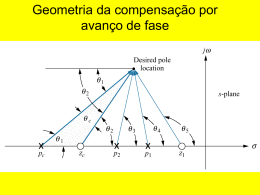

Metodologia de projeto por atraso de fase • Permite melhorar o erro de estado estacionário sem modificar consideravelmente as características de resposta transitória; • Sua principal característica é que ele fornece uma atenuação nas altas frequências o que permite fornecer uma margem de fase adequada ao sistema. Gráficos de resposta de freqüência de um compensador por atraso de fase, Gc(s) = (s + 0,1)/(s + 0,01) Controlador por atraso de fase 1 s 1 T Gc s ; 1 1 s T Controlador por atraso de fase M tg 1 2 2 2 1 4 4 Controlador por atraso de fase Metodologia de projeto por atraso de fase • Determinar K para que o erro de estado estacionário seja estabelecido; • Com o novo ganho se a margem de ganho e margem de fase não estiverem de acordo com os requisitos projetar o controlador atraso de fase: – Encontrar a frequência onde -180º + Margen de Fase requerida acontece (adicionando de 5 a 12 graus na margem de fase para compensar a adição do atraso de fase do controlador); Metodologia de projeto por atraso de fase • Nesta nova frequência para a margem de fase ajustada determinar a atenuação necessária para trazer a curva de módulo para o valor de 0 dB, esta atenuação vale: 20 log • Projetamos a posição do zero do controlador uma década abaixo desta frequência para que o atraso de fase ocorra nas baixas frequências e não afete a margem de fase requerida; 1 T Metodologia de projeto por atraso de fase • Calculado o local do zero podemos determinar o local do pólo: 1 T • E também podemos calcular o ganho do controlador para manter o erro de estado estacionário como desejado EXEMPLO • Para o sistema mostrado abaixo projete um controlador atraso de fase para que o erro de estado estacionário seja melhorado de 10 vezes mantendo-se o percentual de ultrapassagem em 9,5%. 58.210 Gc s ss 36s 100 • O diagrama de bode desta função esta no próximo slide Exemplo • Para atender a exigência de erro de estado estacionário multiplicamos o ganho por 10 e nova função vale: 582.100 Gc s ss 36s 100 • Cujo diagrama de Bode esta no próximo slide Resultado do Controlador 20 log 24 15,85 s 0,978 Gc s 0,0631 s 0,062 36.725s 0,978 G s ss 36s 100s 0,062 Exemplo • Para o sistema abaixo, utilizando a sua resposta em frequência, projete um controlador que reduza em cinco vezes o erro de estado estacionário e mantenha o sistema operando com %U.P.=20%. R(s) + - K s 4 G s ss 5s 8 C(s) Exemplo ln 0,2 ln 0,2 2 M tg 1 2 0,456 2 2 2 1 4 4 48,10 Exemplo • Vemos no gráfico de bode que para a margem de fase desejada o diagrama de módulo vale -40,6 dB logo o ganho deve ser: 20log K 40,6 K 107 107s 428 F .T .M .F . 2 2 s 13s 143,51s 414,06 Exemplo K v lim sG s s 0 107s 4 K v lim s 10,7 s 0 ss 5s 8 K vnovo 5 K v novo ganho 535 Gráfico de Bode com K=535 e com a margem de fase ajustada para 48,1 +10 graus mostrando uma frequência de 6,17rad/s Exemplo atenuaçãonecessária 18dB 20 log 18 7,94 zero controlador 0,62 pólo 0,6 0,078 ganhodo controlador 0,126 67,38s 4 ( s 0,62) F .T .M . A. s s 5s 8( s 0,078)

Baixar