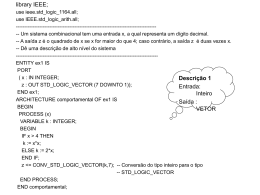

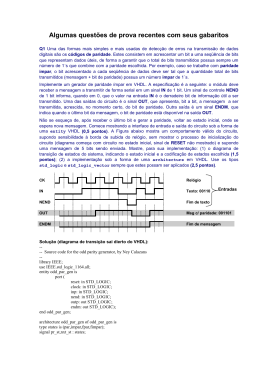

Introdução ao VHDL João M. P. Cardoso Um Contador de 0 a 7 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; architecture Behavioral of count is signal cnt1 : std_logic_vector(2 downto 0); begin process(clk, reset) begin if reset = '1' then entity count is cnt1 <= (others => '0'); Port ( clk : in std_logic; elsifclk'event AND clk = '1' then reset : in std_logic; cnt1 <= cnt1 + 1; cnt : out std_logic_vector(2 downto 0)); end if; end count; end process; cnt <= cnt1; end Behavioral; Simulação Descrição em VHDL de uma bancada de teste Instância o componente Define o valor dos sinais Só serve para simulação! Criação de um ficheiro do tipo Test Bench Waveform Permite a atribuição de valores aos sinais utilizando uma interface gráfica Bancada de Teste LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.numeric_std.ALL; ENTITY testbench IS END testbench; ARCHITECTURE behavior OF testbench IS COMPONENT count PORT( clk : IN std_logic; reset : IN std_logic; cnt : OUT std_logic_vector(2 downto 0) ); END COMPONENT; SIGNAL clk : std_logic; SIGNAL reset : std_logic; SIGNAL cnt : std_logic_vector(2 downto 0); SIGNAL clock : std_logic := '0'; -- for simulation BEGIN uut: count PORT MAP( clk => clk, reset => reset, cnt => cnt ); clock <= not clock after 10 ns; -- T = 20ns clk <= clock; -- *** Test Bench - User Defined Section *** tb : PROCESS BEGIN reset <= '1'; wait for 20 ns; reset <= '0'; wait for 200 ns; --wait; -- will wait forever END PROCESS; -- *** End Test Bench - User Defined Section *** END; ModelSim XE II/Starter 5.7c Janela de ondas do simulador Descodificador de Sete Segmentos architecture Behavioral of seven_seg is begin process(inp_data) begin case inp_data is when "0000" => out_data <= "10000001"; when "0001" => out_data <= "11001111"; entity seven_seg is when "0010" => Port ( inp_data : in std_logic_vector(3 downto 0); out_data <= "10010010"; out_data : out std_logic_vector(7 downto 0)); when "0011" => end seven_seg; out_data <= "10000110"; when "0100" => out_data <= "11001100"; c0 when "0101" => c1 c5 out_data <= "10100100"; c6 when "0110" => c4 c2 out_data <= "10100001"; when "0111" => c3 out_data <= "10001111"; c0 c1 c2 c3 c4 c5 c6 when "1000" => out_data <= "10000000"; when "1001" => Descodificador de out_data <= "10000100"; BCD para 7– when others => segmentos out_data <= "11111111"; end case; A B C D end process; end Behavioral; library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; Exemplo: Máquina de Bebidas Disponibiliza a lata depois de 150 ou mais escudos terem sido depositados Uma única abertura para moedas (50$00 e Reset 100$00) Não dá troco CEM Sensor de Moedas CINQ FSM da máquina de bebidas Clock Abre Mecanismo de Libertar Lata Exemplo: Máquina de Bebidas Tabela e Diagrama de Estados Estado Actual 0$ Reset 0$ 50$ CINQ 50$ CEM 100$ CINQ CEM 100$ CEM + CINQ 150$ [open] 150$ Entrada CEM CINQ 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 – – Próx. Estado 0$ 50$ 100$ – 50$ 100$ 150$ – 100$ 150$ 150$ – 150$ Tabela de estados Simbólica Saída open 0 0 0 – 0 0 0 – 0 0 0 – 1 Exemplo: Máquina de Bebidas fsm1: process(current_state, CEM, CINQ) begin case current_state is when zero => s_open <= '0'; if CINQ = '1' then next_state <= cinquenta; entity fsm is else next_state <= zero; end if; Port ( clk : in std_logic; when cinquenta => reset : in std_logic; s_open <= '0'; CEM : in std_logic; if CINQ = '1' then next_state <= st_cem; CINQ : in std_logic; elsif CEM = '1' then next_state <= cent_cinq; s_open : out std_logic); else next_state <= cinquenta; end if; end fsm; when st_cem => s_open <= '0'; architecture Behavioral of fsm is if CINQ = '1' OR CEM = '1' then next_state <= cent_cinq; type state_type is (zero, cinquenta, st_cem, cent_cinq); else next_state <= st_cem; end if; signal current_state, next_state: state_type; when cent_cinq => begin s_open <= '1'; fsm2: process(reset, clk) next_state <= zero; begin when others => if reset = '1' then s_open <= '0'; current_state <= zero; next_state <= zero; elsif clk'event AND clk='1' then end case; current_state <= next_state; end process; end if; end Behavioral; end process; library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; Exemplo: Máquina de Bebidas Quantos Flip-Flops existem no hardware sintetizado? Modificar as directivas de síntese para utilizar o menor número de FFs possível 4 estados => 2 FFs

Baixar