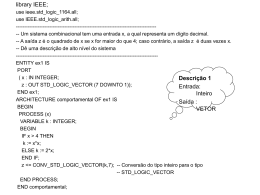

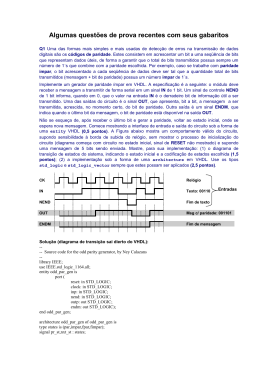

Aula 2 LDH 1 1. Criar uma biblioteca de trabalho. 2. Fazer compilação de ficheiros do projecto. 3. Carregar o projecto e executar simulação. 4. Fazer depuração dos resultados. Biblioteca por omissão é “Work” Aula 2 LDH 2 1. Criar um projecto. 2. Adicionar ficheiros ao projecto. 3. Fazer compilação. 4. Executar simulação. 5. Fazer depuração. Aula 2 LDH 3 entity MyCounter is Port ( reset clk1Hz clock_enable direction BCD end MyCounter; : in STD_LOGIC; : in STD_LOGIC; : in STD_LOGIC; : in STD_LOGIC; : out STD_LOGIC_VECTOR (3 downto 0)); Aula 2 LDH Counter library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; 4 architecture Behavioral of MyCounter is signal count : std_logic_vector (3 downto 0); begin process (clk1Hz) begin if rising_edge(clk1Hz) then if reset='1' then count <= (others => '0'); elsif clock_enable='1' then if direction='1' then count <= count + 1; else count <= count - 1; end if; end if; end if; end process; BCD <= count; end Behavioral; Aula 2 LDH 5 Fluxo de projecto: 1. Criar uma pasta e copiar o código fonte (ver 2 slides anteriores). Vamos criar, por exemplo, a pasta “aula2” e copiar o código. 2. Executar ModelSim. Double click Alterar a pasta para “aula2” utilizando File → Change Directory. 3. Fechar janela “Welcome”. 4. Criar uma biblioteca do projecto: File → New → Library. Se existir um problema pode remover a biblioteca “work”anterior As duas linhas seguintes são iguais às operações de menu consideradas acima: Aula 2 LDH vlib work vmap work work 6 Finalmente a pasta “aula2” vai conter: 5. Fazer compilação: Compile → Compile. Aula 2 LDH 7 Permite verificar o código VHDL utilizando uma sequência predefinida de sinais de entrada. VHDL test bench é composto por uma arquitectura que inclui instâncias de componentes que devem ser verificados, e processos que geram sequências de valores de sinais ligados aos componentes. A arquitectura pode também incluir processos para testar saídas de componentes. Aula 2 LDH 8 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity test_bench is port ( BCD : buffer std_logic_vector(3 downto 0)); end; Aula 2 LDH 9 architecture test_counter of test_bench is signal reset signal clk1Hz signal clock_enable signal direction component MyCounter is Port ( reset clk1Hz clock_enable direction BCD end component; : std_logic := '1'; : std_logic := '0'; : std_logic := '0'; : std_logic := '0'; : in std_logic; : in std_logic; : in std_logic; : in std_logic; : out std_logic_vector (3 downto 0)); begin Aula 2 LDH 10 Count_instance : MyCounter port map (reset, clk1Hz, clock_enable, direction, BCD); clock : process begin wait for 30 ps; clk1Hz <= not clk1Hz; end process clock; stimulus : process begin wait for 50 ps; clock_enable <= '1'; wait for 60 ps; reset <= '0'; wait for 500 ps; direction <= '1'; wait; end process stimulus; signal reset : std_logic := '1'; signal clk1Hz : std_logic := '0'; signal clock_enable : std_logic := '0'; signal direction : std_logic := '0'; force reset 1 0, 0 60 force clk 0 0, 1 30 -r 60 force clock_enable 0 0, 1 50 force direction 0 0, 1 500 end architecture test_counter; Aula 2 LDH 11 Pauta “aula2” 5. Fazer compilação: Compile → Compile. Aula 2 LDH 12 6. Ver os resultados da compilação. double click Aula 2 LDH 13 A estrutura hierárquica do projecto Ficheiros do projecto Aula 2 LDH 14 7. Ver objectos: View → Objects. Aula 2 LDH 15 Os objectos incluem: sinais (signals), ligações (nets), registos (registers), constantes (constants), variáveis (variables) não declaradas em processos, genéricos (generics) e parâmetros (parameters) 8. Abrir diagramas de tempo: View → wave. 9. Adicionar sinais: View → wave. Right click Right click Aula 2 LDH 16 10. Executar simulação: Run 1000. 11. Verificar os resultados. Aula 2 LDH 17 Tarefa 1: Fazer simulação de um contador com código VHDL seguinte: process (<clock>) begin if <clock>='1' and <clock>'event then if <reset>='0' then <count> <= (others => '0'); elsif <clock_enable>='1' then if <load_enable>='1' then <count> <= <input>; else if <count_direction>='1' then <count> <= <count> + 1; else <count> <= <count> - 1; end if; end if; end if; end if; end process; Mostrar resultados da simulação Aula 2 LDH 18 Tarefa 2: Fazer simulação de um registo de deslocamento com código VHDL seguinte: process (<clock>,<reset>) begin if <reset> ='1' then <tmp_sig> <= (others => '0'); elsif <load_enable> = '1' then <tmp_sig> <= <input>; elsif <clock>'event and <clock>='1' then if <clock_enable> = '1' then <tmp_sig> <= <tmp_sig>(<width>-2 downto 0) & <input>; end if; end if; end process; <output> <= <tmp_sig>(<width>-1); Aula 2 LDH Mostrar os resultados da simulação 19 Tarefa 3: Fazer simulação de um circuito com código VHDL seguinte: process (<input1>, <input2>) begin if <add_sub> = '1' then <addsub_output> <= <input1> + <input2>; else <addsub_output> <= <input1> - <input2>; end if; end process; Aula 2 LDH Mostrar os resultados da simulação 20 Tarefa 4 (mais avançada): Fazer simulação de uma máquina de estados finitos: y1,y2 a1 y3,y4 1 a2 x1 not x1 and x2 Mostrar os resultados da simulação x4 y1,y3 y2 a4 not x4 x3 a3 Aula 2 LDH 21 -- This is a sample state-machine using enumerated types. -- This will allow the synthesis tool to select the appropriate -- encoding style and will make the code more readable. --Insert the following in the architecture before the begin keyword --Use descriptive names for the states, like st1_reset, st2_search type state_type is (st1_<name_state>, st2_<name_state>, ...); signal state, next_state : state_type; --Declare internal signals for all outputs of the state-machine signal <output>_i : std_logic; -- example output signal --other outputs NEXT_STATE_DECODE: process (state, <input1>, <input2>, ...) begin --declare default state for next_state to avoid latches next_state <= state; --default is to stay in current state --insert statements to decode next_state --below is a simple example case (state) is when st1_<name> => if <input_1> = '1' then next_state <= st2_<name>; end if; when st2_<name> => if <input_2> = '1' then next_state <= st3_<name>; end if; when st3_<name> => next_state <= st1_<name>; when others => next_state <= st1_<name>; end case; end process; --Insert the following in the architecture after the begin keyword SYNC_PROC: process (<clock>) begin if (<clock>'event and <clock> = '1') then if (<reset> = '1') then state <= st1_<name_state>; <output> <= '0'; else state <= next_state; <output> <= <output>_i; -- assign other outputs to internal signals end if; end if; end process; --MOORE State-Machine - Outputs based on state only OUTPUT_DECODE: process (state) begin --insert statements to decode internal output signals --below is simple example if state = st3_<name> then <output>_i <= '1'; else <output>_i <= '0'; end if; end process; Aula 2 LDH 22 1. Fazer simulação em ModelSim de: • circuitos combinatórios (multiplexadores, descodificadores, comparadores, etc.). • circuitos sequenciais (contadores, registos de deslocamento, acumuladores, etc.). • circuitos sequenciais definidos por diagramas de tempo (i.e. máquinas de estados finitos). 2. Criar projectos em ModelSim que são compostos por vários circuitos combinatórios e sequenciais. Aula 2 LDH 23

Baixar