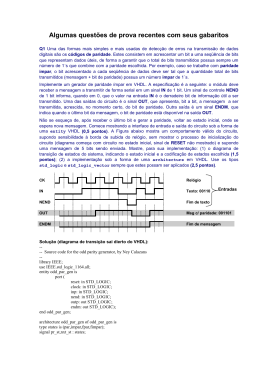

library IEEE; use ieee.std_logic_1164.all; use IEEE.std_logic_arith.all; ------------------------------------------------------------------------------------- Um sistema combinacional tem uma entrada x, a qual representa um dígito decimal. -- A saída z é o quadrado de x se x for maior do que 4; caso contrário, a saída z é duas vezes x. -- Dê uma descrição de alto nível do sistema ------------------------------------------------------------------------------------ENTITY ex1 IS PORT ( x : IN INTEGER; Descrição 1 z : OUT STD_LOGIC_VECTOR (7 DOWNTO 1)); Entrada: END ex1; Inteiro ARCHITECTURE comportamental OF ex1 IS Saída : BEGIN VETOR PROCESS (x) VARIABLE k : INTEGER; BEGIN IF x > 4 THEN k := x*x; ELSE k := 2*x; END IF; z <= CONV_STD_LOGIC_VECTOR(k,7); -- Conversão do tipo inteiro para o tipo -- STD_LOGIC_VECTOR END PROCESS; END comportamental; library IEEE; use ieee.std_logic_1164.all; use IEEE.std_logic_arith.all; ------------------------------------------------------------------------------------- Um sistema combinacional tem uma entrada x, a qual representa um dígito decimal. -- A saída z é o quadrado de x se x for maior do que 4; caso contrário, a saída z é duas vezes x. -- Dê uma descrição de alto nível do sistema ------------------------------------------------------------------------------------ENTITY ex1 IS PORT ( x : IN INTEGER; Descrição 1 z : OUT STD_LOGIC_VECTOR (7 DOWNTO 1)); Entrada: END ex1; Inteiro ARCHITECTURE comportamental OF ex1 IS Saída : BEGIN VETOR PROCESS (x) VARIABLE k : INTEGER; BEGIN IF x > 4 THEN k := x*x; ELSE k := 2*x; END IF; z <= CONV_STD_LOGIC_VECTOR(k,7); -- Conversão do tipo inteiro para o tipo -- STD_LOGIC_VECTOR END PROCESS; END comportamental; Simulação Simulação 12.8 ns (tap) tap -> tempo de atraso de propagação Simulação 21.0ns (tap) tap -> tempo de atraso de propagação ** DEVICE SUMMARY ** Chip/ POF Device Input Output Bidir Memory Pins Pins Pins Bits % ex1 EPF10K10LC84-3 32 7 0 0 Memory Utilized LCs LCs % Utilized 0% 43 7 % library IEEE; use ieee.std_logic_1164.all; use IEEE.std_logic_arith.all; ENTITY ex1_1 IS PORT ( x : IN INTEGER RANGE 0 TO 9; z : OUT STD_LOGIC_VECTOR (7 DOWNTO 1)); END ex1_1; ARCHITECTURE comportamental OF ex1_1 IS BEGIN PROCESS (x) VARIABLE k : INTEGER; BEGIN IF x > 4 THEN k := x*x; ELSE k := 2*x; END IF; z <= CONV_STD_LOGIC_VECTOR(k,7); END PROCESS; END comportamental; Descrição 2 Entrada: Inteiro de 0 a 9 Saída : VETOR ** DEVICE SUMMARY ** Chip/ POF Device ex1 EPF10K10LC84-3 Input Output Bidir Memory Pins Pins Pins Bits % 4 7 0 0 Memory Utilized LCs 0% 7 LCs % Utilized 1 % library IEEE; use ieee.std_logic_1164.all; use IEEE.std_logic_arith.all; ENTITY ex1_2 IS PORT ( x : IN INTEGER RANGE 0 TO 9; z : OUT INTEGER RANGE 0 TO 81); END ex1_2; ARCHITECTURE comportamental OF ex1_2 IS BEGIN PROCESS (x) VARIABLE k : INTEGER; BEGIN IF x > 4 THEN k := x*x; ELSE k := 2*x; END IF; z <= K; END PROCESS; END comportamental; Descrição 3 Entrada: Inteiro de 0 a 9 Saída : Inteiro de 0 a 81 ** DEVICE SUMMARY ** Chip/ POF Device Input Output Bidir Memory Pins Pins Pins Bits % ex1_2 EPF10K10LC84-3 4 7 0 0 Memory Utilized LCs 0% LCs % Utilized 7 1 %

Baixar