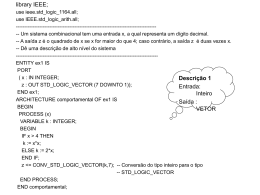

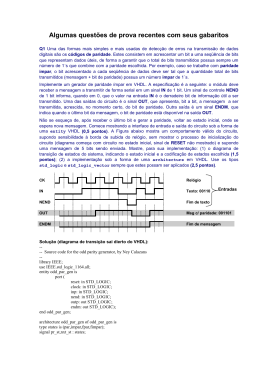

Introdução à Programação da FPGA João M. P. Cardoso Programação da FPGA Placa de Desenvolvimento XSA-50 Board Placa de Desenvolvimento Frequência: 100 MHz Pode ser dividida por 1, 2, ... 2052 utilizando a ferramenta gxssetclk 1º Exemplo Descodificador de 7segmentos 1º Exemplo Criar um novo projecto Device Family: Spartan2 Device: XC2S50 Package property: tq144 speed grade: -5. 1º Exemplo Depois do circuito ser sintetizado, o P&R ter sido feito, podemos verificar que a ferramenta atribuiu aos sinais de entrada/saída da entidade pinos de I/O architecture Behavioral of seven_seg is begin process(inp_data) begin case inp_data is when "0000" => out_data <= "11110111"; when "0001" => out_data <= "10010010"; when "0010" => out_data <= "11011101"; when "0011" => out_data <= "11011011"; when "0100" => out_data <= "10111010"; when "0101" => out_data <= "11101011"; when "0110" => out_data <= "11101111"; when "0111" => out_data <= "11010010"; when "1000" => out_data <= "11111111"; when "1001" => out_data <= "11111011"; when others => out_data <= “01111111"; end case; end process; end Behavioral; 1º Exemplo Falta por isso indicarmos os pinos correctos da FPGA que ligam ao display de 7segmentos e aos 4 interruptores switchs FPGA pin DIPSW1 P54 DIPSW2 P64 DIPSW3 P63 DIPSW4 P56 LED input FPGA pin S0 P67 S1 P39 S2 P62 input FPGA pin S3 P60 Botão SW2 P93 S4 P46 CCLK P88 S5 P57 S6 P49 DP P44 1º Exemplo Atribuição de sinais aos pinos do FPGA Especificação em VHDL Definição de um ficheiro de restrições (User-constraint file) Especificação em VHDL attribute loc : string; Attribute loc of clk : signal is “P88” Attribute loc of reset: signal is “P93” ... Ficheiro de restrições net reset loc=p93; library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity seven_seg is Port ( inp_data : in std_logic_vector(3 downto 0); out_data : out std_logic_vector(7 downto 0)); end seven_seg; architecture Behavioral of seven_seg is attribute loc : string; attribute loc of inp_data : signal is "P54, P64, P63, P56"; attribute loc of out_data : signal is " P44, P49,P57, P46, P60, P62, P39, P67"; begin … end Behavioral; 1º Exemplo Para programarmos a FPGA na placa utilizamos a ferramenta: gxsload O ficheiro da configuração (bitstream) que deve ser carregado tem extensão .bit Descodificador de Sete Segmentos begin library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity seven_seg is Port ( inp_data : in std_logic_vector(3 downto 0); out_data : out std_logic_vector(7 downto 0)); end seven_seg; architecture Behavioral of seven_seg is attribute loc : string; attribute loc of inp_data : signal is "P54, P64, P63, P56"; attribute loc of out_data : signal is " P44, P49,P57, P46, P60, P62, P39, P67"; process(inp_data) begin case inp_data is when "0000" => out_data <= "11110111"; when "0001" => out_data <= "10010010"; when "0010" => out_data <= "11011101"; when "0011" => out_data <= "11011011"; when "0100" => out_data <= "10111010"; when "0101" => out_data <= "11101011"; when "0110" => out_data <= "11101111"; when "0111" => out_data <= "11010010"; when "1000" => out_data <= "11111111"; when "1001" => out_data <= "11111011"; when others => out_data <= “01111111"; end case; end process; end Behavioral;

Baixar