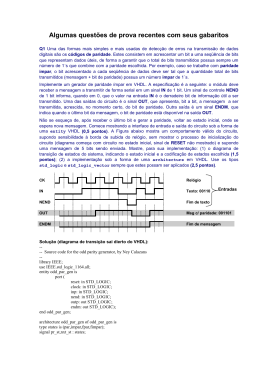

Introdução a VHDL Monitoria de Digitais VHDL: • VHDL (VHSIC – Very High Speed Integrated Circuit Hardware Description Language) é uma linguagem de descrição de hardware muito importante, pois é amplamente utilizada no desenvolvimento de sistemas atuais. VHDL: VHDL foi desenvolvido para facilitar a descrição de circuitos complexos, sem precisar da utilização de vários manuais específicos para cada parte de um projeto. Ou seja, é possível descrever um circuito digital de forma estrutural ou comportamental. Termos: Entity: Responsável pela descrição das portas de entrada e saída dos circuitos, que servem para formalizar uma comunicação com outros circuitos. Cada entidade deve possuir uma ou mais arquiteturas. Architecture: Responsável por descrever o comportamento do circuito, ou seja, o algoritmo utilizado para desempenhar sua funcionalidade. Em VHDL, existem três tipos de arquiteturas: • Estrutural • Comportamental DataFlow • Comportamental processo Architecture - Estrutural: sinais: Interconexões entre componentes Componentes: Devem ter sido especificado anteriormente (Hierarquia) Uso dos componentes: Podem ser usados mais de uma vez (Reusabilidade) Architecture - Dataflow: Data Flow (eq. booleanas): Concorrência Architecture - Dataflow: O que é melhor utilizar expressões concorrentes ou sequências? Depende do que você quer implementar... a <= b; b <= a; a := b; b := a; O primeiro faz com que os valores de a e b sejam permutados e o segundo faz com que a e b assumam o valor anterior de b. Architecture - Processo: Algoritmo(Processo): Seqüencial Lista de Sensibilidade: Sinais de entrada Região declarativa: Região entre o fim da lista de sensibilidade e a palavra chave begin. Usada para declarar variáveis ou constantes dentro do processo. Campo de atribuições: Campo entre a chave begin e end ALG; Configuration: Uma configuração é usada para ligar a arquitetura de um componente a sua entidade. Uma configuração permite a seleção de diversas arquiteturas em diferentes níveis de hierarquia. Package: As bibliotecas são coleções de tipos de dados e subprogramas comumente utilizados nos projetos, como uma caixa de ferramentas. Package: Biblioteca a ser utilizada em Digitais: LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; Tipos: VHDL possui um conjunto de tipos definidos que se caracterizam pelo conjunto de valores que podem assumir e o conjunto de operações que sobre eles podem ser executadas. Objetos “CONSTANT”, “VARIABLE” e “SINAL” devem ser declarados como de um tipo definido para que possam ser identificados seus possíveis valores e quais operações podem ser executadas. Tipos: BIT: assume valores de 0 ou 1 SIGNAL valor: bit; BOOLEAN: usado em teste de decisão, assume os valores true ou false. SIGNAL teste: boolean; INTEGER: assume um valor inteiro entre 2.147.483.647 e +2.147.483.67. SINGNAL valor: integer range 0 to 10; • REAL:representa um número de ponto flutuante. Tipos: • STD_LOGIC: podem assumir dentre outros valores os seguintes: não inicializado(U), alta impedância(Z), nível lógico alto(1) e nível lógico baixo(0). SIGNAL valor: std_logic; • Vetores: são conjuntos de sinais perviamente definidos, exemplos: SIGNAL vetor: std_logic_vector(10 DOWNTO 0); SIGNAL vetor: std_logic_vector(0 TO 10); SIGNAL vetor: bit_vector(10 DOWNTO 0); SIGNAL vetor: bit_vector(0 TO 10); Operadores: Lógicos: and, or, xor, not, nand valor := a xor b; Relacionais: =, /=,<,>,<=,>= IF (a /= b) THEN; A <= B;obs.:cuidado com o operador <=, pois ele também é um operador de atribuição. Deslocamento: sll, srl, sla, rol, ror sinal_a <= x ror 3; z <= x sll 1; Operadores: Adição: +, -, & valor := a + b; Valor := “00” & “11”; (concatenação: “0011”) Sinal: +, A <= -B; Multiplicação e divisão: *, /, mod, rem a_div_b := a / b; Diversos: **, abs, not sinal_abs <= abs( -3); valor := b**2; Decisões: If then else: IF (condição) THEN código; Else codigo; END IF; Case When: Case estados is when estado1 => código; when estado2 => código; when others => código; END CASE; Decisões: SIGNAL sinalA: STD_LOGIC_VECTOR(1 DOWNTO 0); CASE sinalA IS WHEN “00” => código; WHEN “01” => código; WHEN OTHERS => pode ter ou não operações; END CASE; With select: WITH expressao_escolha SELECT sinal <= expressao_a WHEN condicao1, expressao_b WHEN condicao2, expressao_c WHEN condicao3 | condicao4, expressao_d WHEN OTHERS; Referências: • VHDL Programming by Example, Douglas L. Perry, 4ª edition. • Aula de VHDL auxiliar da cadeira de Infra de Hardware. • Aula 1 de VHDL antiga • Aula 2 de VHDL antiga

Baixar