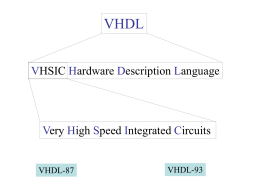

Linguagens de Descrição de Hardware VHDL Foco: Síntese Lógica Integração Hardware-Software João M. P. Cardoso Email: [email protected] URL: http://w3.ualg.pt/~jmcardo 2005 1 Modelação de Sistemas Digitais Razões para modelar Objectivo 2 Especificação dos requisitos documentação Teste utilizando simulação Verificação formal síntese Processo de desenho mais fiável, com custo e tempo mínimos Fuga aos erros de desenho! Modelação de Sistemas Digitais Linguagens de Programação de Hardware VHDL (VHSIC Hardware Description Language) • VHSIC: Very High Speed Integrated Circuit 3 Verilog Domínios e Níveis de Modelação Functional Structural high level of abstraction low level of abstraction Geometric 4 “Y-chart” due to Gajski & Kahn Domains and Levels of Modeling Functional Structural Algorithm (behavioral) Register-Transfer Language Boolean Equation Differential Equation Geometric 5 “Y-chart” due to Gajski & Kahn Domains and Levels of Modeling Functional Structural Processor-Memory Switch Register-Transfer Gate Transistor Geometric 6 “Y-chart” due to Gajski & Kahn Domains and Levels of Modeling Functional Structural Polygons Sticks Standard Cells Floor Plan Geometric 7 “Y-chart” due to Gajski & Kahn Conceitos básicos de VHDL Interfaces Comportamento (behavior) Estrutura Conjuntos de teste (Test Benchs) Análise, elaboração, simulação Síntese 8 Interfaces de Modelação Declaração da Entity Descreve as entradas/saídas de cada módulo entity name port names port mode (direction) entity reg4 is port ( d0, d1, d2, d3, en, clk : in bit; q0, q1, q2, q3 : out bit ); end reg4; reserved words 9 port type punctuation Modelação do Behavior Corpo da Architecture Descreve uma implementação da entity Podem ser várias por entity Arquitectura Behavioral Descreve o algoritmo realizado pelo módulo contém • • • • 10 process statements, cada contém sequential statements, incluindo signal assignment statements e wait statements Exemplo de Behavior 11 architecture behav of reg4 is begin storage : process variable stored_d0, stored_d1, stored_d2, stored_d3 : bit; begin if en = '1' and clk = '1' then stored_d0 := d0; stored_d1 := d1; stored_d2 := d2; stored_d3 := d3; end if; q0 <= stored_d0 after 5 ns; q1 <= stored_d1 after 5 ns; q2 <= stored_d2 after 5 ns; q3 <= stored_d3 after 5 ns; wait on d0, d1, d2, d3, en, clk; end process; end behav; Modelação de Estruturas Structural architecture Implementa o módulo como uma composição de sub-sistemas contém • signal declarations, para interligações internas • Portos da entity são também tratados como sinais • component instances • Instâncias de pares entity/architecture previamente declarados • port maps em component instances • Conecta sinais a portos dos componentes 12 Exemplo de Estrutura bit0 d_latch d q d0 q0 clk bit1 d_latch d q d1 q1 clk bit2 d_latch d q d2 q2 clk bit3 d_latch d q d3 en clk 13 gate and2 a y b clk int_clk q3 Exemplo de Estrutura Declarar primeiro entidades e arquitecturas para o D-latch e and-gate entity d_latch is port ( d, clk : in bit; q : out bit ); end d_latch; architecture basic of d_latch is begin latch_behavior : process (clk, d) begin if clk = ‘1’ then q <= d after 2 ns; end if; end process; end basic; 14 entity and2 is port ( a, b : in bit; y : out bit ); end and2; architecture basic of and2 is begin and2_behavior : process (a, b) begin y <= a and b after 2 ns; end process; end basic; Exemplo de Estrutura Declarar os componentes correspondentes no corpo da arquitectura do registo architecture struct of reg4 is component d_latch port ( d, clk : in bit; q : out bit ); end component; component and2 port ( a, b : in bit; y : out bit ); end component; signal int_clk : bit; ... 15 Exemplo de Estrutura 16 Utilizá-los para implementar o registo ... begin bit0 : d_latch port map ( d0, int_clk, q0 ); bit1 : d_latch port map ( d1, int_clk, q1 ); bit2 : d_latch port map ( d2, int_clk, q2 ); bit3 : d_latch port map ( d3, int_clk, q3 ); gate : and2 port map ( en, clk, int_clk ); end struct; Exemplo de Estrutura Configurar os modelos: necessário quando temos mais do que um modelo para cada entidade configuration basic_level of reg4 is for struct for all : d_latch use entity work.d_latch(basic); end for; for all : and2 use entity work.and2(basic) end for; end for; end basic_level; 17 Mistura de comportamento e estrutura Uma arquitectura pode ser descrita com comportamentos e estruturas Exemplo: modelo register-transfer-level (RTL) 18 Instruções process e instâncias de componentes Processos podem ler e atribuir sinais Data-path é descrito estruturalmente Unidade de controlo descrita comportamentalmente Exemplo com mistura multiplier multiplicand shift_reg control_ section shift_ adder reg product 19 Exemplo com mistura entity multiplier is port ( clk, reset : in bit; multiplicand, multiplier : in integer; product : out integer ); end multiplier; architecture mixed of mulitplier is -- falta declaração de componentes signal partial_product, full_product : integer; signal arith_control, result_en, mult_bit, mult_load : bit; begin arith_unit : shift_adder port map ( addend => multiplicand, augend => full_product, sum => partial_product, add_control => arith_control ); result : reg port map ( d => partial_product, q => full_product, en => result_en, reset => reset ); 20 ... Exemplo com mistura … multiplier_sr : shift_reg port map ( d => multiplier, q => mult_bit, load => mult_load, clk => clk ); product <= full_product; control_section : process -- variable declarations for control_section -- … begin -- sequential statements to assign values to control signals -- … wait on clk, reset; end process; end mixed; 21 Bancada de teste Testar um desenho por simulação Utilizar um modelo de test bench Um corpo de arquitectura que inclui uma instância do desenho a testar Aplicar sequências de valores de teste às entradas Monitorizar valores em sinais de saída • Utilizando o simulador • Ou com um processo que verifica a correcta operacionalidade 22 Exemplo de bancada de teste architecture test_reg4 of test_bench is entity test_bench is end test_bench; 23 -- falta declaração do componente a testar: reg4 signal d0, d1, d2, d3, en, clk, q0, q1, q2, q3 : bit; begin dut : reg4 port map ( d0, d1, d2, d3, en, clk, q0, q1, q2, q3 ); stimulus : process begin d0 <= ’1’; d1 <= ’1’; d2 <= ’1’; d3 <= ’1’; wait for 20 ns; en <= ’0’; clk <= ’0’; wait for 20 ns; en <= ’1’; wait for 20 ns; clk <= ’1’; wait for 20 ns; d0 <= ’0’; d1 <= ’0’; d2 <= ’0’; d3 <= ’0’; wait for 20 ns; en <= ’0’; wait for 20 ns; … wait; end process; end test_reg4; Teste de regressão Testar se um refinamento do desenho está correcto A bancada de teste inclui duas instâncias do desenho em teste 24 se um modelo estrutural de mais baixo nível faz o mesmo que um modelo comportamental Comportamental e estrutural de baixo-nível Simula ambos com as mesmas entradas Verifica igualdade dos resultados Necessita de ter em conta diferenças temporais Exemplo de teste de regressão architecture regression of test_bench is 25 -- falta declaração do componente a testar signal d0, d1, d2, d3, en, clk : bit; signal q0a, q1a, q2a, q3a, q0b, q1b, q2b, q3b : bit; begin dut_a : entity reg4(struct) port map ( d0, d1, d2, d3, en, clk, q0a, q1a, q2a, q3a ); dut_b : entity reg4(behav) port map ( d0, d1, d2, d3, en, clk, q0b, q1b, q2b, q3b ); stimulus : process begin d0 <= ’1’; d1 <= ’1’; d2 <= ’1’; d3 <= ’1’; wait for 20 ns; en <= ’0’; clk <= ’0’; wait for 20 ns; en <= ’1’; wait for 20 ns; clk <= ’1’; wait for 20 ns; … wait; end process; Exemplo de teste de regressão … verify : process begin wait for 10 ns; assert q0a = q0b and q1a = q1b and q2a = q2b and q3a = q3b report ”implementations have different outputs” severity error; wait on d0, d1, d2, d3, en, clk; end process; end regression; 26 Processamento do Desenho Análise Elaboração Simulação Síntese 27 Análise 28 Verifica sintaxe e semântica sintaxe: gramática da linguagem semântica: o sentido do modelo Analisa cada unidade de desenho em separado Declaração da entity Corpo da architecture … Preferível unidades de desenho em ficheiros separados Unidades de desenho analisadas são colocadas numa biblioteca Numa forma interna de implementação dependente A biblioteca corrente é designada por work Elaboração “Flattening” da hierarquia do desenho Cria portos Cria sinais e processos no corpo da arquitectura Para cada instância de um componente, copia a entity e a architecture instanciada Repete recursivamente • Corpos de architecture unicamente comportamentais Resultado final da elaboração 29 Colecção planar de nets de sinais e processos Exemplo Elaborado bit0 d_latch d q reg4(struct) d0 q0 clk bit1 d_latch d q d1 q1 clk bit2 d_latch d q d2 q2 clk bit3 d_latch d q d3 en clk 30 gate and2 a y b clk int_clk q3 Exemplo Elaborado bit0 d_latch(basic) d q reg4(struct) d0 q0 clk bit1 d_latch(basic) d q d1 q1 clk bit2 d_latch(basic) d q d2 q2 clk bit3 d_latch(basic) d q d3 en clk 31 gate and2(basic) a y b q3 clk int_clk process with variables and statements Simulação Execução dos processos no modelo elaborado Simulação de eventos discretos Tempo avança em passos discretos Quando os sinais mudam de valor - eventos Um processo é sensível a eventos nos sinais de entrada Especificados em instruções wait ou na lista de sensibilidades do processo Resume e escalona novos valores nos sinais de saída • Escalona transacções • Evento num sinal se um novo valor é diferente do valor antigo 32 Síntese Traduz desenho RTL em netlist ao nível da porta lógica Restrições no estilo de código para o modelo RTL Dependente da ferramenta de síntese utilizada 33 Simulação versus Síntese Todos os desenhos sintetizáveis podem ser simulados Nem todos os desenhos simuláveis podem ser sintetizáveis dout <= din after 10 ns; Sintetizável? 34 Metodologia de desenho básica Requirements RTL Model Simulate Synthesize Gate-level Model ASIC or FPGA 35 Simulate Place & Route Timing Model Simulate Test Bench VHDL Detalhes sobre a linguagem 36 Bibliotecas e Pacotes Bibliotecas Fornecem um conjunto de desenhos, componentes, e funções Pacotes (packages) Fornecem uma colecção de tipos de dados e sub-programas utilizados num desenho library IEEE; use IEEE.STD_LOGIC_1164.ALL; 37 Ports 38 Nomes Letras, dígitos, e/ou underscores Começa sempre com uma letra Não é case-sensitive Escolha de direcções de ports In: port de entrada Out: port de saída Inout: port bidireccional Tipos de sinal do port (sugestões): STD_LOGIC STD_LOGIC_VECTOR(<max> DOWNTO/TO <min>) Signals Representam fios e elementos de armazenamento num desenho VHDL Só podem ser declarados dentro de architecture São associados com um certo tipo de dados VHDL é uma linguagem fortemente tipificada 39 Apenas é suportada conversão de tipos explicita Representações Signal Em termos físicos os fios não podem ser modelados com exactidão utilizando a representação binária São necessários outros valores além do ‘0’ e do ‘1’ para representar o estado de um fio 40 Representações de lógica multi-valor MVL (Multi-Valued Logic) MVL-4 • • • • MVL-9 • • • • • • • • • 41 Forçar ‘1’: ‘1’ Forçar ‘0’: ‘0’ Forçar desconhecido: ‘X’ Forçar alta impedância: ‘Z’ Forçar ‘1’: ‘1’ Forçar ‘0’: ‘0’ Forçar desconhecido: ‘X’ Forçar alta impedância: ‘Z’ Não interessa o valor: ‘-’ Não inicializado: ‘U’ 1 fraco: ‘H’ 0 fraco: ‘L’ Desconhecido fraco: ‘W’ Tipos de Dados prédefinidos Os tipos de dados pré-definidos funcionam bem para simulação mas não são ideais para síntese Exemplos de Tipos de dados 42 Bit (1 bit) bit_vector (vector de bits) Integer Real Outros tipos de dados podem ser definidos pelo utilizador Tipos de Dados prédefinidos 43 Time: hr, min, sec, ms, us, ns, ps, fs STRING(positivo): array de chars CHARACTER: 7-bit ASCII BIT_VECTOR(natural): Array of bits BIT: ‘0’, ‘1’ REAL: Floating-point POSITIVE: inteiros > 0 NATURAL: inteiros >= 0 INTEGER: 32 ou 64 bits BOOLEAN: True ou false STD_LOGIC_1164 Pacote standard que implementa um conjunto de tipos de dados Utiliza MVL-9 IEEE recomenda a utilização dos tipos de dados STD_LOGIC e STD_LOGIC_VECTOR utilização recomendada pela maioria das ferramentas de síntese 44 Operadores Lógicos VHDL suporta 45 AND OR XOR XNOR NOT NAND NOR VHDL suporta a sobrecarga dos operadores existentes e a criação de novos Outros operadores Relacionais 46 = (igualdade) /= (diferente) < (menor que) > (maior que) <= (menor ou igual) >= (maior ou igual) Deslocamento sll Srl Sla Sra Rol ror Aritméticos + (adição) - (subtracção) * (multiplicação) / (divisão) mod Rem outros & (concatenação) abs (valor absoluto) ** (potência) Instruções de atribuição 47 X: std_logic Y: std_logic_vector(7 downto 0) Z: integer; Instruções de atribuição de sinais concorrentes X <= Y AND z; A <= B OR c; (X e A são produzidos concorrentemente) Atribuição de constantes a sinais X <= ‘0’; X <= ‘1’; X <= ‘Z’; Y <= “00111010”; -- atribui 0x3A a Y Y <= X”3A”; -- atribui 0x3A a Y Y <= X”3” & X”A”; -- atribui 0x3A a Y Z <= 9; -- atribui 9 a Z Y <= (others => ‘0’); -- atribui todos os bits a ‘0’ Constantes Exemplos: constant a : integer := 5; constant b: std_logic := ‘1’; constant c: std_logic_vector(3 downto 0) := “0000”; constant d: std_logic_vector(0 to 3) := “0000”; constant delay : time := 5 ns; 48 Arrays Uma ou mais dimensões array (0 to 7) of integer range 0 to 15; type array1 of char is array(1 to 4) of character; type matrix is array(1 to 4, 1 to 7) of integer; 49 Definição de novos tipos de dados type type gap is range 10 to 100; type word is range -32768 to 32767; type myInteger is range -2147483647 to 2147483647 subtype subtype G is INTEGER range 0 to 9; subtype word is bit_vector(31 downto 0); subtype myNatural is myInteger range 0 to myInteger'HIGH; 50 Definição de novos tipos de dados 51 Enumerados type color is (white, black, blue, red, yellow); signal my_color: color; Type instr is (load, store, add, mult); type BOOLEAN is (FALSE, TRUE); type BIT is ('0', '1'); Atributos pré-definidos ‘event ‘length 52 Para identificar um evento (mudança de estado) num sinal Exemplo: clock’event Exemplo: bus’length ‘range (esquerda downto/to direita) ‘high (valor do limite superior) ‘low (valor do limite inferior) ... Comentários Cada linha de comentários é precedida por ”--” Exemplo • -- exemplo de um comentário 53 Contador de 0 a 7 architecture Behavioral of count is signal cnt1 : std_logic_vector(2 downto 0); begin process(clk, reset) library IEEE; begin use IEEE.STD_LOGIC_1164.ALL; if reset = '1' then use IEEE.STD_LOGIC_ARITH.ALL; cnt1 <= (others => '0'); use IEEE.STD_LOGIC_UNSIGNED.ALL; elsif clk'event AND clk = '1' then cnt1 <= cnt1 + 1; entity count is end if; Port ( clk : in std_logic; end process; reset : in std_logic; cnt <= cnt1; cnt : out std_logic_vector(2 downto 0)); end Behavioral; end count; • Com std_logic_vector 54 Contador de 0 a 7 • Com integer library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity count is Port ( clk : in std_logic; reset : in std_logic; cnt : out integer range 0 to 7); end count; 55 architecture Behavioral of count is signal cnt1 : integer range 0 to 7; begin process(clk, reset) begin if reset = '1' then cnt1 <= 0; elsif clk'event AND clk = '1' then cnt1 <= cnt1 + 1; end if; end process; cnt <= cnt1; end Behavioral; Bancada de teste Declaração de um sinal periódico: exemplo do relógio LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.numeric_std.ALL; ENTITY testbench IS END testbench; ARCHITECTURE behavior OF testbench IS COMPONENT count PORT(clk : IN std_logic; reset : IN std_logic; cnt : OUT std_logic_vector(2 downto 0) ); END COMPONENT; SIGNAL clk : std_logic; SIGNAL reset : std_logic; SIGNAL cnt : std_logic_vector(2 downto 0); SIGNAL clock : std_logic := '0'; -- for simulation 56 BEGIN uut: count PORT MAP( clk => clk, reset => reset, cnt => cnt ); clock <= not clock after 10 ns; -- T = 20ns clk <= clock; -- *** Test Bench - User Defined Section *** tb : PROCESS BEGIN reset <= '1'; wait for 20 ns; reset <= '0'; wait for 200 ns; --wait; -- will wait forever END PROCESS; -- *** End Test Bench - User Defined Section *** END; Processos: process Secções onde a execução é sequencial Process(........) Lista de sensibilidades • -- declaração de variáveis Begin • ...– código sequencial 57 End process; Lista de sensibilidades: sinais de entrada do processo Processos: process Declaração de variáveis (variable) apenas visíveis no escopo do processo process (A, B, Cin) variable carry : std_logic; begin S <= A xor B xor Cin; carry := (A and B) or (Cin and B) or (Cin and A); Cout <= carry; end process; Atribuição a variáveis utiliza := 58 Processos: process Possibilidade de utilização de instruções de controlo com o modelo imperativo Condicionais • • Ciclos • • • • 59 If: [LABEL:] if expr then ... [{elsif expr then ...}] [else ... ] end if [LABEL]; Case: [LABEL:] case expr is {when choice [{| choice}] => ...} end case [LABEL]; For: [LABEL:] for ID in range loop ... end loop [LABEL]; While: [LABEL:] [while expr] loop ... end loop [LABEL]; next [LOOPLBL] [when expr]; exit [LOOPLBL] [when expr]; if S, temp: std_logic_vector(7 downto 0) Enable: std_logic process(enable, temp) begin IF enable = ‘0' THEN S <= temp; ELSE S <= "ZZZZZZZZ"; END IF; end process; 60 case Descodificador de código BCD para disply de sete segmentos process(inp_data) begin case inp_data is when "0000" => out_data <= "0000001"; when "0001" => out_data <= "1001111"; when "0010" => out_data <= "0010010"; when "0011" => out_data <= "0000110"; when "0100" => out_data <= "1001100"; when "0101" => out_data <= "0100100"; when "0110" => out_data <= "0100001"; when "0111" => out_data <= "0001111"; when "1000" => out_data <= "0000000"; when "1001" => out_data <= "0000100"; when others => out_data <= "1111111"; end case; end process; 61 c5 c4 c0 c6 c1 c2 c3 c0 c1 c2 c3 c4 c5 c6 Descodificador de BCD para 7– segmentos A B C D when others => out_data <= “-------"; for Tris, A, tris: std_logic_vector(7 downto 0) process(tris, A) begin for i in 0 to 7 loop IF tris(i) = '0' THEN PORTA(i) <= A(i); ELSE PORTA(i) <= 'Z'; END IF; end loop; end process; 62 while Tris, A, tris: std_logic_vector(7 downto 0) process(tris, A) variable i: integer; -- :=0; begin i := 0; while i <=7 loop IF tris(i) = '0' THEN PORTA(i) <= A(i); ELSE PORTA(i) <= 'Z'; END IF; i := i+1; end loop; end process; 63 Loop Tris, A, tris: std_logic_vector(7 downto 0) process(tris, A) variable i: integer; -- :=0; begin i := 0; L1: loop IF tris(i) = '0' THEN PORTA(i) <= A(i); ELSE PORTA(i) <= 'Z'; END IF; i := i+1; exit L1 when i > 7; -- if(i > 7) then return; end if; end loop; end process; 64 Processos: process Cuidados com a síntese lógica Ciclos (loops) Número de iterações tem de ser conhecido estaticamente A ferramenta de síntese lógica desenrola completamente os ciclos Não consegue gerar uma arquitectura com controlo (essa síntese chama-se de síntese de alto-nível) 65 Processos: variables versus signals Variables 66 Actualizadas instantaneamente Signals Actualizados no fim do processo Processos: variables versus signals entity xor_sig is port (A, B, C: in STD_LOGIC; X, Y: out STD_LOGIC); end xor_sig; architecture SIG_ARCH of xor_sig is signal D: STD_LOGIC; begin SIG:process (A,B,C) begin D <= A; -- ignored !! X <= C xor D; D <= B; -- overrides !! Y <= C xor D; end process; end SIG_ARCH; 67 entity xor_var is port (A, B, C: in STD_LOGIC; X, Y: out STD_LOGIC); end xor_var; architecture VAR_ARCH of xor_var is begin VAR:process (A,B,C) variable D: STD_LOGIC; begin D := A; X <= C xor D; D := B; Y <= C xor D; end process; end VAR_ARCH; Exemplo: somador de 4 bits library IEEE; use IEEE.std_logic_1164.all; entity adder is port(A, B: in std_logic_vector(3 downto 0); Cin: in std_logic; S: out std_logic_vector(3 downto 0); Cout: out std_logic); end adder; 68 Exemplo: somador de 4 bits architecture comportamental of adder is signal S0: std_logic_vector(4 downto 0); Begin S0 <= ('0' & A) + ('0' & B) + Cin; S <= S0(3 downto 0); Cout <= S0(4); end comportamental; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; 69 Exemplo: somador de 4 bits architecture comportamental of adder is signal S0: std_logic_vector(4 downto 0); Begin S0 <= ('0' & A) + ('0' & B) + Cin; S <= S0(3 downto 0); Cout <= S0(4); end comportamental; 70 Exemplo: somador de 4 bits architecture estrutural of adder is component FullAdder port (A , B, CI: CO, S : in std_logic; out std_logic ); end component; signal cin_temp: std_logic_vector(4 downto 0); begin cin_temp(0) <= Cin; gen: for i in 0 to 3 generate FA: FullAdder port map(A=>A(i), B=>B(i), Cin=>cin_temp(i), Cout=>cin_temp(i+1), S=>S(i)); end generate gen; Cin Cin a0 b0 a a1 b1 a2 b2 Cout <= cin_temp(4); b Cout Cin a FA1 s b s1 Cout Cin a s0 FA2 s b s2 Cout Cin end estrutural; 71 FA0 s a3 b3 a b FA3 s Cout s3 Cout Exemplo: somador de 4 bits Full Adder (FA) Cin a b Cin a b s FA s Cout Cout 72 Exemplo: somador de 4 bits Cin a b Full Adder (FA) entity FullAdder is port (A , B, Cin: in std_logic; Cout, S : out std_logic ); end FullAdder; Cin a b FA s Cout architecture logic of FullAdder is Begin process (A, B, Cin) variable carry : std_logic; begin S <= A xor B xor Cin; Cout <= (A and B) or (Cin and b) or (Cin and a); end process; end logic; 73 s Cout Exemplo: somador de N bits? Utilização de parâmetros Por omissão N=8 entity adder is generic(N: integer := 8); port(A, B: in std_logic_vector(N-1 downto 0); Cin: in std_logic; S : out std_logic_vector(N-1 downto 0); Cout: out std_logic); end adder; 74 Exemplo: somador de N bits? architecture comportamental of adder_param is signal S0: std_logic_vector(N downto 0); Begin S0 <= ('0' & A) + ('0' & B) + Cin; S <= S0(N-1 downto 0); Cout <= S0(N); end comportamental; 75 Exemplo: somador de N bits? architecture estrutural of adder_param is component FullAdder port (A , B, Cin: Cout, S : in std_logic; out std_logic ); end component; signal cin_temp: std_logic_vector(N downto 0); Instrução para gerar N instâncias do FullAdder Begin cin_temp(0) <= Cin; gen: for i in 0 to N-1 generate FA: FullAdder port map(A=>A(i), B=>B(i), Cin=>cin_temp(i), Cout=>cin_temp(i+1), S=>S(i)); end generate gen; Cout <= cin_temp(N); end estrutural; 76 Parâmetros Como redefinir o valor dos parâmetros para cada instância do componente? ADD1: adder generic map(32) port map(A1, B1, Cin1, S1, Cout1) ADD2: adder generic map(8) port map(A2, B2, Cin2, S2, Cout2) 77 Parâmetros Declarados como generic na entity Ou num package como constantes Utilização de duas instruções para gerar instâncias For ... Generate : instrução cíclica If ... generate : geração condicional 78 Exemplo: Máquina de Bebidas Disponibiliza a lata depois de 150 ou mais escudos terem sido depositados Uma única abertura para moedas Reset (50$00 e 100$00) Não dá troco CEM Sensor de Moedas 79 CINQ FSM da máquina de bebidas Clock Abre Mecanismo de Libertar Lata Exemplo: Máquina de Bebidas Tabela e Diagrama de Estados Reset Estado Actual 0$ 0$ CINQ 50$ 50$ CEM CINQ CEM 100$ 100$ CEM + CINQ 150$ 80 [open] 150$ Entrada CEM CINQ 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 – – Próx. Estado 0$ 50$ 100$ – 50$ 100$ 150$ – 100$ 150$ 150$ – 150$ Tabela de estados Simbólica Saída open 0 0 0 – 0 0 0 – 0 0 0 – 1 Exemplo: Máquina de Bebidas library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity fsm is Port ( clk : in std_logic; reset : in std_logic; CEM : in std_logic; CINQ : in std_logic; s_open : out std_logic); end fsm; architecture Behavioral of fsm is type state_type is (zero, cinquenta, st_cem, cent_cinq); signal current_state, next_state: state_type; begin process(reset, clk) begin if reset = '1' then current_state <= zero; elsif clk'event AND clk='1' then current_state <= next_state; end if; end process; 81 process(current_state, CEM, CINQ) begin s_open <= '0'; case current_state is when zero => if CINQ = '1' then next_state <= cinquenta; elsif CEM = ‘1’ then next_state <= st_cem; else next_state <= zero; end if; when cinquenta => if CINQ = '1' then next_state <= st_cem; elsif CEM = '1' then next_state <= cent_cinq; else next_state <= cinquenta; end if; when st_cem => if CINQ = '1' OR CEM = '1' then next_state <= cent_cinq; else next_state <= st_cem; end if; when cent_cinq => s_open <= '1'; next_state <= zero; when others => next_state <= zero; end case; end process; end Behavioral; Funções e Procedimentos Corpo executa sequencialmente Permitem declaração de variáveis locais Funções: devolvem dados utilizando a instrução return function allzero(A: std_logic_vector(7 downto 0)) return std_logic is variable val: std_logic; Begin … Return Val; End allzero; Procedimentos: devolvem dados através de variáveis de saída nos argumentos procedure allzero(A: in std_logic_vector(7 downto 0), O: out std_logic) is Begin O := …; End allzero; 82 Redefinição de funções e procedimentos Exemplo: function max(A, B: myType) return myType; function max(A, B, C: myType) return myType; 83 Sobrecarga de operadores Exemplo: 84 function "+"(L: UNSIGNED; R: UNSIGNED) return UNSIGNED; function "+"(L: SIGNED; R: SIGNED) return SIGNED; function "+"(A,B: myType) return myType; function "+"(L: UNSIGNED; R: UNSIGNED) return UNSIGNED is constant length: INTEGER := max(L'length, R'length); begin return unsigned_plus(CONV_UNSIGNED(L, length), CONV_UNSIGNED(R, length)); end; function "+"(L: SIGNED; R: SIGNED) return SIGNED is constant length: INTEGER := max(L'length, R'length); begin return plus(CONV_SIGNED(L, length), CONV_SIGNED(R, length)); end; ... Packages library IEEE; use IEEE.std_logic_1164.all; package aritmetica is function allzero(A: std_logic_vector(7 downto 0)) return std_logic; function "+"(A,B: std_logic_vector(7 downto 0)) return std_logic_vector; … end aritmetica; package body aritmetica is function allzero(A: std_logic_vector(7 downto 0)) return std_logic is variable Z: std_logic; begin if (A = "00000000") then Z := '1'; else Z := '0'; end if; return(Z); end allzero; … 85 end aritmetica; Packages Exemplo: library IEEE; use IEEE.std_logic_1164.all; package rom is constant ROM_WIDTH: integer := 12; constant ROM_LENGTH: integer := 135; subtype ROM_WORD is std_logic_vector (ROM_WIDTH-1 downto 0); subtype ROM_RANGE is integer range 0 to ROM_LENGTH-1; type ROM_TABLE is array (0 to ROM_LENGTH-1) of ROM_WORD; constant ROM: ROM_TABLE := ROM_TABLE'( ROM_WORD'("000000000000"), ROM_WORD'("000001000000"), ROM_WORD'("000000000010"), ... ROM_WORD'("000000000000"), ROM_WORD'("000000000000")); end rom; Utilização da package: Library work; Use work.rom.all; 86 Outras potencialidades Ficheiros utilizados para simulação como armazenamento de dados de memórias 87 Etc. Síntese Gera a estrutura de um circuito A partir do código VHDL Utiliza os componentes existentes numa biblioteca (portas lógicas, unidades aritméticas, etc.) 88 Inferência de determinados componentes com base na descrição VHDL Síntese: Inferência Largura em bits numa linha Número de bits atribuído a um sinal ou porto Exemplo: Port A: in integer range 0 to 15; • Síntese atribui 4 bits a A 89 Síntese: Inferência 90 A, B, S: std_logic_vector(7 downto 0) S <= A + B; Síntese atribui um somador de 8 bits sem sinal S <= SIGNED(A) + SIGNED(B); Síntese atribui um somador de 8 bits com sinal SIGNED é uma função da package STD_LOGIC_ARITH da biblioteca IEEE Converte std_logic_vector em representação de inteiros com sinal: signed Síntese: Inferência Flip Flop com reset assíncrono process(reset, clk) Begin if(reset = '1') then Q <= '0'; elsif(clk'event and clk='1') then Q <= D; End if; end process; 91 Síntese: Inferência Flip Flop com reset síncrono process(reset, clk) begin if(clk'event and clk='1') then if(reset = '1') then Q <= '0'; else Q <= D; end if; End if; end process; 92 Síntese: Inferência Latch process(load, D) begin if(load = '1') then Q <= D; end if; end process; 93 Síntese: Inferência Multiplexador process(sel, D1, D2) begin if(sel = '1') then Q <= D1; else Q <= D2; end if; end process; 94 Síntese: Inferência Flip-Flop com sinal de load process(reset, clk, load) begin if(reset = '1') then Q <= '0'; elsif(clk'event and clk='1') then if(load = '1') then Q <= D; end if; End if; end process; 95 Síntese: Inferência tabelas de valores: ROMs ou portas lógicas library IEEE; use IEEE.std_logic_1164.all; entity tabela is port (ADDR : in INTEGER range 0 to 3; DATA : out STD_LOGIC_VECTOR (1 downto 0)); end tabela ; architecture description of tabela is subtype ROM_WORD is STD_LOGIC_VECTOR (1 downto 0); type ROM_TABLE is array (0 to 3) of ROM_WORD; constant ROM : ROM_TABLE := ROM_TABLE’( ROM_WORD’("01"), ROM_WORD’("00"), ROM_WORD’("10"), ROM_WORD’("11")); begin DATA <= ROM(ADDR); -- Read from the ROM end description ; 96 Síntese: Inferência Distributed RAMs ... process (clk) begin if (clk'event and clk = '1') then if (we = '1') then RAM(conv_integer(a)) <= di; end if; end if; end process; do <= RAM(conv_integer(a)); Read assíncrono ... 97 Síntese: Inferência Block RAMs ... process (clk) begin if (clk'event and clk = '1') then if (we = '1') then RAM(conv_integer(a)) <= di; end if; index <= conv_integer(a); end if; end process; do <= RAM(index); Read síncrono ... 98 Comentários VHDL é uma linguagem definida para simulação de sistemas digitais 99 Inclui muitas formas de especificação não suportadas por ferramentas de síntese No projecto de sistemas digitais com síntese lógica utiliza-se um sub-conjunto de VHDL boa regra de descrição: evitar código ao qual não associamos um tipo de estrutura de hardware

Baixar