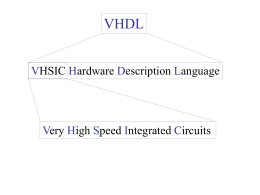

Circuit Design and Simulation with VHDL 2nd edition Volnei A. Pedroni MIT Press, 2010 Book web: www.vhdl.us Appendix D ModelSim Tutorial (ModelSim 10.1d) This tutorial is based on ModelSim 10.1d Altera Starter Edition (free at www.altera.com), which accompanies, for example, Quartus II 13.0 sp1. The circuit used in this tutorial is the 4‐stage shift register of figure 1a. The waveforms to be generated for rst, clk, and din are shown in figure 1b, from which the waveforms shown for q and dout are expected. din clk rst d0 q0 rst d1 q1 rst (a) d2 q2 rst d3 q3 dout rst Figure 1 (b) 1. Files Needed for Simulation To perform functional simulation, two files must be created by the user (see figure 2): ‐ A design file (shift_register.vhd). ‐ A test file (shift_register_tb.vhd). To perform timing simulation, two additional files are needed, both generated by the synthesizer (Quartus II, for example): ‐ A post synthesis file (shift_register.vho). ‐ An SDF (standard delay format) file (shift_register.sdo), which contains the propagation delays. Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 2 -----------------------------------------LIBRARY ieee; USE ieee.std_logic_1164.all; -----------------------------------------ENTITY shift_register IS PORT (clk, rst, din: IN STD_LOGIC; dout: OUT STD_LOGIC); END ENTITY; -----------------------------------------ARCHITECTURE mydesign OF shift_register IS BEGIN PROCESS (clk, rst) VARIABLE q: STD_LOGIC_VECTOR(0 TO 3); BEGIN IF rst='1' THEN q := (OTHERS => '0'); ELSIF rising_edge(clk) THEN q := din & q(0 TO 2); END IF; dout <= q(3); END PROCESS; END ARCHITECTURE; ------------------------------------------ (a) Design file (shift_register.vhd) Figure 2 --------------------------------------------------LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------------ENTITY shift_register_tb IS END ENTITY; --------------------------------------------------ARCHITECTURE testbench OF shift_register_tb IS --DUT declaration: COMPONENT shift_register IS PORT (clk, rst, din: IN STD_LOGIC; dout: OUT STD_LOGIC); END COMPONENT; --Signal declarations: SIGNAL clk: STD_LOGIC := '0'; SIGNAL rst: STD_LOGIC := '1'; SIGNAL din: STD_LOGIC := '0'; SIGNAL dout: STD_LOGIC; BEGIN --DUT instantiation: dut: shift_register PORT MAP (clk, rst, din, dout); --Stimuli generation: clk <= NOT clk AFTER 40 ns; rst <= '0' AFTER 80 ns; din <= '1' AFTER 160 ns, '0' AFTER 240 ns, '1' AFTER 320 ns; END ARCHITECTURE; --------------------------------------------------- (b) Testbench file (shift_register_tb.vhd) 2. Preparing ModelSim a) Before starting ModelSim, create a directory where all files should be located (c:/.../shift_register). b) Launch ModelSim. This opens the screen of figure 3a. Click Jumpstart, leading to figure 3b. Click Create a Project, which opens the dialog of figure 3c. Enter the project name (shift_register) and the project location (c:/.../shift_register). Click OK, leading to figure 3d, then click Close. (a) Figure 3 (b) (c) (d) c) The following setup is suggested: ‐ In the View menu, mark only Library and Transcript. ‐ In the Window menu, mark only Show Toolbar and Show Window Headers. ‐ In the Window > Toolbar menu, mark Standard, Compile, and Simulate. The resulting screen is that shown in figure 4, but with the work directory (top left) still empty. 2 Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 3 d) To type the files of figure 2, select File > New > Source > VHDL, which opens the VHDL editor. Type each file and save it in the directory created in step (a). Leave these files open, as shown in figure 5. e) Select File > Change Directory and change to the directory created in step (a). Figure 4 Figure 5 3. Performing Functional Simulation For functional simulation, proceed below. For timing simulation, go to section 4. a) Select Compile > Compile or click . This opens the dialog of figure 6a. Select both files (shift_register.vhd and shift_register_tb.vhd) and click Compile. When finished, click Done. (If you are debugging a file, you can compile it separately.) 3 Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 4 b) Select Simulate > Start Simulation. This leads to figure 6b. c) Expand the work library in figure 6b, select shift_register_tb, then click OK. This leads to figure 6c (without the waveforms yet). d) Click the right mouse button on shift_register_tb in figure 6c (top left corner) and select Add to > Wave > All items in region. This places the signal names (no waveforms yet) as shown in the center of figure 6c. e) Any signal in the wave list can be dragged up or down (reset and clock are usually wanted at the top). To do so, press and hold the left mouse button on the signal’s name and move it to the desired position. f) Set the simulation time interval by selecting Simulate > Runtime Options and entering Default Run = 720 ns. or selecting Simulate > Run > Run 100. Click then the zoom full icon g) Finally, run the simulation by clicking see the complete waveforms of figure 6d. h) Repeat step (g) a few times. Note that the plot grows 720 ns each time. i) Clean the waveforms window by clicking the restart icon (compare to figure 1b). (a) to , then repeat steps (g)‐(h). Finally, inspect the results (b) (c) Figure 6 4. Performing Timing Simulation a) Go to Quartus to get the two additional files: ‐ Launch Quartus II and load the shift_register.vhd file. ‐ Select Assignments > Settings > EDA Tools Settings > Simulation > Tool name > ModelSim‐Altera and click OK. ‐ Compile the design. In the work directory, a simulation/modelsim (default name) subdirectory is automatically created, containing the files shift_register.vho and shift_register_vhd.sdo. ‐ Copy these two files to the ModelSim work directory and return to the ModelSim software. b) Compile the files: 4 Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 5 ‐ Click or select Compile > Compile. This opens the dialog of figure 7a. Select the files shift_register.vho and shift_register_tb.vhd and click Compile. When finished, click Done. (If you are debugging a file, you can compile it separately.) c) Select Simulate > Start Simulation, which leads to figure 7b. d) Expand the work library in figure 7b and select shift_register_tb. Open then the SDF tab and click Add. This leads to figure 7c. In SDF File, select shift_register_vhd.sdo. In Apply to Region, type /shift_register_tb/DUT. Click OK (twice). e) Click the right mouse button on shift_register_tb in figure 7e (top left corner) and select Add to > Wave > All items in region. This places the signal names (no waveforms yet) as shown in the center of figure 7d. f) Any signal in the wave list can be dragged up or down (reset and clock are usually wanted at the top). To do so, press and hold the left mouse button on the signal’s name and move it to the desired position. g) Set the simulation time interval by selecting Simulate > Runtime Options and entering Default Run = 720 ns. or selecting Simulate > Run > Run 100. Click then the zoom full icon to h) Finally, run the simulation by clicking see the complete waveforms of figure 7e. Observe that there are now propagation delays between clock transitions and corresponding dout transitions. i) Repeat step (h) a few times. Note that the plot grows 720 ns each time. j) Clean the waveforms window by clicking the restart icon (compare to figure 1b). , then repeat steps (h)‐(i). Finally, inspect the results 5 Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 6 (a) (b) (c) (d) Figure 7 5. Using Breakpoints To add breakpoints, follow the procedure below. a) Run the simulation (without breakpoints yet). b) The lines of the testbench file that are enumerated in red accept breakpoints. Click on the line number to include a breakpoint (red dot). c) Run the simulation with breakpoints included. d) To disable a breakpoint, click on it (black dot). To remove it, use the right mouse button. 6. Running ModelSim with Tcl Commands (Manual Simulation) 6 Circuit Design and Simulation with VHDL, 2nd Edition, V. A. Pedroni, MIT Press 7 Tcl (tool command language) is a scripting language. Like any other EDA software, ModelSim too can be run using Tcl commands (this is called command‐line mode, as opposed to GUI mode, employed for manual graphical input). The main commands for the present purpose are described below. a) Command add wave: Adds a new wave to the wave pane. Example: add wave clk b) Command run: The first example below causes the simulation to run until the time limit set in the simulator is reached. The other two cause the simulation to advance 300ns (ps is the default time unit). Examples: run, run 300ns, run 300000 c) Command restart: Causes the waveforms to be cleared, with the simulator returning to time zero. d) Command force for periodic waveforms (like clock): Below, ‐r stands for “repeat”; freeze is the default value, so it can be omitted. In the example, ‘0’ is the initial value, 150 ns is the period, and 50% is the duty cycle. Syntax: force [–freeze] <signal_name> <value> <time>, <value> <time> ‐r <time> Example: force clk 0 0ns, 1 75ns –r 150ns d) Command force for non‐periodic waveforms (like reset): In the example below, the initial value ‘1’ during 50 ns, then ‘0’ forever. Syntax: force <signal_name> <value> run <time> ... force <signal_name> <value> Example: force rst 1 run 50ns force rst 0 e) Command do: Runs a DO file. Example: do mydesign.do f) DO file: Script file consisting of Tcl commands. It constitutes a very effective way of documenting and reusing test sequences. Example of DO file: An example is shown in figure 8b, which produces the signals clk, rst, and din depicted in figure 8a. If we develop a simulation up to the Add to > Wave step, the rest can be performed with this file. Save it with the extension .do and run it with the command do mydesign.do. The resulting waveform (dout) is shown in the last plot of figure 8a. If the add wave commands (lines 1‐4) that are commented out in the DO file are included, then the Add to > Wave step is not needed. Figure 8 (a) (b) 7

Baixar