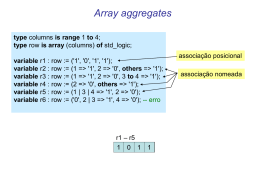

VHDL VHSIC Hardware Description Language Very High Speed Integrated Circuits entidade reg4 portas de entrada d0 s0 d1 s1 d2 s2 d3 s3 portas de saída en clk entity reg4 is port (d0, d1, d2, d3, en, clk : in bit; s0, s1, s2, s3 : out bit ); end entity reg4; declaração da entidade A descrição da implementação interna duma entidade chama-se corpo arquitectural. Uma entidade pode ter vários corpos arquitecturais que correspondem às implementação alternativas. Corpo arquitectural comportamental descreve o funcionamento de um modo abstracto; só inclui atribuições de sinais concorrentes e processos que especificam acções sequenciais a executar. estrutural descreve que subsistemas compõem a entidade e como estes são interligados. misto algumas partes da entidade são descritas como comportamentais enquanto outras são descritas de modo estrutural. Descrição comportamental architecture Behavioral of reg4 is begin process (d0, d1, d2, d3, en, clk) is begin if en = '1' and clk = '1' then s0 <= d0; s1 <= d1; s2 <= d2; s3 <= d3; end if; end process; end Behavioral; Descrição estrutural bit0 latch d s d0 s0 clk bit1 latch d s d1 s1 clk bit2 latch d s d2 s2 clk bit3 latch d s d3 en clk gate and2_gate x z y clk s3 Descrição estrutural bit0 latch d s d0 s0 clk bit1 latch d s d1 s1 clk bit2 latch d s d2 s2 entity latch is port ( d, clk : in bit; s : out bit); end latch; architecture beh of latch is begin latch_beh: process (clk, d) is begin if clk = '1' then s <= d; end if; end process latch_beh; end beh; clk bit3 latch d s d3 s3 entity and2_gate is Port ( x, y : in bit; z : out bit); end and2_gate; clk en x clk y z and2_gate architecture beh of and2_gate is begin z <= x and y; end beh; Descrição estrutural bit0 latch d s d0 s0 clk bit1 latch d s d1 s1 clk bit2 latch d s d2 s2 entity latch is port ( d, clk : in bit; s : out bit); end latch; architecture beh of latch is begin process (clk, d) is begin if clk = '1' then s <= d; end if; end process; end beh; clk bit3 latch d s d3 s3 entity and2_gate is Port ( x, y : in bit; z : out bit); end and2_gate; clk en x clk y z and2_gate architecture beh of and2_gate is begin z <= x and y; end beh; entity reg4 is Port ( d0, d1, d2, d3, en, clk : in bit; s0, s1, s2, s3 : out bit); end reg4; architecture estrutural of reg4 is signal int_clk : bit; bit0 latch s s d0 bit1 latch s s d1 gate: entity work.and2_gate(beh) port map (en, clk, int_clk); end estrutural; s1 clk bit2 latch s s d2 int_clk begin bit0: entity work.latch(beh) port map (d0, int_clk, s0); bit1: entity work.latch(beh) port map (d1, int_clk, s1); bit2: entity work.latch(beh) port map (d2, int_clk, s2); bit3: entity work.latch(beh) port map (d3, int_clk, s3); s0 clk d3 en clk gate and2_gate x z y s2 clk bit3 latch s s clk instâncias de componentes s3 library IEEE; use IEEE.std_logic_1164.all; entity design_module_ent is port ( input1,input2,input3,input4 : in STD_LOGIC; output1,output2,output3: out STD_LOGIC ); end design_module_ent; architecture design_module_ent_arch of design_module_ent is component and_ent port ( input1,input2 : in STD_LOGIC; output1: out STD_LOGIC ); end component; begin logic_AND_1 : and_ent PORT MAP (input1,input2,output1); logic_AND_2 : and_ent PORT MAP (input2,input3,output2); logic_AND_3 : and_ent PORT MAP (input3,input4,output3); end design_module_ent_arch; library IEEE; use IEEE.std_logic_1164.all; entity design_module_ent is port ( input1,input2,input3,input4 : in STD_LOGIC; output1,output2,output3: out STD_LOGIC ); end design_module_ent; architecture design_module_ent_arch of design_module_ent is component and_ent port ( input1,input2 : in STD_LOGIC; output1: out STD_LOGIC ); end component; begin logic_AND_1 : and_ent PORT MAP (input1,input2,output1); logic_AND_2 : and_ent PORT MAP (input2,input3,output2); logic_AND_3 : and_ent PORT MAP (input3,input4,output3); end design_module_ent_arch; input1 input2 input3 input4 output1 output2 output3 library IEEE; use IEEE.std_logic_1164.all; entity adder1 is port ( A: in STD_LOGIC; B: in STD_LOGIC; A SUM: out STD_LOGIC; CARRY: out STD_LOGIC ); end adder1; B architecture adder1_arch of adder1 is CARRY begin -- <<enter your statements here>> SUM <= A xor B; CARRY <= A and B; end adder1_arch; SUM library IEEE; use IEEE.std_logic_1164.all; entity FULLADD is port (A, B, CIN : in bit; SUM, CARRY : out bit); end FULLADD; entity adder1 is port ( A: in STD_LOGIC; B: in STD_LOGIC; SUM: out STD_LOGIC; CARRY: out STD_LOGIC ); end adder1; architecture adder1_arch of adder1 is begin -- <<enter your statements here>> SUM <= A xor B; CARRY <= A and B; end adder1_arch; library IEEE; use IEEE.std_logic_1164.all; entity ORGATE is port ( A: in STD_LOGIC; B: in STD_LOGIC; Z: out STD_LOGIC ); end ORGATE; OR architecture ORGATE_arch of ORGATE is begin -- <<enter your statements here>> Z <= A or B; end ORGATE_arch; Z architecture STRUCT of FULLADD is signal I1, I2, I3 : bit; component adder1 port(A,B : in bit; SUM, CARRY : out bit); end component; component ORGATE port(A,B : in bit; Z : out bit); end component; begin u1:adder1 port map(A,B,I1,I2); u2:adder1 port map(I1,CIN,SUM,I3); u3:ORGATE port map(I2,I3,CARRY); end STRUCT; entity FULLADD is port (A, B, CIN : in bit; SUM, CARRY : out bit); end FULLADD; A B A (A) B (B) architecture STRUCT of FULLADD is signal I1, I2, I3 : bit; component adder1 port(A,B : in bit; SUM, CARRY : out bit); end component; component ORGATE port(A,B : in bit; A (I1) Z : out bit); end component; CIN begin B (CIN) u1:adder1 port map(A,B,I1,I2); u2:adder1 port map(I1,CIN,SUM,I3); u3:ORGATE port map(I2,I3,CARRY); end STRUCT; CARRY (I2) I2 I3 OR CARRY (I3) SUM (I1) CARRY CARRY (CARRY) SUM SUM (SUM) SW1 SW2 SW3 LED1 LED2 LED3 LED4 LEDs : out std_logic_vector(3 downto 0); entity LCD_struc is Port ( switchers : in std_logic_vector(2 downto 0); LEDs : out std_logic_vector(3 downto 0); clk48 : in std_logic; rst : in std_logic); end LCD_struc; LCD_struc architecture Behavioral of LCD_struc is 48 MHz component LED_SW clk48 Divider PORT (CLK,RESET,SW1,SW2,SW3: IN std_logic; rst loc_clk rst LED1,LED2,LED3,LED4 : OUT std_logic); 1 Hz internal_clock end component; component Divider RESET CLK S3 Port ( clk48 : in std_logic; switchers(2) SW1 LED_SW S2 SW2 switchers(1) rst : in std_logic; S1 SW3 switchers(0) loc_clk : out std_logic); LED1 LED2 LED3 LED4 switchers : in end component; std_logic_vector signal internal_clock : STD_LOGIC; (2 downto 0); LEDs(0) LEDs(1) LEDs(2) LEDs(3) begin L1 L2 L3 L4 FSM : Divider port map(clk48,rst,internal_clock); led_control : LED_SW port map(internal_clock,rst,switchers(2),switchers(1),switchers(0), LEDs(0),LEDs(1),LEDs(2),LEDs(3)); end Behavioral; LEDs : out std_logic_vector(3 downto 0); entity LCD_struc is Port ( switchers : in std_logic_vector(2 downto 0); LEDs : out std_logic_vector(3 downto 0); clk48 : in std_logic; rst : in std_logic); end LCD_struc; LCD_struc architecture Behavioral of LCD_struc is 48 MHz component LED_SW clk48 Divider PORT (CLK,RESET,SW1,SW2,SW3: IN std_logic; rst loc_clk rst LED1,LED2,LED3,LED4 : OUT std_logic); 1 Hz internal_clock end component; CLK component Divider RESET S3 Port ( clk48 : in std_logic; switchers(2) SW1 LED_SW S2 SW2 switchers(1) rst : in std_logic; S1 SW3 switchers(0) loc_clk : out std_logic); LED1 LED2 LED3 LED4 switchers : in end component; std_logic_vector signal internal_clock : STD_LOGIC; (2 downto 0); LEDs(0) LEDs(1) LEDs(2) LEDs(3) begin L1 L2 L3 L4 connection FSM : Divider port map(clk48,rst,internal_clock); led_control : LED_SW port map(internal_clock,rst,switchers(2),switchers(1),switchers(0), LEDs(0),LEDs(1),LEDs(2),LEDs(3)); end Behavioral; VHDL entity architecture entity my_gate is port ( x1: in STD_LOGIC; x2: in STD_LOGIC; x3: in STD_LOGIC; y: out STD_LOGIC ); architecture my_gate_arch of my_gate is begin -- <<enter your statements here>> y <= not (x1 and x2 and x3); end my_gate_arch; configuration configuration config_and of and_ent is for and_ent_arch end for; end config_and; library IEEE; use IEEE.std_logic_1164.all; entity and_ent is port ( input1: in STD_LOGIC; input2: in STD_LOGIC; output1: out STD_LOGIC ); end and_ent; architecture and_ent_arch of and_ent is begin Process(input1,input2) begin if ((input1 = '1') AND (input2 = '1')) then output1 <= '1'; else output1 <= '0'; end if; end Process; end and_ent_arch; architecture and_ent_arch1 of and_ent is begin output1 <= input1 and input2; end and_ent_arch1; configuration config_and of and_ent is for and_ent_arch end for; end config_and; configuration config_and of and_ent is for and_ent_arch1 end for; end config_and; library IEEE; use IEEE.std_logic_1164.all; entity and_ent is port ( input1: in STD_LOGIC; input2: in STD_LOGIC; output1: out STD_LOGIC ); end and_ent; architecture and_ent_arch of and_ent is begin Process(input1,input2) begin if ((input1 = '1') AND (input2 = '1')) then output1 <= '1'; else output1 <= '0'; end if; end Process; end and_ent_arch; architecture and_ent_arch1 of and_ent is begin output1 <= input1 and input2; end and_ent_arch1; configuration config_and of and_ent is for and_ent_arch end for; end config_and; STD_LOGIC 1) 2) 3) 4) 5) 6) 7) 8) 9) '1' - logical 1 '0' - logical 0 'H' – weak 1 'L' – weak 0 'X' – unknown 'U' – uninitialized 'Z' – high impedance '-' – don't care 'W' – weak unknown

Baixar