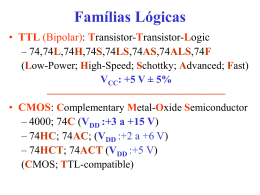

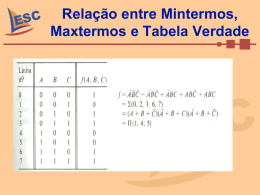

Concepção de Circuitos Integrados Lógica Combinacional Lógica Combinacional Os sinais de saída de um circuito são resultados de uma combinação lógica dos sinais de entrada atuais. Lógica Estática As saídas só mudam de valores a partir da mudança dos valores de entrada. Lógica Dinâmica As saídas representam o resultado da combinação lógica durante um tempo pré-determinado. Lógica Combinacional Lógica Estática - CMOS Estático Convencional - Lógica com Chaves - Lógica Proporcional (Ratioed Logic) -Resistive Load -Depletion nMOS Load -Pseudo nMOS Load Lógica Dinâmica - CMOS Dinâmico - Conventional Logic - 4-Phase Logic (Type A) - CMOS Domino Logic - CVSL, DCVSL Lógica Combinacional CMOS Estático Convencional • Exceto durante o período de transição, a saída de uma porta CMOS estática está ligada a VDD ou VSS (Massa) através de um caminho com baixa resistividade. OBS: Isto faz com que uma porta CMOS estática consuma muito menos que uma porta NMOS. • A saída de uma porta CMOS assume sempre o valor da função booleana implementada pelo circuito (ignorando novamente os efeitos de transição durante o período de chaveamento). • O colocado acima difere da classe de circuitos dinâmicos, que baseia-se no armazenamento temporário de valores de sinais em capacitâncias de nodos do circuito com alta impedância. Lógica Combinacional CMOS Estático Convencional VDD E1 E2 E3 Somente PMOS pull up S = f (E1,E2,E3) E1 E2 E3 pull down Somente NMOS VSS As redes PUP (pull up) e PDN (pull down) são duais. Lógica Combinacional CMOS Estático Convencional Fast Complex Gate - Design Techniques (1/2) • Transistor Sizing: As long as Fan-out Capacitance dominates • Progressive Sizing: Out InN MN CL M1 > M2 > M3 > MN In3 M3 C3 In2 M2 C2 In1 M1 C1 Distributed RC-line Can Reduce Delay with more than 30%! Lógica Combinacional CMOS Estático Convencional Fast Complex Gate - Design Techniques (2/2) • Transistor Ordering critical path critical path CL In3 M3 In2 M2 C2 In1 M1 C1 (a) CL In1 M1 In2 M2 C2 In3 M3 C3 (b) Lógica Combinacional Ratioed Logic VDD Resistive Load VDD Depletion Load RL PDN VSS (a) resistive load PMOS Load VSS VT < 0 F In1 In2 In3 VDD F In1 In2 In3 PDN VSS (b) depletion load NMOS F In1 In2 In3 PDN VSS (c) pseudo-NMOS Goal: to reduce the number of devices over complementary CMOS Lógica Combinacional Ratioed Logic Passive Loads VDD • N transistors + Load Resistive Load • VOH = V DD RL • VOL = F In1 In2 In3 . RPN VDD RPN + RL • Assymetrical response PDN • Static power consumption VSS • tpL= 0.69 RLCL Lógica Combinacional Ratioed Logic Active Loads VDD Depletion Load VDD PMOS Load VT < 0 VSS F In1 In2 In3 PDN VSS depletion load NMOS F In1 In2 In3 PDN VSS pseudo-NMOS Lógica Combinacional Ratioed Logic Pseudo-nMOS NOR Gate Pseudo-NMOS VDD A B C D F CL VOH = VDD (similar to complementary CMOS) V2 k 2 OL = -----p V k V –V V – ------------ DD – VTp n DD Tn OL 2 2 V OL = VDD – V T 1 – kp 1 – ------ (assuming that V T = V Tn = VTp ) kn SMALLER AREA & LOAD BUT STATIC POWER DISSIPATION!!! Onde: eox = 3,97 eo = 3,5 . 10-13 F/cm (permissividade do óxido) Lógica Combinacional Ratioed Logic Pseudo-nMOS NAND Gate Lógica Combinacional Ratioed Logic Outro exemplo de Pseudo-nMOS Gate … Lógica Combinacional Ratioed Logic Pseudo-nMOS Improved Load VDD M1 Enable M2 M1 >> M2 F A B C D Adaptive Load NOR-4 Gate CL Lógica Combinacional Conventional Dynamic CMOS Logic Lógica Combinacional Example of Conventional Dynamic CMOS Gates … Cascaded Dynamic Gates Problem! Lógica Combinacional Cascaded Conventional Dynamic CMOS Gates 4-phase Logic – Type A Lógica Combinacional Example of Cascaded Conventional Dynamic CMOS Gates 4-phase Logic – Type A Allowable gate connections Lógica Combinacional CMOS Domino Logic CMOS Domino Logic: (a) Basic Gate; (b) Static Version (low frequency); (c) Latching Version. Lógica Combinacional Cascode Voltage Switch Logic (CVSL) Fig. 5.11 pag. 170 Lógica Combinacional Dual Cascode Voltage Switch Logic (DCVSL) VDD M1 VDD M2 Out A A B B Out PDN1 PDN2 VSS VSS Dual Cascode Voltage Switch Logic (DCVSL)

Baixar