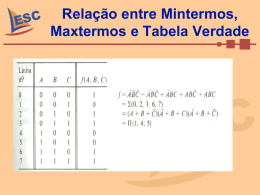

Famílias Lógicas • TTL (Bipolar): Transistor-Transistor-Logic – 74,74L,74H,74S,74LS,74AS,74ALS,74F (Low-Power; High-Speed; Schottky; Advanced; Fast) VCC: +5 V ± 5% ————————————————— • CMOS: Complementary Metal-Oxide Semiconductor – 4000; 74C (VDD :+3 a +15 V) – 74HC; 74AC; (VDD :+2 a +6 V) – 74HCT; 74ACT (VDD :+5 V) (CMOS; TTL-compatible) Ciclo de Vida das Famílias Lógicas Gates Básicos • INVERTER • NAND • NOR Por que? Importante: Ler págs. 53-56, do livro “Sistemas Digitais” de R. Tocci P ÂNODO N CATÔDO ÂNODO CATÔDO + – VB (a) Se VB < +0.6 V + – VB (b) Se VB > +0.6 V + – VB (NPN) (B) (C) (E) N VC >VE e VBE > 0.6 V P N Níveis de Voltagem e Estados Lógicos p/ TTL INPUT OUTPUT VHN VLN 1.6mA 10µA I. TOTEM-POLE II. OPEN-COLLECTOR III.TRI-STATE I. TOTEM-POLE II. OPEN-COLLECTOR SIMBOLOGIA PARA UM INVERSOR COM COLETOR ABERTO OPEN-COLLECTOR COM RESISTOR DE “PULL-UP” OPEN-COLLECTOR APLICAÇÃO COMO “WIRED-AND” SAÍDAS TOTEM-POLE E CONEXÃO WIRED-AND? OPEN-COLLECTOR APLICAÇÃO COMO “BUFFER/DRIVER” III.TRI-STATE TRISTATE APLICAÇÃO EM BARRAMENTO DE DADOS Simbologia p/ dispositivos c/ saída TRISTATE MOS Field Effect Transistors Níveis de Voltagem e Estados Lógicos p/ CMOS INPUT OUTPUT VHN VLN I. PUSH-PULL II. OPEN-DRAIN III. TRI-STATE Transmission Gate Níveis de Voltagem e Estados Lógicos p/ CMOS e TTL tPHL: propagation delay time from HIGH to LOW tPLH: propagation delay time from LOW to HIGH Gate Power versus Frequency CMOS versus TTL ICs CMOS: consomem uma potência menor do que os TTL permitem uma maior densidade de integração possuem uma maior imunidade a ruídos elétricos e alta impedância de entrada podem operar numa faixa maior de alimentação têm maiores fan-ins e fan-outs são mais sujeitos a danos por descarga eletrostática suas entradas não podem ser deixadas em aberto não são tão rápidos quanto aos TTLs small outline integrated circuit plastic leaded chip carrier leadless ceramic chip carrier

Baixar