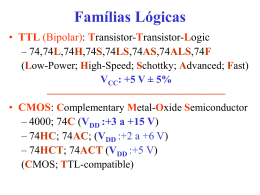

Concepção de Circuitos Integrados Portas Lógicas Tópicos abordados neste capítulo: Introdução – Lógica com Chaves Portas Lógicas nMOS Portas Lógicas nMOS: problema! Portas Lógicas CMOS Portas Lógicas com Chaves nMOS Portas Lógicas com Chaves nMOS: problema! Portas Lógicas com Chaves CMOS Portas Lógicas: otimização 2 Introdução – Lógica com Chaves Transistores podem ser vistos como uma chave controlada pelo sinal da grade Uma chave NMOS fecha quando o sinal de controle for VCC (1 lógico) B A E F F=E se A e B F F=E se A ou B A E B OBS: o transistor NMOS passa um 0 forte e um 1 fraco 3 Introdução – Lógica com Chaves Uma chave PMOS fecha quando o sinal de controle for VSS (0 lógico) B A E F F=E se A e B = A ou B = A + B F F=E se A ou B = A A E e . B =A B B OBS: o transistor PMOS passa um 0 fraco e um 1 forte 4 Portas Lógicas nMOS INVERSOR nMOS • Equação: • Esquema Elétrico nMOS: S=E Vcc • Esquema Lógico Transistor N de depleção S 10 S E E 0 1 saída 1 0 E 0 1 Transistor N V Terra 5 Portas Lógicas nMOS Porta NAND nMOS • Esquema Elétrico nMOS: • Equação Lógica: Vcc S=A.B • Esquema Lógico : S A S A B A B 0 0 0 1 1 0 1 1 saída 1 1 1 0 B Terra 6 Portas Lógicas nMOS Porta NOR nMOS • Esquema Elétrico nMOS: • Equação: S=A+B VCC • Esquema Lógico: A S S B A A B 0 0 0 1 1 0 1 1 saída 1 0 0 0 B terra 7 Portas Lógicas nMOS: problema! - Consumo de corrente (portanto, potência) elevado. - Custo de produção mais elevado devido ao acréscimo de etapas adicionais no processo de fabricação. 8 Portas Lógicas CMOS Circuitos CMOS Estáticos • Exceto durante o período de transição, a saída de uma porta CMOS estática está ligada a VDD ou VSS (Massa) através de um caminho com baixa resistividade. OBS: Isto faz com que uma porta CMOS estática consuma muito menos que uma porta NMOS. • A saída de uma porta CMOS assume sempre o valor da função booleana implementada pelo circuito (ignorando novamente os efeitos de transição durante o período de chaveamento). • O colocado acima difere da classe de circuitos dinâmicos, que baseia-se no armazenamento temporário de valores de sinais em capacitâncias de nodos do circuito com alta impedância. 9 Portas Lógicas CMOS Circuitos CMOS Estáticos VDD E1 E2 E3 De Morgan: A + B = A . B Somente PMOS pull up S = f (E1,E2,E3) E1 E2 E3 = pull down Somente NMOS AND = NAND + INV VSS As redes PUP (pull up) e PDN (pull down) são duais. 10 Portas Lógicas CMOS INVERSOR CMOS • Equação: • Esquema Elétrico CMOS: S=E Vcc • Esquema Lógico E V Transistor P S 10 S E 0 1 Transistor N V Terra 11 Portas Lógicas CMOS Porta NAND CMOS • Esquema Elétrico: • Equação Lógica: Vcc S=A.B S • Esquema Lógico : A B A S B Terra 12 Portas Lógicas CMOS Porta NOR CMOS • Esquema Elétrico CMOS: • Equação: VCC S=A+B • Esquema Lógico: A S A B S B terra 13 A B C D Portas Lógicas CMOS Porta NAND CMOS S VDD VDD A B C D S A S B C D terra A B C D terra 14 Portas Lógicas CMOS Portas CMOS Complexas SCCG (Static CMOS Complex Gate) VCC C Exemplo: A C D B B D S A S S = A + ( B .(C+D)) A B C A lógica da porta é definida pelos transistores de pull down. D terra 15 Portas Lógicas CMOS Portas CMOS Complexas SCCG (Static CMOS Complex Gate) Exercícios: Apresente o esquemático ao nível de transistores para os circuitos abaixo. 16 Portas Lógicas com Chaves nMOS B A E1 E1 E2 A B C Rede de chaves NMOS A’ G F G E2 B’ D - Transistores N - Sem consumo estático - Vg alto varia em função da lógica - Buffer regenera o sinal Concepção de Circuitos Integrados - 4.17 Adapted from … F Portas Lógicas com Chaves nMOS: problema! C=5v C=5v M2 E=5v F i F E=5v Mn CL CL M1 - VF não consegue atingir 5V, mas 5V -VTn ~ = 3,5 V devido ao efeito de corpo (boddy effect) - VF - Tensão na entrada do inversor não e’ suficiente para desligar o transistor PMOS - “Perda de tensão” causa consumo estático de potência e diminui margem de ruído Concepção de Circuitos Integrados - 4.18 Adapted from … Portas Lógicas com Chaves CMOS Símbolos: C C=5V F E F E C CL F E C=0V C OBS: o transistor PMOS passa um 0 fraco e um 1 forte o transistor NMOS passa um 0 forte e um 1 fraco Req de uma chave CMOS: cerca de 10 KΩ Desvantagem: temos que ter C e C Concepção de Circuitos Integrados - 4.19 Adapted from … Portas Lógicas com Chaves CMOS Multiplexador de 2 entradas S S S VDD VDD A M2 F F S M1 B S S S A Concepção de Circuitos Integrados - 4.20 B Adapted from … Portas Lógicas com Chaves CMOS XNOR e XOR XOR realizado com transistores de passagem B XNOR realizado com portas lógicas A B Z M2 A Z B M3 M1 M4 B B Concepção de Circuitos Integrados - 4.21 Adapted from … A Portas Lógicas: otimização Restruturação lógica para redução do fan-in redução do atraso da porta Concepção de Circuitos Integrados - 4.22 Adapted from …

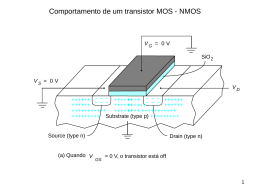

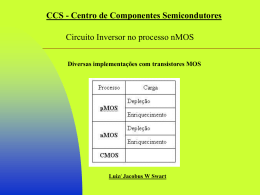

Baixar