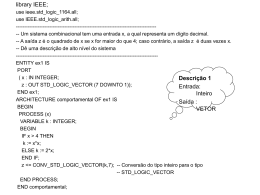

VHDL Linguagem de Descrição e Síntese de Circuitos Digitais Sistemas Digitais Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Especificação da Estrutura do Sistema Instanciação Direta Especificação da Estrutura do Sistema Instanciação Direta Especificação da Estrutura do Sistema Instanciação Direta Especificação da Estrutura do Sistema Componentes Especificação da Estrutura do Sistema Componentes Especificação da Estrutura do Sistema Componentes Especificação da Estrutura do Sistema Componentes Algumas Práticas que Devem ser Evitadas Maus exemplos: process (a,b) begin if (a = ‘1’) then q <= b; end if; end process; process(c) begin case c is when ‘0’ => q <= ‘1’; z <= ‘0’; when others => q <= ‘0’; end case; end process; • • Exemplo1 falta else Exemplo2 falta atribuição de z quando c é diferente de ‘0’. • • • • Para evitar: atribua valores default as saídas process(inputs,state) begin – outpus <= ‘0’; – case (state) – ... – end case; end process; • Teste x Verificação • Verificação – usado para verificar se o projeto está de acordo com o desejado – objetivo é verificar a funcionalidade – a ferramenta mais utilizada é o simulador • Teste – usado para verificar a fabricação do dispositivo – objetivo não é verificar a funcionalidade – objetivo é exercitar os nós físicos do sistema • nós devem ir de 0 para 1 ou de 1 para 0 – usa padrões específicos para exercitar estes nós • estes padrões são gerados por ferramenta de ATPG (automatic test pattern generation ) Test Bench testbench geração de estímulos UUT referencial avaliação de respostas Test Bench Test Bench Test Bench Test Bench Test Bench Test Bench Exemplo: Geração de estímulos • Origem dos estímulos: – formas de onda – de arquivos – de tabelas – aleatória – mista Estímulos Tipo Forma de Onda process begin s <= ‘0’ ; wait for 20 ns; s <= ‘1’ ; wait for 10 ns; s <= ‘0’ ; wait for 10 ns; s <= ‘1’ ; wait for 20 ns; s <= ‘0’ ; wait for 50 ns; s <= ‘1’ ; wait for 10 ns; s <= ‘0’ ; wait for 20 ns; s <= ‘1’ ; wait for 10 ns; s <= ‘0’ ; wait for 20 ns; s <= ‘1’ ; wait for 40 ns; s <= ‘0’ ; wait for 20 ns; end process; Estímulos de Arquivos procedure ReadFile() is variable lineAux : line; file PatternFile : TEXT open READ_MODE is “inputPattern.txt"; begin for i in 0 to nPolig-1 loop readline(PatternFile , lineAux); Vantagem: simples read(lineAux,value); implementação para padrões simples ... end loop; Desvantagem: end procedure; •difícil de implementar para padrões complexos •aumenta tempo de simulação devido as chamadas de sistema Estímulos de Tabela type vector is record LD : std_logic; LL : std_logic; Vantagem: menor tempo de RST : std_logic; simulação que estímulo de D : std_logic_vector(7 downto 0); arquivo P : std_logic; end record; type vectorArrayType is array (0 to TABLE_SIZE) of vector; constant vectorTable : vectorArrayType := ( -- LD LL RST D P ( ‘0’, ‘0’, ‘0’, “xxxxxxxx” ‘0’), Desvantagem: ( ‘0’, ‘0’, ‘1’, “xxxxxxxx” ‘0’), •aumenta tempo de compilação ( ‘0’, ‘0’, ‘1’, “xxxxxxxx” ‘0’), ( ‘1’, ‘0’, ‘0’, “00000101” ‘0’), •consome memória para muitos ( ‘0’, ‘1’, ‘0’, “11010100” ‘0’), padrões ( ‘0’, ‘0’, ‘0’, “xxxxxxxx” ‘1’), ( ‘0’, ‘0’, ‘0’, “xxxxxxxx” ‘1’), ... ); Test Bench - Verificação Test Bench - Verificação Exemplo: Práticas Básicas • Convenções de nomes (sinais, entidades, arquivos, etc) • Incluir headers nos fontes – descrição (func, autor, versão, etc) – formato e temp. de entrada e saída – histórico • Comentários (inglês) • Indentação • Instanciação (associação por nomes) • Uma linha por comando/declaração • Usar tipos baseados nos tipos padrões IEEE – std_logic, std_ulogic • Não usar valores fixos na descrição – use generic ou constant DISCIPLINA !!!

Baixar