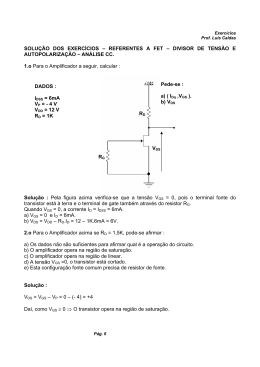

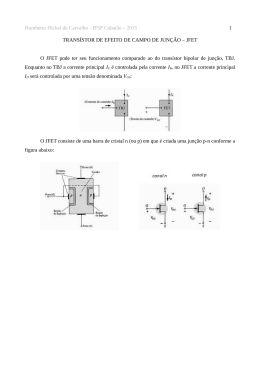

Concepção de Circuitos Integrados Modelos doTransistor MOS Informática UFRGS Transistor MOS fonte VGS - grade + óxido de gate canal N óxido de campo N+ N+ dreno P contato de substrato (bulk) Concepção de Circuitos Integrados - 12.2 adapted from: região de depleção substrato P Transistor MOS Regimes de funcionamento grade de polisilício óxido de silício SiO2 Vgs << Vt ISOLANTE substrato P região de depleção Vgs = Vt Acumulação região de inversão região de depleção Depleção Concepção de Circuitos Integrados - 12.3 adapted from: Inversão Vgs > Vt Transistor MOS Influência das tensões dos terminais Modo de inversão fonte Vg s - grade canal N - camada de inversão dreno + N+ N+ P √ Wd = 2 esi f q NA Vgs ≥ Vt p/ Vds = 0 camada de depleção onde: Wd - profundidade da camada de depleção NA- dopagem do substrato f - tensão através da região de depleção q - carga do elétron esi - permissividade elétrica do silício Concepção de Circuitos Integrados - 12.4 adapted from: Transistor MOS Influência das tensões dos terminais Modo não saturado (linear, resistivo) fonte N+ Ids depende de Vgs e Vds Concepção de Circuitos Integrados - 12.5 adapted from: Vds < Vgs Vt N+ P Transistor MOS Influência das tensões dos terminais Modo saturado pinch-off Vds Vgs - Vt Vds > Vgs Vt fonte N+ N+ Vds P Os elétrons do canal são “injetados” na região de depleção do dreno e acelerados em direção ao dreno A corrente no canal é controlada pela por Vgs e praticamente independente de Vds Com Vds e Vgs fixo Ids depende de : - distância entre fonte e dreno - largura do canal (W) - tensão de threshold Vt - espessura do óxido de gate - constante dielétrica do isolante e - mobilidade do portador µ - temperatura Concepção de Circuitos Integrados - 12.6 adapted from: Transistor MOS Tensão de threshold Vt é a tensão Vgs de um dispositivo MOS abaixo da qual a corrente Ids cai praticamente a zero. Quando ocorre inversão forte. Vt é função de vários parâmetros, dentre os quais: -material condutor da grade -material isolante do gate (dielétrico) e sua espessura -dopagem do canal -concentração de impurezas na interface silício-isolante -tensão entre fonte e substrato Vsb -temperatura (diminui com o aumento de temperatura) tipicamente - 4 a -2 mV /ºC Concepção de Circuitos Integrados - 12.7 adapted from: Transistor MOS Tensão de threshold eox Cox = tox Cox é a capacitância de gate por unidade de área eox = 3,97 eo = 3,5 . 10-13 F/cm (permissividade do óxido) Exemplo: para tox =20 nm(=200Aº) temos que Cox é 1,75 fF/µm2. Concepção de Circuitos Integrados - 12.8 adapted from: Transistor MOS Curvas I-V Ids - corrente de dreno Ids canal N em enriquecimento 0 Vtn Vg s Ids canal N em depleção OBS: como nos transistores de carga (pull-up) de portas lógicas NMOS - Vtn 0 Vg s Concepção de Circuitos Integrados - 12.9 adapted from: Transistor MOS Curvas I-V VDS < VGS -VT ID 2 triodo √ ID VGS = 5V VDS = VGS -VT (mA) Supondo VT = 0.8 v VDS > VGS -VT 0.02 saturação VDS = 4.2 v VGS = 4V VDS = 3.2 v 1 subthreshold current 0.01 VDS = 2.2 v VGS = 3V VDS = 1.2 v VGS = 2V VGS = 1V 0 1 2 3 4 ID em função de VDS 5 VDS (V) 0 2 3 VGS VT1 ID em função de VGS (para VDS = 5V) Região de triodo: o transistor funciona como um resistor controlado por tensão Região de saturação: o transistor funciona como uma fonte de corrente controlada por tensão Concepção de Circuitos Integrados - 12.10 adapted from: Transistor MOS Modelo de Capacitâncias G CGS CGD D S CSB CGB CDB B CGS - Capacitância grade-fonte CGD - Capacitância grade-dreno CSB - Capacitância fonte-substrato (bulk) CDB - Capacitância dreno-substrato (bulk) CGB - Capacitância grade-substrato (bulk) Concepção de Circuitos Integrados - 12.11 adapted from:

Baixar

![Aula 6A Fisica do transistor MOS [Modo de Compatibilidade]](http://s1.livrozilla.com/store/data/001227336_1-79b7f9fd95991a689265ddf6df4744e5-260x520.png)