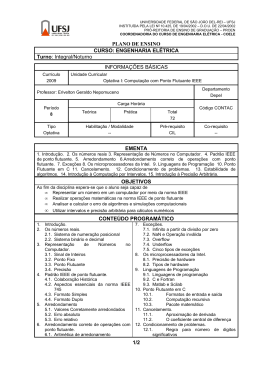

Lista de Exercícios – ACM 1) Neste exercício, você avaliará a diferença de desempenho entre duas arquiteturas de CPU, a CISC (Complex Instruction Set Computing) e a RISC (Reduced Instruction Set Computing). Genericamente falando, as CPUs CISC possuem instruções mais complexas do que as CPUs RISC e, portanto, precisam de menos instruções para realizar as mesmas tarefas. Entretanto, em geral uma instrução CISC, por ser mais complexa, leva mais tempo para ser completada do que uma instrução RISC. Considere que uma determinada tarefa precise de P instruções CISC e 2P instruções RISC, e que uma instrução CISC leva 8T ns (nanossegundos) para ser completada enquanto uma instrução RISC leva 2T ns. Com essas considerações, qual arquitetura apresenta o melhor desempenho? 2) Algumas vezes, a otimização pode melhorar significativamente o desempenho de um sistema computacional. Considere que uma CPU pode realizar uma operação de multiplicação em 10 ns e uma operação de subtração em 1 ns. Quanto tempo a CPU levará para calcular o resultado da equação d = a*b – a*c? Você poderia otimizar a equação de modo que ela levasse menos tempo? 3) Suponha que você trabalhe em uma empresa, e seja o responsável pela aquisição de um novo computador. Imagine que fosse apresentada a você uma lista com contenha muitos computadores a considerar para a compra. Você poderia usar o custo dividido pelo tempo de execução da aplicação a ser mais utilizada pela empresa como métrica para ajudar em sua decisão de compra? E quanto ao custo multiplicado pelo tempo de execução? Se uma das duas fórmulas não puder ser usada, apresente um exemplo simples que demonstre por que não. 4) Queremos comparar dois computadores diferentes: M1 e M2. As seguintes medições foram feitas nesses computadores: Programa 1 2 Tempo em M1 (em seg.) 2,0 5,0 Tempo em M2 (em seg.) 1,5 10,0 Considerando que o custo de M1 é de US$500,00 e de M2 US$800,00, responda: a) Qual computador possui o melhor desempenho para essa carga (workload)? O quanto melhor? b) Que computador é mais produtivo para essa carga (leve em conta o custo)? O quanto mais? 5) No mercado de embutidos, no qual o custo é um fator decisivo, os processadores algumas vezes implementam ponto flutuante apenas por software. Estamos interessados em duas implementações de um computador, uma com e uma sem hardware de ponto flutuante especial. Considere um programa, P, com o seguinte mix de operações: Multiply de ponto flutuante 10% Add de ponto flutuante 15% Divide de ponto flutuante 5% Instruções de inteiros 70% O computador MFP (computador com ponto flutuante) possui hardware de ponto flutuante e, portanto, pode implementar as operações de ponto flutuante diretamente. Ele exige o seguinte número de ciclos de clock para cada classe de instrução: Multiply de ponto flutuante Add de ponto flutuante Divide de ponto flutuante Instruções de inteiros 06 04 20 02 O computador MNFP (computador sem ponto flutuante) não possui qualquer hardware de ponto flutuante e, então, precisa emular as operações de ponto flutuante usando instruções de inteiros. Todas as instruções de inteiros levam 2 ciclos de clock. O número de instruções de inteiros necessário para implementar cada uma das operações de ponto flutuante é o seguinte: Multiply de ponto flutuante Add de ponto flutuante Divide de ponto flutuante 30 20 50 Os dois computadores possuem uma velocidade de clock de 1.000MHz. Encontre os índices de MIPS nativos para ambos os computadores. 6) Se o computador MFP no Exercício 5 precisa de 300 milhões de instruções para esse programa, de quantas instruções de inteiros o computador MNFP precisa para o mesmo programa? 7) Considerando as contagens de instruções do Exercício 5, qual é o tempo de execução (em segundos) para o programa no exercício ser executado no MFP e no MNFP? 8) Você é o diretor de projeto de um novo processador. O projeto do processador e o compilador estão completos e, agora, você precisa decidir entre produzir o projeto atual como está ou gastar mais tempo para melhorá-lo. Você discute esse problema com sua equipe de engenharia de hardware e chega às seguintes opções: a. Deixar o projeto como está. Chame esse computador básico de Mbase. Ele possui uma velocidade de clock de 500MHz e as seguintes medições foram feitas usando um simulador para Mbase: Classe de instrução CPI Freqüência Classe de Instrução A B C D CPI 2 3 3 5 Freqüência 40% 25% 25% 10% b. Otimizar o hardware. A equipe de hardware afirma que pode melhorar o projeto do processador para conferir-lhe uma velocidade de clock de 600MHz. Chame esse computador de Mopt. As seguintes medições foram feitas usando um simulador para Mopt: Classe de instrução CPI Freqüência Classe de Instrução A B C D CPI 2 2 3 4 Freqüência 40% 25% 25% 10% Qual é o CPI para cada computador? 9) escrever quaisquer registradores, que leva o mesmo tempo de uma instrução de inteiros. Considere que o tempo de acesso a unidades de memória leve 200ps, ALU 100ps os e registradores 50ps. Nestes exercícios, encontraremos o índice de desempenho entre uma implementação em que o ciclo de clock é diferente para cada classe de instrução e uma implementação em que todas as instruções possuem o mesmo tempo de ciclo de clock. Considere o seguinte: Todos os loads levam o mesmo tempo e representam 30% das instruções. Todos os stores levam o mesmo tempo e representam 15% das instruções. As instruções no formato R representam 25% do mix. Os branches representam 10% das instruções, enquanto os jumps respondem por 5%. Soma e subtração de ponto flutuante levam o mesmo tempo e, juntas, representam 5% das instruções. Multiplicação e divisão de ponto flutuante levam o mesmo tempo e, juntas, representam 10% das instruções. a) Encontre o tempo para as operações de ponto flutuante. b) Descubra o tempo para o processador com uma extensão fixa de ciclo de clock igual à instrução mais longa. c) Encontre o tempo médio por instrução para o processador com um clock de extensão variável. 10) Descreva as características gerais de um programa que exibiria muito pouca localidade temporal e espacial com relação a buscas de instruções. 11) Descreva as características gerais de um programa que exibiria quantidades muito altas de localidade temporal, mas muito pouca localidade espacial com relação a buscas de instruções. 12) Descreva as características gerais de um programa que exibiria muito pouca localidade temporal, mas quantidades muito altas de localidade espacial com relação a buscas de instruções. 13) Considere uma hierarquia de memória usando uma das três organizações para a memória principal mostradas na figura abaixo. Suponha que o tamanho do bloco da cache é de 16 palavras, que a largura da organização (b) da figura é de quadro palavras e que o número de bancos na organização (c) é quatro. Se a latência da memória principal para um novo acesso é de 10 ciclos de clock de barramento de memória, e o tempo de transferência é de um ciclo de clock de barramento de memória, quais são as penalidades de memória para cada uma dessas organizações? 14) Suponha que um processador com tamanho de bloco de 16 palavras tenha uma taxa de falhas efetiva por instrução de 0,5%. Suponha que o CPI sem perdas de cache seja 1,2. Usando as memórias descritas na figura acima e o exercício anterior, o quanto esse processador é mais rápido usando a memória larga do que usando memórias estreitas ou intercaladas?

Baixar