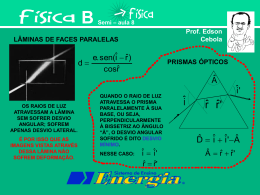

Pipeline

Execução sequencial das instruções

Uma etapa do ciclo de instrução se

inicia após a conclusão da anterior

Uma máquina com este tipo de

execução é chamada de SISD (Single

Instruction Single Data)

Para aumentar a velocidade de execução de

uma instrução, era necessário aumentar o

clock do processador e melhorar a tecnologia

dos semicondutores

As etapas do ciclo de instrução permaneciam

sendo realizadas seqüencialmente

Sobreposição temporal das etapas da

execução de instruções

As etapas de um ciclo de instrução

vão ocorrer simultaneamente, porém

sobre instruções diferentes

Cada uma das etapas do ciclo de

instrução recebe o nome de estágio

Cada estágio é executado por uma

unidade do processador:

◦ Unidade

◦ Unidade

◦ Unidade

◦ Unidade

◦ Unidade

de

de

de

de

de

Busca de Instrução (BI)

Decodificação (D)

Busca de Operandos (BO)

Execução da Instrução (E)

Escrita de Resultados (ER)

Processador

Unidade

De BI

instrução

Unidade

De D

instrução

Unidade

De BO

Unidade

De E

instrução

Unidade

instrução De ER

Existem no pipeline situações em que a

instrução seguinte não pode ser executada

no próximo ciclo de clock: conflitos

Existem três tipos de conflitos:

◦ Conflitos Estruturais

◦ Conflitos de Controle

◦ Conflitos de Dados

Ocorre quando duas instruções estão

em etapas diferentes mas estão

utilizando o mesmo hardware, por

exemplo, a memória

No diagrama anterior ocorrem vários

conflitos para acessar a memória, por

exemplo:

◦ No instante de tempo 5, a instrução 5 está

sendo buscada na memória junto com os

operandos da instrução 3

Conflito

Se a memória for uma só, não é possível

atender as duas requisições ao mesmo

tempo

◦ A memória principal (ou cache) possui somente

uma porta para atendimento de requisições

Nas máquinas modernas existem duas

memórias cache: cache de dados e cache de

instruções

O estágio de busca de instruções irá buscar a

instrução 5 na cache de instruções e ao

mesmo tempo o estágio de busca de

operandos acessa a cache de dados

Problema resolvido (para casos em que temos

cache separadas)

Ocorre quando uma instrução que está

no pipeline é um desvio condicional

Enquanto esta instrução não passar pelo

estágio de execução, não se sabe qual é

a próxima instrução a ser executada

Ocorrerá, então, uma parada no pipeline

(bolha)

◦ Queda no desempenho do pipeline

Para entendermos o que acontece no

pipeline quando uma instrução de desvio é

executada, iremos analisar o trecho de

código a seguir

Considere que o código está armazenado

na memória na ordem ilustrada

Instr.

Instr.

Instr.

Instr.

Instr.

Instr.

Instr.

1

2

3

4

5

6

7

Instr. 8

Instr. 9

Instr. 10

Instr. 11

cin>>x>>valor;

Instrução de

menor = 0;

desvio

maior = 0;

condicional

If (valor< x) {

maior = menor;

Desvio

menor= valor;

cout<< “qualquer coisa”;

}

Fluxo de

else {

execução

menor = maior;

seqüencial

maior = valor;

}

cin>> k;

K++;

A técnica mais utilizada para resolver

o conflito de controle é a predição ou

previsão de desvios

◦ A unidade de busca de instrução tenta

prever se o desvio será tomado ou não

◦ Esta previsão é baseada em uma tabela de

histórico de desvios

A tabela de histórico é uma memória cache

pequena associada ao estágio de busca de

instrução do pipeline e tem cerca de 90 % de

precisão

◦ Esta tabela contém todas as instruções de

desvio de um programa, informando se

houve desvio ou não da última vez que a

instrução foi executada

◦ Se uma instrução de desvio condicional

provocou um desvio da última vez que ela

foi executada, da próxima vez que esta

instrução for executada, a unidade de

busca irá considerar que haverá desvio

novamente

int F, N;

F = 1;

cin >> N;

Em caso de estruturas

de repetição,

é considerado que sempre

ocorrerá desvio

If (N = = 0)

cout << “Fatorial de 0 é 1”;

else {

F = N;

while (N !=1){

F = F * (N-1);

N = N –1;

}

cout << “Fatorial de N é”, F;

}

Desvio

Fluxo de

execução

seqüencial

Quando a previsão está correta, o pipeline

prossegue na velocidade máxima

Quando a previsão falha, o pipeline é

esvaziado e as instruções corretas são

buscadas

A execução de uma instrução depende do

resultado de outra que ainda está no pipeline

Exemplo: suponha que tenhamos uma

instrução de carga imediatamente seguida

por uma instrução de subtração que utilize o

resultado da carga

LDA Op

ACC

(OP)

SUB Op

ACC

ACC - (OP)

A operação SUB

precisa do

conteúdo do

ACC no 4o

estágio do

pipeline

A operação LDA

só escreve o

resultado no ACC

no 5o estágio do

pipeline

Neste caso vai ocorrer uma bolha no pipeline

Bolha

A solução para resolver este conflito é a

reordenação das instruções

◦ As instruções que não estão conflitando são

adiantadas

Reordenação

LDA Op

LDA Op

SUB Op

GET Op

GET Op

SUB Op

Baixar