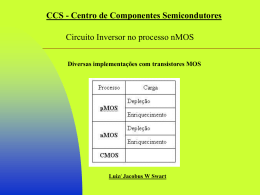

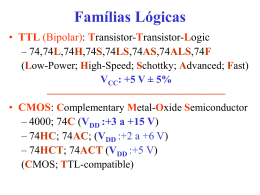

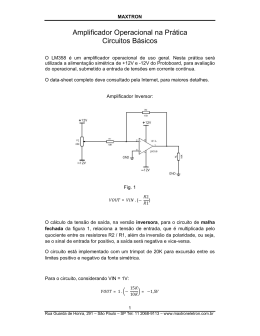

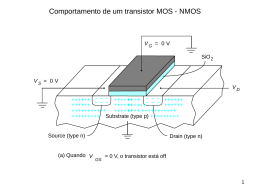

Tecnologias de Circuitos Integrados Tecnologias de Circuitos Integrados MOS-CMOS MOSFET (Metal Oxide Silicon Field Effect Field) – nMOS (N-type MOS) – pMOS (P-type MOS) – CMOS (Complementary - type MOS) Manoel Eusebio de Lima Greco-CIn-UFPE Transistor nMOS Transistor nMOS Características: – O tipo nMOS é composto por substrato de silício do tipo p, fracamente dopada, e duas áreas (drain e source) do tipo n fortemente dopadas. – A difusão no silício é feita com a adoção de elementos doadores de elétrons, como Arsênio e Fósforo. – As cargas majoritárias nos transistores tipo nMOS são elétrons – Este tipo de transistor conduz o sinal “0” lógico forte e o sinal “1” lógico fraco. Cristal de Germânio c/impurezas doadoras Polisilí Polisilício Difusão Gate (polisilí polisilício) cio) Dreno (difusão) difusão Fonte (difusão) difusão Elemento dopante (5 elé elétrons de valência Sb – Antimônio, Fósforo, Arsênio) 5 condutores W = comprimento do canal L = tamanho do canal elé elétron livre Sb Transistor nMOS Transistor pMOS Um transistor nMOS Vista em corte Vista de cima Óxido de Silício metal Polisilício metal contato Características: – O tipo pMOS é composto por substrato de silício do tipo n-well, fracamente dopada, e duas áreas (drain e source) do tipo p fortemente dopadas. – A difusão no silício é feita com a adoção de elementos doadores de buracos (falta de elétrons), com o Índio, Boro. – As cargas majoritárias nos transistores tipo pMOS são buracos. – Este tipo de transistor conduz o sinal “1” lógico forte e o sinal “0” lógico fraco. Cristal de Germânio c/impurezas aceitadoras Elemento dopante (3 elé elétrons de valência InIn-Indium, Indium, Boro) contato buraco Source gate drain 3 In simbologia 1 1 Transistor pMOS Transistor nMOS contato p-MOS - tipo de transistor MOS composto de um moderado substrato de silício tipo n com duas áreas de difusão fortemente dopadas tipo p (p+) (fonte e dreno). difusão difusão Vgs nMOS + - Capacitor MOS – modos de operação Vgs cria o canal • Depleç Depleção • Acumulaç Acumulação + - • Inversão Transistor nMOS - Funcionamento Transistor nMOS - Funcionamento • Transistor polarizado sem condução de corrente elétrica, na região de corte Vgs = 0 V Vth (tensão de limiar) é a tensão na qual o dispositivo MOS começ começa a conduzir (“ (“turn on” on”). Vds = 0 V •Transistor na região linear ou resistiva * Vtn ≅ 0.2VDD Vds < Vgs - Vtn - fraca camada de inversão no canal - Ids depende de Vgs e Vds Vds é a tensão entre o dreno e a fonte do dispositivo. -sem camada de inversão no canal - Ids = 0 fonte dreno Ids aumenta com Vds (similar a um resistor linear) 2 2 Transistor nMOS - Funcionamento Transistor nMOS - Funcionamento •Transistor na região de saturação Vds > Vgs – Vtn, Vgd < Vth (tensão de limiar) Ids aumenta com Vds (similar a um resistor linear) - forte camada de inversão no canal - Ids independe de Vds, a corrente satura (fonte de corrente) corrente) •Corrente de avalanche •O canal é estrangulado canal Eletrons fluindo através de um transistor de sílicio http://researchweb.watson.ibm.com/resources/press/strainedsilicon/ Caracterí Características Tensão - Corrente (VdsVds-Ids) Ids) Transistor MOS - operação Corte – Se Vgs < Vt, então Ids = 0 tn, Linear – Se Vds < ( Vgs-Vt), então Ids depende dos valores Vds e Vgs tn Região linear Região de saturaç saturação tn tn Saturado – Se Vds > (Vgs-Vt), então Ids não depende de Vds. Ids é essencialmente constante. tn tn tn Região corte Caracterí Características de conduç condução de transistores MOS (alta) Transistores MOS vistos como Switches (depleção) > > 3 3 Transistor nMOS Fabricação de Circuitos VLSI Criação Definir Etch (produzir o desenho do circuito desejado através de • Passos simplificados na confecç confecção do SiO2 máscaras) Pastilhas de silício Foto-resistor SiO2 Formação de material por deposição, difusão ou implantação Luz UV Máscara de vidro Máscara (molde) Foto-resistor SiO2 Definição dos circuitos por litografia 8 a 10 interações Etch Transistor nMOS SiO2 Camada fina de óxido de silício Oxidação do gate Substrato de silício Características elétricas da tecnologia MOS Poli-silício molde do Poli-silício Difusão ou implante Cortes de contato Circuitos lógicos MOS dissipam uma pequena quantidade de potência em função das grandes resistências existentes nos dispositivos MOSFET. Vdd=+5V Difusão de impurezas Q1 (depletion) depletion) Id SiO2 por deposição Vin Contatos de alumínio Vantagens da tecnologia MOS Simplicidade e baixo custo da fabricação dos transistores. Tamanho extremanente pequeno quando comparado a tecnologias tais como TTL e ECL. Baixo consumo elétrico. Possuem uma melhor margem de ruído que bipolar. Fan-out bem maior que circuitos bipolares. Grande faixa de alimentação (3 a 15V). Todas as vantagens acima fazem com que seja possível acomodar em circuitos MOS uma grande quantidade de dispositivos. Id = Vdd Ron(Q1)+ Roff(Q2) (Q2) ≅ 0.05nA Ron(Q1)+Roff Potência Pd = 0.25 nW Q2 (enhancement) enhancement) GND molde da camada de alumínio Vin = 0V a) Q1 - Ron(Q1) Ron(Q1) = 100 Kohms b) Q2 - Roff(Q2) Roff(Q2) Vin = +5V a) Q1 - Ron(Q1) Ron(Q1) = 100 Kohms b) Q2 - Ron(Q2) Ron(Q2) = 1 Kohms Id = Vdd Ron(Q1)+ Ron(Q2) (Q2) ≅ 50 µ A Ron(Q1)+Ron Potência Pd = 0.25 mW Desvantagens da tecnologia MOS Baixa velocidade de operação quando comparada as famílias bipolares. Este fenômeno se deve a dois fatores: – Alta resistência de saída no estado lógico 1(alto). – Alta carga capacitiva normalmente presente nas entradas dos circuitos lógicos MOS . 4 4 Características elétricas da tecnologia CMOS Inversor CMOS Vcc Tecnologia CMOS é composta por dois tipos de transistores, um do tipo NMOS e outro do tipo PMOS. CMOS é mais rápido e consome menos potência que outros elementos da família MOS. Inversor CMOS Vdd Vin Vout Vdd Vout pMOS Vin (gate) Vss P-switch - pullpull-up Vin Layout – vista de cima Vout Vin 0 1 N-switch - pullpull-down Vout 1 0 nMOS Terra Vss Inversor CMOS Operação de um inversor CMOS Vdd 1- Vin = Vdd Q1 Aná Análise do circuito: Vdd=+5V Vdd=+5V Ids Roff Ron Vout 0V Característica estática de um inversor CMOS Vin Id Cload Q2 Vout Vss Cálculo de Vout Vdd = Ids(Roff+Ron) Vdd = Ids.Roff+Ids.Ron Vdd = Ids.Roff+Vout Vout = Vdd-Ids.Roff ≅ => => => 0V Ron < 1 Kohms Roff ≅ 1010Kohms Ids é pequeno, mas Roff é bastante grande Operação de um inversor CMOS Vdd 2- Vin = 0V Q1 Aná Análise do circuito: Vdd=+5V Vdd=+5V Ids Ron Roff Vout • Note que Vh = 5V, VL = 0V, e que Ids = 0A. • Isto significa que não existe praticamente dissipação de potência. 0V Vin Id Q2 Vout Vss Cload Cálculo de Vout Vdd = Ids(Roff+Ron) => Vdd = Ids.Roff+Ids.Ron => Vdd = Vout+Ids.Ron => Vout = Vdd-Ids.Ron ≅ Vdd=5V Ron < 1 Kohms Roff ≅ 1010Kohms Ids é muito pequeno 5 5 Característica estática de um inversor CMOS Operação de um inversor CMOS Vout P “on” on” N “off” off” P “on” on” N “on” on” Vdd P “off” off” N “on” on” Idsn = - Idsp 0.5 Vdd • Note que Vh = 5V, VL = 0V, e que Ids = 0A. • Isto significa que não existe praticamente dissipação de potência. 0 Vth 0.5Vdd Vdd+ Vdd+Vtp Vin Características elétricas da tecnologia CMOS A dissipação de potência em circuitos CMOS embora seja muito pequena nas condições dc, aumentam com a freqüência de operação do circuito. Em altas freqüências os picos de corrente no chaveamento dos transistores tendem a ocorrer com mais freqüência e a corrente média fornecida por Vdd aumenta. Vdd Id (reversa) Id Cload Q1 Lógica CMOS Vin Vout Q2 Id Vin Vout Vss Podemos constatar que em alta freqü freqüências CMOS começ começa a perder vantagens sobre as outras famí famílias ló lógicas NAND CMOS Lógica Combinacional Porta saí saída NAND A 0 0 1 1 1 1 1 0 B Vcc (‘1’) Porta NAND de n-entradas Vcc (A+B) P Vcc P B A saída C Saída Dual Ló Lógico n Saída A N B A (A B) A N B GND (‘0’) C B GND n GND 6 6 NOR CMOS Lógica Combinacional saí saída Porta NOR 0 A 0 1 1 0 0 0 B 1 Vcc (‘1’) Vcc Vcc P (A B) n A A P B B Dual Ló Lógico saída N N A saída B GND (A+B) A Saída C B n C GND GND (‘0’) Transmission Gate Transmission gate Análise do transistor tipo N como “pass transistor” Análise do transistor tipo P como “pass transistor” Análise do transmission Gate “CMOS” CanalCanal-N Vout Vin CanalCanal-P Transistor tipo N como “pass transistor” transistor” Transistor tipo P como “pass transistor” transistor” Vgs Vin Vout Canal-N Vin CI Condição Inicial Vout=0V (capacitor descarregado) φ = ´0´ , Vgs=0V, assim Ids = 0 mA independente do valor de Vin Quando φ= ´1´ , Vin = ´1 ´ e Vgs= Vdd o transistor começa a conduzir e a carregar o capacitor até Vout ~ Vdd. Como Vin > Vout, Ids flui da esquerda para a direita. Vout tende a (Vdd - Vth) e o transistor para a região de corte(turn off), com Vgs < Vth. O capacitor Cl permanecerá carregado quando φ = ´0´, portanto Vout = Vdd-Vth. Conclusão: A transmissão do nível logico ´1´ é degenerado quando ele passa através de um transistor tipo n-MOS, ou seja Vout ≠ Vdd(Vin). No entanto, quando Vin=´0´ , Vgs=Vdd e Vout=´1´ o capacitor descarrega através do transistor até Vout = 0V, desde que a relação Vgs>Vth será sempre verdade. Ou seja, Transistor tipo n-Mos é apropriado para transmitir nível lógico ‘0’. Canal-P Vgs Vout CI Condição Inicial Vout=0(capacitor descarregado) φ = ´1´ , Vgs=Vdd, assim Ids = 0 mA independente do valor de Vin. Quando φ= ´0´ , Vin = ´1´ o transistor começa a conduzir e a carregar o capacitor até Vout =Vdd. Como Vin > Vout, Ids flui da esquerda para a direita. Vout vai para Vdd, sem degradação do sinal. O capacitor Cl permanecerá carregado quando φ = ´1´. Conclusão: A transmissão do nível logico ´1´ não é degenerado quando ele passa através de um transistor tipo p-MOS, ou seja Vout = Vdd(Vin). No entanto, quando Vin=´0´ e Vout=´1´ o capacitor descarrega através do transistor até Vout = |Vtp|, ponto no qual o transistor para de conduzir. Ou seja, um transistor tipo p-MOS degrada o nível lógico ´0´. 7 7 Aplicação com Flip-Flops Multiplixador analógio CMOS (8 canais) Chaves CMOS/Transmission gates Flip-Flop tipo D IN Q Q LD LD LD = ‘1’ - carrega IN em Q LD = ‘0’ - manté mantém Q 8 8

Baixar