TRANSISTORES DE EFEITO

DE CAMPO MOS - MOSFETs

FUNDAMENTOS

12 h

ESTRUTURA DE UM

TRANSISTOR NMOS

Na figura a seguir é mostrada a estrutura de

um transistor MOSFET (“Metal-Oxide

Semiconductor Field Effect Transistor) tipo

enriquecimento canal n.

Um transistor NMOS possui 4 pinos: Porta

(G-Gate) Dreno (D-Drain) Fonte (S-Source)

Substrato (B-Body).

O isolante na porta, faz com que a corrente

de porta seja muito pequena, da ordem de

10-15 A.

2

ESTRUTURA DE UM

TRANSISTOR MOSFET

3

ESTRUTURA DE UM

TRANSISTOR NMOS

O substrato forma duas junções PN com a

fonte e com o dreno, que em operação

normal são mantidas reversamente

polarizadas, conectando-se o substrato à

fonte.

A região de canal, situada logo abaixo da

porta, é caracterizada por um comprimento

L, tipicamente de 1 a 10 μm, e por uma

largura W, tipicamente de 2 a 500 μm.

4

FUNCIONAMENTO DE UM

TRANSISTOR NMOS

Um transistor NMOS é um dispositivo

simétrico, podendo o dreno ser trocado com

a fonte.

Sem a aplicação de tensão vGS>0, existe

uma resistência entre fonte e dreno da

ordem de 1012 Ω.

Por outro lado, a aplicação de uma tensão

vGS>0 faz o aparecimento de um canal n,

como mostra a figura a seguir.

5

ESTRUTURA DE UM

TRANSISTOR MOSFET

6

FUNCIONAMENTO DE UM

TRANSISTOR NMOS

A tensão vGS necessária para a formação do

canal de condução é denominada de tensão

de limiar Vt, tipicamente entre 1 a 3 V.

A aplicação de tensão vDS>0 possibilita a

existência de corrente entre dreno e fonte iD,

como mostrado a seguir.

7

FUNCIONAMENTO DE UM

TRANSISTOR NMOS

8

DEPENDÊNCIA DE Id com

vDS PEQUENO e vGS

A condutância do canal é proporcional à

diferença de tensão vGS-Vt.

Assim, quanto maior for a diferença vGS-Vt,

maior será ID.

E também, quanto maior for vDS, maior será

ID, já que esta corrente é produzida por

aquela tensão.

A próxima figura mostra estas duas

dependências.

9

DEPENDÊNCIA DE Id com

vDS PEQUENO e vGS

10

OPERAÇÃO COM vDS

GRANDE

Observando a próxima figura, concluímos

que o canal não mantém a sua profundidade

constante com o aumento de vDS.

Isto deve-se ao fato da tensão variar de vGS

entre porta e fonte a vGS-vDS entre porta e

dreno.

Assim, à medida que vDS aumenta, o canal

torna-se mais estreito no dreno, até o

momento em que o canal é estrangulado

(“pinched-off”).

11

OPERAÇÃO COM VDS

GRANDE

12

OPERAÇÃO COM VDS

GRANDE

Neste momento, a resistência do canal

torna-se infinita, e portanto a corrente ID

torna-se constante em função de vDS.

A próxima figura, ilustra as duas regiões de

funcionamento de um transistor NMOS:

–

–

Região Triodo

Região de Saturação (não confundir com a

saturação do transistor bipolar!)

A tensão vDS em que ocorre a saturação:

vDSsat=vGS-Vt

13

REGIÃO TRIODO E DE

SATURAÇÃO

14

DERIVAÇÃO DA RELAÇÃO

ID VERSUS VDS

Vamos considerar inicialmente que vGS>Vt e que o

transistor opera na região triodo, ou seja que

vDS<vGS-Vt. Neste caso, o formato do canal é

mostrado a seguir.

Considere uma região infinitesimal de

comprimento dx. Portanto a carga nesta região,

vale:

δq(x)=-CoxWδx[vGS-v(x)-Vt]

onde Cox é a capacitância por área formado pelo

eletrodo de porta e o canal, W é a largura do

transistor e v(x) é a tensão neste ponto do canal.

15

DERIVAÇÃO DA RELAÇÃO

iD VERSUS vDS

16

DERIVAÇÃO DA RELAÇÃO

iD VERSUS vDS

Como o dielétrico de Cox é formado pela camada de

óxido, a capacitância por área é dada por:

Cox=εox/tox

onde εox é a permissividade e tox é a espessura do

dielétrico.

A tensão vDS produz um campo elétrico,

E(x)=-δv(x)/δx

E portanto, a velocidade de um elétron:

δx/δt=-μnE(x)

δx/δt=μnδv(x)/δx

onde μn é a mobilidade dos elétrons.

17

DERIVAÇÃO DA RELAÇÃO

iD VERSUS vDS

O produto de δq(x)/δx por δx/δt nos fornece

a corrente de deriva, que é igual a -iD:

iD=μnCoxW[vGS-v(x)-Vt]δv(x)/δx

Integrando ambos os lados de x=0 até x=L,

∫0LiDδx=∫0vDSμnCoxW[vGS-v(x)-Vt]δv(x)

Que resulta em

iD=μnCox(W/L)[(vGS-Vt)vDS-vDS2/2]

expressão válida para a região triodo.

18

DERIVAÇÃO DA RELAÇÃO

iD VERSUS vDS

Para a fronteira da região de saturação

vDS=vGS-Vt, e portanto:

iD=μnCox(W/L)(vGS-Vt)2/2

O produto kn’=μnCox é denominado de

parâmetro de transcondutância do processo

e tem dimensão A/V2.

A razão W/L é conhecida como razão de

aspecto do transistor.

19

MOSFET CANAL p

O MOSFET tipo enriquecimento canal p

opera do mesmo modo que o dispositivo

canal n, exceto que as tensões vGS, vDS e Vt

são negativas.

Além disso, a corrente de dreno entra pelo

terminal de fonte e sai pelo dreno.

A tecnologia CMOS (MOS Complementar)

utiliza transistores PMOS e NMOS.

20

CMOS

21

SÍMBOLO MOSFET CANAL

n

22

RESUMO DA

CARACTERÍSTICA iD x vDS

A próxima figura ilustra as 3 regiões de um

NMOS: corte, triodo e saturação.

Na região de corte

vGS<Vt

Na região triodo, definida por:

vGS>Vt e vDS<vGS-Vt

Temos uma resistência:

rDS=vDS/iD=[kn’(W/L)(vGS-Vt)]-1

onde vDS<<1.

23

RESUMO DA

CARACTERÍSTICA iD x vDS

24

REGIÃO DE SATURAÇÃO

Já sabemos que na região de saturação:

iD=(kn’/2)(W/L)(vGS-Vt)2

cuja corrente não depende de vDS, conforme

mostra a figura a seguir.

25

REGIÃO DE SATURAÇÃO

26

MODELO PARA GRANDES SINAIS

NA REGIÃO DE SATURAÇÃO

27

NÍVEIS DE TENSÃO PARA REGIÃO

TRIODO E DE SATURAÇÃO

28

RESISTÊNCIA DE SAÍDA NA

SATURAÇÃO

A próxima figura mostra a variação do

comprimento do canal com a tensão vDS.

Por sua vez, a diminuição no comprimento

do canal, pode ser modelado como:

iD=(kn’/2)[W/(L-ΔL)](vGS-Vt)2

Como ΔL<<L, temos que

iD≈(kn’/2)W/L(1+ΔL/L)(vGS-Vt)2

29

RESISTÊNCIA DE SAÍDA NA

SATURAÇÃO

Assumindo que ΔL=λ'vDS, temos que

iD=(kn’/2)(W/L)(1+λ'vDS/L)(vGS-Vt)2

Chamando λ'/L=λ=1/VA, temos

iD=(kn’/2)(W/L)(vGS-Vt)2(1+vDS/VA)

onde VA é denominada tensão de Early e

tipicamente varia de 30 a 200 V.

30

VARIAÇÃO DO PONTO DE

ESTRANGULAMENTO

31

RESISTÊNCIA DE SAÍDA NA

SATURAÇÃO

32

RESISTÊNCIA DE SAÍDA NA

SATURAÇÃO

A resistência para pequenos sinais com o

transistor na saturação é dada por:

ro=(δiD/δvDS)-1=[(kn’/2)(W/L)(vGS-Vt)2/VA]1

Que pode ser aproximado por:

ro=VA/ID=1/(λID)

33

MODELO PARA GRANDES SINAIS

NA SATURAÇÃO INCLUINDO ro

34

SÍMBOLO E

CARACTERÍSTICAS PMOS

35

CARACTERÍSTICAS PMOS

Para o transistor PMOS, vGS<0, vDS<0 e

Vt<0.

Podemos fazer um raciocínio equivalente,

trocando a ordem dos índices, ou seja de vGS

para vSG, e assim por diante. Neste caso, as

tensões permaneceriam positivas.

Assim, o transistor estará em corte, se

vSG<|Vt|

E caso contrário, um canal será formado.

36

NÍVEIS DE TENSÃO PMOS

37

EFEITO DO CORPO

Quando o corpo é conectado à fonte, a junção

entre fonte e substrato trabalha com uma

tensão de polarização reversa constante. Neste

caso, a existência do corpo pode ser ignorada.

Quando o corpo é conectado não na fonte, mas

no potencial mais negativo (canal n) do

circuito para que a junção fonte-corpo trabalhe

reversamente polarizada, temos que o sinal na

fonte irá produzir uma variação na tensão

reversa desta junção, que por sua vez mudará a

profundidade do canal.

38

EFEITO DO CORPO

Pode-se mostrar que a tensão VSB produz

uma mudança na tensão de limiar,

Vt=Vt0+γ[√(2Φf+VSB)-√(2Φf)]

onde Vt0 é a tensão de limiar para VSB=0, Φf

é um parâmetro físico que vale Φf≈0,6 V, e

γ é o parâmetro de efeito de corpo γ≈0,5

V1/2.

39

POLARIZAÇÃO DE

MOSFETs – EXEMPLO 4.1

Polarize o NMOS a seguir, tal que ID=0,4 mA,

VD=0,5 V. O transistor tem parâmetros Vt=0,7 V,

kn’=μnCox=100 μA/V2, L=1 μm, W=32 μm, VA=∞.

Solução: Como vDG=0,5 V, o transistor está

operando na saturação, e portanto:

iD=(kn’/2)(W/L)(vGS-Vt)2

que resolvendo, temos que vGS=0,2 V ou vGS=1,2

V, onde a primeira solução não tem significado

físico.

40

EXEMPLO 4.1

41

EXEMPLO 4.1

Portanto,

RS=(VS-VSS)/ID=(-1,2+2,5)/0,4x10-3=3,3 kΩ

Além disso,

RD=(VDD-VD)/ID=(2,5-0,5)/0,4x10-3=5 kΩ

42

EXEMPLO 4.2

Determine R e VD no circuito a seguir, tal que

ID=80 μA. O transistor tem parâmetros Vt=0,6 V,

kn’=μnCox=200 μA/V2, L=0,8 μm, W=4 μm,

VA=∞.

Solução: Como vDG=0, o transistor está operação

na saturação, e portanto:

iD=(kn’/2)(W/L)(vGS-Vt)2

que resolvendo, temos que vGS=0,2 V ou vGS=1 V,

onde a primeira solução não tem significado

físico.

43

EXEMPLO 4.2

44

EXEMPLO 4.2

Logo,

VD=1 V

E portanto,

R=(VDD-VD)/ID=(3-1)/80x10-6=25 kΩ

45

EXEMPLO 4.3

Projete o circuito a seguir, tal que VD=0,1 V. Qual

é a resistência entre dreno e fonte? O transistor

tem parâmetros Vt=1 V, kn’W/L=1 mA/V2, VA=∞.

Solução: Como VDS<VGS-Vt, o transistor está

operação na região triodo, e portanto:

ID=kn’(W/L)[(VGS-Vt)VDS-VDS2/2]=0,395 mA

Portanto,

RD=(VDD-VD)/ID=(5-0,1)/0,395x10-3=12,4 kΩ

A resistência entre dreno e fonte é dada por:

rDS=VDS/ID=0,1/0,395x10-3=253 Ω

46

EXEMPLO 4.3

47

EXEMPLO 4.4

Analise o circuito a seguir. O transistor tem

parâmetros Vt=1 V, kn’W/L=1 mA/V2, VA=∞.

Solução: Utilizando o divisor de tensão, temos

que

VG=VDDRG2/(RG1+RG2)=5 V

A tensão no terminal fonte vale

VS=RSID

Supondo o transistor na saturação:

ID=(kn’/2)(W/L)(VGS-Vt)2=0,5x10-3(46x103ID)2

48

EXEMPLO 4.4

49

EXEMPLO 4.4

Que resolvida, fornece 2 valores: ID=0,5 mA e

0,89 mA, onde a segunda resposta produz

tensão de fonte sem significado físico.

Portanto,

ID=0,5 mA

VS=RSID=3 V

VGS=5-3=2 V

VD=VDD-RDID=10-6x103x0,5x10-3=7 V

Como VDS>VGS-Vt, o transistor encontra-se

realmente na região de saturação.

50

EXEMPLO 4.5

Projete o circuito a seguir, e determine o

maior valor de RD para que o transistor

opere na saturação, com ID=0,5 mA, VD=3

V. O transistor PMOS tem parâmetros

Vt=-1 V, kp’W/L=1 mA/V2, VA=∞.

Solução: Como o transistor encontra-se em

saturação:

ID=(kp’/2)(W/L)(VSG-Vt)2

que fornece VSG=2 V como única solução.

51

EXEMPLO 4.5

52

EXEMPLO 4.5

Portanto,

VG=VS-VSG=5-2=3 V

Usando que RG=RG1+RG2=5 MΩ, temos

que:

RG1=VG(RG1+RG2)/VDD=2 MΩ

RG2=RG-RG1=3 MΩ

E portanto,

RD=VD/ID=3/(0,5x10-3)=6 kΩ

53

EXEMPLO 4.5

A tensão mínima de saturação ocorre

quando VSD=VSG-Vt, e portanto,

VD=VG+Vt=4 V

E portanto,

RD=VD/ID=4/(0,5x10-3)=8 kΩ

54

CARACTERÍSTICA DE

TRANSFERÊNCIA

O circuito a seguir é denominado de fonte

comum. A partir do circuito podemos

escrever a reta de carga do circuito:

vO=vDS=VDD-RDID

Assim, uma variação em vI=vGS dá origem a

uma variação em ID, que por sua vez

proporciona uma variação em vO=vDS, o que

nos permite obter a curva vO x vI.

55

CARACTERÍSTICA DE

TRANSFERÊNCIA

56

CARACTERÍSTICA DE

TRANSFERÊNCIA

57

CARACTERÍSTICA DE

TRANSFERÊNCIA

Para vI≤Vt, temos que o transistor está

cortado e vO=VDD. Um aumento na tensão

de entrada leva o transistor inicialmente à

saturação. Se continuarmos a aumentar a

tensão de entrada, o transistor irá para a

região triodo. A tensão de saída em que isto

ocorre é dada por:

vO=vI-Vt

58

CARACTERÍSTICA DE

TRANSFERÊNCIA

Continuando a aumentar a tensão de

entrada, a tensão de saída continua a

diminuir na região triodo, tal que se vI=VDD,

então vO≈0.

59

MOSFET COMO CHAVE

Para vI=0, temos que vO=VDD. Por outro

lado, para vI=VDD, temos que vO≈0, o que

sugere que um transistor MOSFET na

configuração fonte comum tem um

funcionamento similar a um inversor lógico

com níveis lógicos dados por 0 e VDD.

60

MOSFET COMO

AMPLIFICADOR

O trecho AB da curva vOxvI, que

corresponde ao MOSFET saturado, é o mais

linear e com grande derivada.

O ganho do amplificador é dado por:

Av=dvO/dvI

para vI=VIQ

onde VIQ é a tensão de polarização de

entrada.

Para evitar distorção, a variação do sinal de

entrada deve se restringir à região linear.

61

EXEMPLO 4.7

Considere a configuração fonte comum com

kn’W/L=1 mA/V2, Vt=1 V, RD=18 kΩ,

VDD=10 V. Determine os valores dos pontos

notáveis da curva vOxvI.

O ponto X é dado por vI=0 V e vO=10 V.

O ponto A é dado por vI=1 V e vO=10 V.

Para o ponto B temos que:

iD=(kn’/2)(W/L)(vI-Vt)2 e vO=VDD-RDiD

62

EXEMPLO 4.7

De onde tiramos que:

vO=VDD-RD(kn’/2)(W/L)(vI-Vt)2

Além disso,

vO=vI-Vt

Substituindo os valores temos que vI=2 V e

vO=1 V.

63

EXEMPLO 4.7

Para o ponto C temos que:

iD=(kn’/2)(W/L)[(vI-Vt)vO-vO2/2] e

vO=VDD-RDiD

Desprezando o termo vO2/2, tiramos que:

vO=VDD/[1+RD(kn’/2)(W/L)(vI-Vt)]

Substituindo os valores temos que vI=10 V

e vO=0,06 V.

64

POLARIZAÇÃO DE

AMPLIFICADORES MOS

No modo de saturação a relação entre a

corrente de dreno e a tensão porta fonte é

dada por:

iD=μnCox(W/L)(vGS-Vt)2/2

Os parâmetros μn e Vt são muito

dependentes da temperatura e os parâmetros

Cox, Vt, W e L variam muito de transistor

para transistor.

Qualquer polarização impondo uma tensão

vGS constante não terá bom resultado.

65

POLARIZAÇÃO DE

AMPLIFICADORES MOS

O esquema a seguir apresenta uma

polarização muito mais estável, visto que o

resistor de emissor proporciona uma

realimentação negativa. Do circuito,

VG=VGS+IDRD

Se por algum motivo ID subir, então VGS

terá que cair, pois VG é constante. Assim, se

VGS cair, então ID cairá, de acordo com a

equação de saturação IDxVGS.

66

POLARIZAÇÃO DE

AMPLIFICADORES MOS

67

POLARIZAÇÃO DE

AMPLIFICADORES MOS

A próxima figura ilustra 4 configurações

para polarização de um NMOS.

Para o caso de fonte de alimentação única o

primeiro e o quarto circuito podem ser

empregados.

Para o caso de duas fontes de alimentação, a

segunda e terceira configurações podem ser

utilizadas.

68

POLARIZAÇÃO DE

AMPLIFICADORES MOS

69

POLARIZAÇÃO DE MOS EM

CIs

Em circuitos integrados resistores são

implementados usando transistores MOS.

Outro ponto a ser evitado em CIs é o uso de

capacitores de acoplamento, visto que

somente se consegue implementar

capacitores de alguns pF.

70

POLARIZAÇÃO DE MOS EM

CIs

A próxima figura ilustra uma fonte de

corrente utilizando MOSFETs.

O transistor Q1 por apresentar VDS1=VGS1

está saturado, e portanto

ID1=(kn’/2)(W/L)1(VGS1-Vt)2

Além disso,

ID1=IREF=(VDD-VGS1)/R

71

POLARIZAÇÃO DE MOS EM

CIs

72

POLARIZAÇÃO DE MOS EM

CIs

Como VGS2 é igual a VGS1,

IO=ID2=(kn’/2)(W/L)2(VGS2-Vt)2

Portanto,

IO/IREF=(W/L)2/(W/L)1

Esta configuração recebe o nome de espelho

de corrente. Para que Q2 trabalhe saturado:

VO≥VGS2-Vt

73

EXEMPLO 4.8

Projete o espelho de corrente para que

IO=100 μA, onde VDD=5 V e IREF=100 μA.

Os transistores têm L=10 μm, W=100 μm,

Vt=1 V, kn’=20 μA/V2, VA=100 V.

Qual o menor valor possível de VO?

Determine a resistência de saída.

Obtenha a mudança em IO, se a tensão de

saída mudar de 3 V.

74

EXEMPLO 4.8

A corrente de dreno de Q1 é dada por:

ID=IREF=(kn’/2)(W/L) (VGS-Vt)2=100x10-6

de onde obtemos que VGS=2 V.

Portanto,

R=(VDD-VGS)/ID=(5-2)/100x10-6=30 kΩ

O valor mínimo de VO vale:

Vomin=VGS-Vt=2-1=1 V

75

EXEMPLO 4.8

A resistência de saída é dada por:

ro=VA/ID=100/100x10-6=1 MΩ

A variação da corrente é dada por:

ΔIO=ΔVO/ro=3/106=3 μA

76

CIRCUITO GUIA DE

CORRENTE

77

MOSFET COMO

AMPLIFICADOR

Considere o MOSFET como amplificador a

seguir.

O transistor polarizado opera na região de

saturação, portanto,

iD=(kn’/2)(W/L)(vGS-Vt)2

A tensão no dreno é dada por:

vD=VDD-RDiD

Para garantir saturação

vDS>vGS-Vt

78

MOSFET COMO

AMPLIFICADOR

79

MOSFET COMO

AMPLIFICADOR

Considerando a aplicação de sinal na

entrada:

vGS=VGS+vgs

Temos que

iD+id=(kn’/2)(W/L)(VGS+vgs-Vt)2

=(kn’/2)(W/L)[(VGS-Vt)2+vgs2+2(VGS-Vt)vgs]

Para que o termo de sinal quadrático seja

desprezível, temos que:

vgs<<2(VGS-Vt)

80

MOSFET COMO

AMPLIFICADOR

Desprezando o termo quadrático temos que

a corrente de sinal:

id=kn’(W/L)(VGS-Vt)vgs

Portanto, a transcondutância do MOSFET é

dada por

gm=id/vgs=kn’(W/L)(VGS-Vt)

cuja interpretação é mostrada na figura a

seguir.

81

MOSFET COMO

AMPLIFICADOR

82

GANHO DE TENSÃO

Utilizando que

vD+vd=VDD-RD(ID+id)

Portanto,

vd=-RDid

Ou ainda que,

vd/vgs=-gmRD

A interpretação do ganho é mostrada a

seguir.

83

GANHO DE TENSÃO

84

MODELO DE PEQUENOS

SINAIS

85

TRANSCONDUTÂNCIA

Sabemos que a transcondutância é dada por:

gm=kn’(W/L)(VGS-Vt)

Por outro lado, usando a expressão da

corrente de dreno:

(VGS-Vt)=√[2ID/kn’(W/L)]

Portanto,

gm=√2kn’√(W/L)√ID

Em geral, a transcondutância de um

MOSFET é bem menor que a de um bipolar

86

EXEMPLO 4.9

Determine o ganho de tensão e a resistência

de entrada, para um transistor NMOS tipo

enriquecimento que tem Vt=1,5 V,

kn’W/L=0,25 mA/V2 e VA=50 V.

Solução: Iniciando pela polarização,

supondo região de saturação:

ID=(kn’/2)(W/L)(VGS-Vt)2

Além disso, como não há corrente em RG, a

tensão VD=VG, ou seja VDS=VGS.

87

EXEMPLO 4.9

88

EXEMPLO 4.9

Além disso,

VDS=VDD-RDID

Resolvendo este sistema de duas equações,

temos que a única solução aceitável é:

ID=1,06 mA, VG=VD=4,4 V

Portanto, a transcondutância vale:

gm=kn’(W/L)(VGS-Vt)

=0,25x10-3(4,4-1,5)=0,725 mA/V

89

EXEMPLO 4.9

A resistência de saída é dada por:

ro=VA/ID=50/1,06x10-3=47 kΩ

A resistência RG não afeta o ganho de tensão, e

portanto

Av=vo/vi=-gm(RD//ro//RL)=-3,3

A resistência de entrada pode ser determinada a

partir da corrente de entrada:

ii=(vi-vo)/RG=vi(1-Av)/RG

E portanto,

Ri=vi/ii=RG/(1-Av)=2,3 MΩ

90

MODELO T PARA

PEQUENOS SINAIS

91

EFEITO DO CORPO NO MODELO

DE PEQUENOS SINAIS

O corpo age como se fosse uma segunda porta.

Portanto,

gmb=δiD/δvBS

Pode-se mostrar que

gmb=χgm

onde

χ=δVt/δVBS=γ/[2√(2Φf+VSB)]

e χ=0,1 a 0,3.

A próxima figura ilustra o modelo de pequenos

sinais incluindo e efeito do corpo.

92

EFEITO DO CORPO NO MODELO

DE PEQUENOS SINAIS

93

TIPOS DE

AMPLIFICADORES

Existem basicamente 3 tipos de

amplificadores usando transistor MOSFET:

fonte comum.

porta comum.

dreno comum.

Vamos iniciar pelo amplificador fonte

comum, mostrado a seguir.

94

AMPLIFICADOR FONTE

COMUM

95

AMPLIFICADOR FONTE

COMUM

Vamos inicialmente obter o ganho de

tensão. Através do circuito podemos

escrever que:

vgs/vsig=RG/(RG+Rsig)

vo=-gmvgs(RD//ro//RL)

Normalmente podemos escolher RG>>Rsig,

tal que vgs/vsig=1, e portanto:

Av=vo/vsig=-gm(RD//ro//RL)

A resistência de entrada é fácil de ser obtida

é é dada por RG.

96

AMPLIFICADOR FONTE

COMUM

Para obter a resistência de saída, vamos

eliminar a resistência de carga, colocar uma

fonte de tensão na saída e curto-circuitar a

entrada do amplificador. Neste caso, a

resistência de saída é dada por:

Rout=RD//ro

97

AMPLIFICADOR FONTE

COMUM COM RESISTÊNCIA

NA FONTE

98

AMPLIFICADOR FONTE

COMUM COM RESISTÊNCIA

NA FONTE

Vamos desconsiderar inicialmente rO. Para obter o

ganho de tensão, podemos escrever que:

vg=vsig

vs=gmvgsRS

-gmvgs(ro//RL)=vo

Usando nas duas primeiras equações que vgs=vg-vs

temos que:

vgs=vsig(1+gmRS)

Usando a terceira equação temos que:

Av=vo/vsig=-(RD//ro//RL)/(1/gm+RS)

99

AMPLIFICADOR FONTE

COMUM COM RESISTÊNCIA

NA FONTE

Toda resistência colocada na fonte age no

sentido de se reduzir o ganho de tensão.

Este ganho pode ser interpretado como

sendo a resistência vista no pino de dreno

dividida pela resistência vista no pino de

fonte.

A resistência de entrada e a resistência de

saída não se alteram neste caso.

100

AMPLIFICADOR PORTA

COMUM

101

AMPLIFICADOR PORTA

COMUM

Do circuito podemos escrever que:

vsig=-Rsiggmvgs-vgs

vo=-gmvgs(RD//RL)

Portanto, o ganho de tensão é dado por:

Av=vo/vsig=(RD//RL)/(1/gm+Rsig)

A resistência de entrada e de saída podem

ser obtidas por inspeção e são dadas por

1/gm e RD. Observe que esta configuração

possui ganho positivo com baixa resistência

de entrada.

102

AMPLIFICADOR DRENO

COMUM

103

AMPLIFICADOR DRENO

COMUM

Do circuito podemos escrever que:

vg=vsigRG/(RG+Rsig)

vs=vo

gmvgs=vo/Req

onde Req=rO//RL

Portanto, o ganho de tensão é dado por:

Av=vo/vsig=RG/(RG+Rsig)Req/(1/gm+Req)

Como RG>>Rsig e Req>>1/gm, então Av≈1.

104

AMPLIFICADOR DRENO

COMUM

A

resistência de entrada e de saída

podem ser obtidas por inspeção e são

dadas por RG e 1/gm.

Observe que esta configuração possui

pequeno ganho de tensão, grande

resistência de entrada e pequena

resistência de saída. Por isso, recebe o

nome de seguidor de tensão.

105

CAPACITÂNCIAS DE UM

MOSFET

Existem basicamente dois tipos de

capacitâncias em um MOSFET:

Capacitância de porta, formada pelo

eletrodo de porta e pelo canal, tendo a

camada de óxido como dielétrico. A

capacitância por unidade de área é dada por

Cox.

Capacitâncias de depleção fonte-corpo e

dreno-corpo.

106

CAPACITÂNCIAS DE

PORTA DE UM MOSFET

O efeito capacitivo da porta pode ser

modelado por 3 capacitores: Cgs, Cgd, Cgb.

Quando o MOSFET opera na região triodo,

o canal é uniforme, e portanto:

Cgs=Cgd=WLCox/2

Quando o MOSFET opera na saturação, o

canal tem formato triangular, portanto:

Cgs=2WLCox/3

Cgd=0

107

CAPACITÂNCIAS DE

PORTA DE UM MOSFET

Quando o MOSFET opera no corte, o canal

desaparece, portanto:

Cgs=Cgd=0

Cgb=WLCox

108

CAPACITÂNCIAS DE

JUNÇÃO DE UM MOSFET

A capacitância de depleção da junção fontecorpo é dada por:

Csb=Csb0/√(1+VSB/V0)

em que 0,6≤V0≤0,8 V é a tensão interna de

junção.

A capacitância de depleção da junção

dreno-corpo é dada por:

Cdb=Cdb0/√(1+VDB/V0)

109

MODELO PARA ALTAS

FREQUÊNCIAS

110

FREQUÊNCIA fT DE UM

MOSFET

A próxima figura ilustra o modelo de

pequenos sinais de um MOSFET com a

saída em curto.

Podemos escrever que:

Io=gmVgs-j2πfCgdVgs≈gmVgs

Além disso,

Vgs=Ii/[j2πf(Cgs+Cgd)]

Portanto, o ganho de corrente é dado por:

Io/Ii=gm/[j2πf(Cgs+Cgd)]

111

GANHO DE CORRENTE EM

ALTAS FREQUÊNCIAS

112

FREQUÊNCIA fT DE UM

MOSFET

A frequência em que o ganho de corrente é

unitário é dada por:

fT=gm/[2π(Cgs+Cgd)]

Nos dias de hoje é possível fabricar

MOSFETs com fT de alguns GHz.

113

RESPOSTA EM FREQUÊNCIA

DE AMPLIFICADOR FONTE

COMUM

A frequência de corte superior se deve às

capacitâncias parasíticas, enquanto que a

frequência de corte inferior se deve aos

capacitores de acoplamento.

A banda de um amplificador é dada por:

B=fH-fL≈fH

pois fH>>fL

Um bom amplificador é aquele que tem um grande

produto ganho-banda:

GB=AvB

114

RESPOSTA EM FREQUÊNCIA

DE AMPLIFICADOR FONTE

COMUM

115

FREQUÊNCIA DE CORTE

SUPERIOR

Para determinar a frequência de corte

superior temos que a corrente no capacitor

Cgd é dada por:

ICgd=j2πfCgd(vgs-vO)

Vimos anteriormente que vO=-gmRL’vgs,

onde RL’=RD//rO//RL, então

ICgd=j2πfCgd(1+gmRL’)vgs

116

FREQUÊNCIA DE CORTE

SUPERIOR

117

FREQUÊNCIA DE CORTE

SUPERIOR

O quociente entre vgs e a corrente ICgd

fornece a reatância equivalente vista entre

os pontos X e X' devido a Cgd, e é dada por:

vgs/ICgd=1/[j2πfCgd(1+gmRL’)]=1/(j2πfCeq)

ou seja, a capacitância Cgd é refletida para

porta com valor igual a

Ceq=Cgd(1+gmRL’)

Esta transformação é conhecida como efeito

Miller.

118

FREQUÊNCIA DE CORTE

SUPERIOR

Portanto, podemos calcular o ganho através de:

vgs=Z/(Z+Rsig)vsig

vO=-gmvgsRL’

onde

Z=XCt//RG

e

Xct=1/{j2πf[Cgs+Cgd(1+gmRL’)]}

Finalmente, o ganho é dado por:

Av=Av0/(1+j2πf/f0)

onde Av0=-gmRL’RG/(RG+Rsig)≈-gmRL’ e

f0=1/[2π(RG//Rsig)Ct]≈1/(2πRsigCt)

119

EXEMPLO 4.10

Vamos calcular o ganho nas frequências médias e a

frequência de corte superior para um amplificador

com Rsig=100 kΩ, RG=4,7 MΩ, RD=RL=15 kΩ, gm=1

mA/V, rO=150 kΩ, Cgs=1 pF e Cgd=0,4 pF.

A resistência RL’=RD//RL//rO=7,14 kΩ. Como

RG>>Rsig, temos Av0≈-gmRL’=-10-3x7,1x103=-7,1.

A capacitância devido ao efeito Miller é igual a

Ceq=Cgd(1+gmRL’)=0,4x10-12(1+10-3x7,1x103)=3,3 pF,

enquanto que a capacitância total Ct=Cgs+Ceq=4,3 pF.

A frequência de corte é igual a f0≈1/(2πRsigCt)=382

kHz.

120

FREQUÊNCIA DE CORTE

INFERIOR

Para o próximo circuito podemos escrever:

vg=vsigRG/(Rsig+XC1+RG)

vs=gmvgsXCS

iL=gmvgsRD/(RD+XC2+RL)

vO=-RLiL

A partir destas equações podemos obter o

ganho de tensão, dado por:

Av=Av0 (j2πf/fP1)/(j2πf/fP2)/(j2πf/fP3)

/(1+j2πf/fP1)/(1+j2πf/fP2)/(1+j2πf/fP3)

121

FREQUÊNCIA DE CORTE

SUPERIOR

122

FREQUÊNCIA DE CORTE

INFERIOR

onde

Av0=-gm(RL//RD)RG/(RG+Rsig)

fP1=1/[2π(Rsig+RG)C1]

fP2=1/[2π(RD+RL)C2]

fP3=gm/(2πCS)

onde normalmente, a frequência de corte fP3

é bem maior que as outras duas, tal que

fL≈gm/(2πCS).

123

FREQUÊNCIA DE CORTE

SUPERIOR

124

EXEMPLO 4.11

Determine os capacitores de acoplamento

para um amplificador com Rsig=100 kΩ,

RG=4,7 MΩ, RD=RL=15 kΩ, gm=1 mA/V,

rO=150 kΩ, Cgs=1 pF e Cgd=0,4 pF.

Considere que a frequência de corte inferior

é igual a fL=100 Hz.

Para fP3=gm/(2πCS)=100, temos que CS=1,6

μF. Para fP1=fP2=10, temos que C1=3,3 nF e

C2=0,5 μF.

125

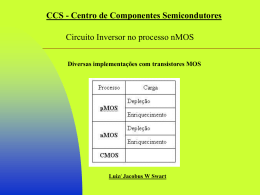

INVERSOR LÓGICO CMOS

Considere o inversor lógico mostrado a seguir.

Colocando na entrada vI=VDD, temos que o

transistor QN irá conduzir, enquanto que QP

ficará cortado, que corresponde ao modelo

circuital mostrado.

De fato, QN irá operar na região triodo com

uma corrente muito pequena, e faz com que

VO=0 V.

A resistência de QN é dada por:

rDSn=1/[kn’(W/L)n(VDD-Vtn)]

126

INVERSOR LÓGICO CMOS

127

INVERSOR LÓGICO CMOS

128

INVERSOR LÓGICO CMOS

Colocando agora na entrada vI=0, temos que

o transistor QP irá conduzir, enquanto que

QN ficará cortado, que corresponde ao

modelo circuital mostrado a seguir.

De fato, QP irá operar na região triodo com

uma corrente muito pequena, e faz com que

VO=VDD V.

A resistência de QP é dada por:

rDSp=1/[kp’(W/L)p(VDD-|Vtp|)]

129

INVERSOR LÓGICO CMOS

130

INVERSOR LÓGICO CMOS

Alguns aspectos do inversor lógico CMOS

merecem se destacados:

–

–

–

Os níveis lógico são iguais às tensões de

alimentação.

Um dos transistores está cortado e o outro

sempre conduz com uma corrente praticamente

nula, o que significa que a dissipação na porta é

praticamente zero.

A resistência de entrada é infinita, e portanto

um grande número de portas lógicas podem ser

conectadas à saída de uma porta.

131

INVERSOR LÓGICO CMOS TRANSFERÊNCIA DE TENSÃO

A característica de transferência de tensão é

mostrada a seguir.

Um inversor CMOS é projetado para ter:

Vtn=|Vtp|

kn’(W/L)n=kp’(W/L)p

No trecho de 0 V até o ponto A, QN está

cortado e QP está na região triodo.

132

INVERSOR LÓGICO CMOS TRANSFERÊNCIA DE TENSÃO

133

INVERSOR LÓGICO CMOS TRANSFERÊNCIA DE TENSÃO

No trecho de 0 até A, QN está cortado.

O trecho AB é obtido quando QN estiver saturado e QP

estiver na região triodo.

O trecho BC é obtido quando QN e QP estiverem

operando na saturação. Assim, para vIB=vIC=VDD/2

vOB=VDD/2+Vt

vOC=VDD/2-Vt

O trecho CD é obtido quando QP estiver saturado e QN

estiver na região triodo.

No trecho de D até VDD, QP está cortado.

134

INVERSOR LÓGICO CMOS ATRASO DE PROPAGAÇÃO

Considere a próxima figura, na qual existe

na saída uma capacitância parasítica C.

Esta capacitância produz um atraso de

propagação não-nulo.

Considerando que a entrada vai de 0 a VDD,

temos que QP corta instantaneamente e o

capacitor será descarregado por QN.

135

INVERSOR LÓGICO CMOS ATRASO DE PROPAGAÇÃO

136

INVERSOR LÓGICO CMOS ATRASO DE PROPAGAÇÃO

Pode-se mostrar que quando a saída vai de alto

para baixo:

tPHL=1,6C/[kn’(W/L)nVDD]

Quando a saída vai de baixo para alto:

tPLH=1,6C/[kp’(W/L)pVDD]

Assim,

tP=(tPHL+tPLH)/2

Para minimizar o atraso de propagação, C

deveria ser minimizado, enquanto que W/L

e/ou VDD maximizados.

137

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

A porta lógica CMOS consome corrente somente

quando QN e QP estiverem conduzindo, ou seja para

Vtn<vI<VDD-|Vtp|, conforme mostra a próxima figura.

A variação de energia no capacitor δEC em um

intervalo infinitesimal δt é igual à potência P vezes o

intervalo de tempo infinitesimal

δEC=Pδt

Como a potência P é igual ao produto da tensão pela

corrente no capacitor, temos que:

δEC=vCiCδt

138

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

139

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

Para um capacitor temos que CδvC=iCδt, e

portanto

δEC=CvCδvC

Quando a saída do inversor variar de vC=VDD a

vC=0, a energia armazenada no capacitor varia de

∫δEC=∫CvCδvC

ou seja:

ΔEC=-CVDD2/2

Assim, toda esta energia é dissipada em QN.

140

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

Por outro lado, quando a saída variar de vC=0 a

VDD, a energia do capacitor varia

ΔEC=CVDD2/2,

Como o capacitor se carrega, toda a energia vem

da fonte de alimentação através de QP.

A energia fornecida pela fonte de alimentação no

período de carga do capacitor é:

δEVDD=VDDiCδt=VDDCδvC

141

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

E portanto, a energia retirada da fonte é

dada por:

ΔEVDD=CVDD2

Como a energia no capacitor no final do

período é de CVDD2/2, portanto CVDD2/2 foi

dissipada em QP.

Portanto a dissipação de energia no ciclo

completo é dada por CVDD2.

142

INVERSOR LÓGICO CMOS DISSIPAÇÃO DE POTÊNCIA

Se o inversor for chaveado f=1/T vezes por

segundo, então a potência dissipada

PD=CVDD2/T=fCVDD2

Uma figura de mérito que mede a qualidade

da tecnologia da fabricação de CIs é dado

pelo produto atraso-potência:

DP=PDtp=1,6fC2VDD/[kp’(W/L)p]

143

CHAVES ANALÓGICAS

Transistores MOSFETs são também

utilizados na fabricação de chaves

controladas por tensão. Estas chaves são

muito empregadas em conversores A/D e

D/A.

Dependendo da tensão de controle, um

MOSFET poderá estar em corte, ou em

condução, quando apresenta uma resistência

dada por:

rDS=1/[kn’(W/L)(VGS-Vt)]

144

CHAVES ANALÓGICAS

145

CHAVES ANALÓGICAS

Considere transistores NMOS e PMOS com

|Vt|=2 V.

A tensão analógica irá variar entre -5vA5

V.

O substrato do NMOS será conectado à

tensão mais negativa do circuito, ou seja -5

V, enquanto que o do PMOS será conectado

ao 5 V.

146

CHAVES ANALÓGICAS

As portas dos transistores são controladas

por dois sinais complementares, que neste

caso podem assumir +5 V e -5 V.

Assim, quando vC=-5 V, tanto o NMOS,

quanto o PMOS estarão cortados, e a chave

aberta.

Quando vC=5 V, o NMOS conduzirá para

-5vA3 V, quanto o PMOS conduzirá para

-3vA5 V.

147

CHAVES ANALÓGICAS

Ou seja, na faixa de -3vA5 V, somente o

PMOS estará conduzindo, já que o mesmo

colocará no seu terminal b, uma tensão que

não permitirá o NMOS conduzir.

Na faixa de -5vA3 V, somente o NMOS

estará conduzindo.

Portanto, na faixa de -5vA5 V, pelo

menos um transistor estará conduzindo.

148

MOSFET TIPO DEPLEÇÃO

149

MOSFET TIPO DEPLEÇÃO

Um transistor MOSFET tipo depleção

possui um canal implantado, o que faz com

que exista corrente de dreno, mesmo para

vGS=0.

150

MOSFET TIPO DEPLEÇÃO

iD x vDS

151

MOSFET TIPO DEPLEÇÃO

iD x vGS

152

DISPOSITIVOS EM ARSENETO

DE GÁLIO - MESFET

Outro material semicondutor tem sido usado

em altas freqüências: o GaAs.

O Gálio tem 3 elétrons, enquanto o Arsênio

tem 5 elétrons na camada de valência.

A maior velocidade de chaveamento deste

material decorre da maior mobilidade dos

elétrons n, que é de 5 a 10 vezes maior que

no silício.

Esta maior mobilidade, implica em maiores

transcondutâncias.

153

Baixar