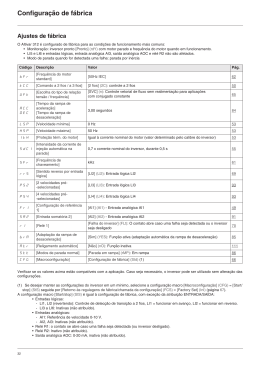

Problema 10.1 Considere um inversor CMOS fabricado num processo de 0,25 m em que Cox=6fF/m, nCox= 115 A/V2, pCox= 30 A/V2, Vtn=-Vtp=0,4V, VDD=2,5V. O W/L de QN é 0,375 m/0,25 m e o de QP vale 1,125 m/0,25 m. Existe uma sobreposição das capacidades GS e GD de 0,3 fF/m de largura da porta. O valor efectivo das capacidades DB são Cdbn=Cdbp=1fF.A capacidade das interligações vale Cw=0,2 fF. Determine tpHL, tpLH e tp. Problema 10.3 Considere um inversor pseudo NMOS fabricado num processo de 0,25 m com os parâmetros do problema 10.1 e com r=9. Determine: a) VOH, VOL, VIL, VIH, VM, NMH e NML. b) (W/L)p c) Isat e PD d) tpHL, tpLH e tp assumindo que a capacidade total na saída do inversor é de 7 fF.

Download

![[Tempo de Propagação] O tempo de propagação de uma porta](http://s1.livrozilla.com/store/data/001673620_1-4c64234c31b80bcb00da8c173228f539-260x520.png)