Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

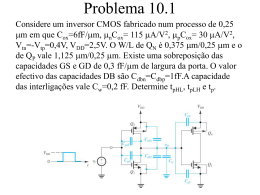

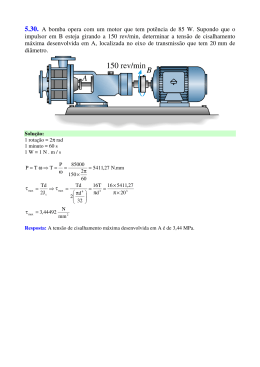

Problema 1. [Tempo de Propagação]

O tempo de propagação de uma porta lógica indica o tempo que uma variação de valor

lógico numa das suas entradas demora a fazer efeito na saída. No caso de um caminho

com várias portas o atraso total é dado pela soma dos atrasos de cada uma das portas.

Os tempos de propagação de uma porta são habitualmente diferentes se a variação na

saída é de 1 para 0, HL, ou de 0 para 1, LH. Por isso e sempre que for viável,

consideram-se as 2 hipóteses possíveis de variação do sinal.

No caso deste circuito existem 4 caminhos possíveis das entradas para a saída, A→Z,

B→Z, C→Z e D→Z. O caminho B→Z é sempre mais rápido que o A→Z porque inclui

um inversor a menos, e o D→Z é igual ao C→Z. Portanto, é apenas necessário analisar

qual dos 2 caminhos A→Z e C→Z tem maior atraso. Vamos analisar separadamente o

caso HL, em que a saída comuta de 1 para 0, e o caso LH, em que a saída comuta de 0

para 1.

tpHL

= max{ tpHL AND + tpHL AND + tpHL NOT , tpHL AND + tpHL OR } =

= max{ 14 + 14 + 10 , 14 + 20}

= max{ 38 , 34} = 38 ns

tpLH

= max{ tpLH AND + tpLH AND + tpLH NOT , tpLH AND + tpLH OR } =

= max{ 14 + 14 + 8 , 14 + 28}

= max{ 36 , 42} = 42 ns

O tempo de atraso máximo do circuito é, portanto, de 42 ns e verifica-se quando a

entrada C varia de 0 para 1 (e D=0, A=0, B=1) e faz variar a saída Z de 0 para 1.

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

Problemas 2 [Tempo de Propagação]

Da entrada A para a saída tem-se:

A 0→1 : tpHL NOT + max{tpSEL LH, tpSEL HL} = 10 + max{29,32} = 10 + 32 = 42 ns

A 1→0 : tpLH NOT + max{tpSEL LH, tpSEL HL} = 8 + max{29,32} = 10 + 32 = 40 ns

Nota: É utilizado o termo max{tpSEL LH, tpSEL HL} e não apenas um dos tpSEL em ambos os

caso porque ao comutar-se a selecção de uma entrada para a outra pode ter-se qualquer

das comutações H→L ou L→H na saída, dependendo dos valores das entradas 0 e 1 do

multiplexer.

Em relação às entradas B, C e D, observando o esquema lógico verifica-se que o tempo

de propagação da entrada B para a saída será sempre maior que o tempo de propagação

de C e D: tem-se o mesmo multiplexer, uma porta OR e uma porta NOT a mais que de

D, e uma porta NOT a mais que de C. Basta portanto calcular os tempos para quando a

entrada B varia.

B 0→1 : tpHL NOT + tpHL OR + tpDados HL = 10 + 20 + 10 = 40 ns

B 1→0 : tpLH NOT + tpLH OR + tpDados LH = 8 + 28 + 20 = 56 ns

O tpMAX do circuito é, portanto, de 56 ns.

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

Problema 3. [Multiplexers/Descodificador]

a) A tabela de verdade da função é:

A B C D F

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

1

1

1

0

0

0

1

1

0

1

0

1

1

1

0

1

1

1

1

1

1

D

0

D

D

0

D

0

1

Utilizando as entradas A, B e C para selecção, obtém-se o seguinte circuito:

Note que a entrada A, de maior peso, está ligada à entrada de selecção de peso 2, B está

ligada à entrada de selecção de peso 1, e C está ligada à entrada de selecção de peso 2

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

b)

Com a função pretendida não é possível eliminar o requisito da porta lógica NOT.

Utilizando como entradas de selecção as variáveis A, B e D, quando (A, B, D) =

(0, 0, 1), dá origem a um termo C . Considerando-se como entradas de selecção as

variáveis A, C e D, quando (A, C, D) = (0, 0, 1), dá origem a um termo B . Finalmente,

com entradas de selecção B, C e D, para (B, C, D) = (0, 0, 1) tem-se um termo A .

c)

Para realizar a função F, as entradas A, B, C e D são utilizadas como entradas do

descodificador. Ao realizar a operação OR entre as saídas do descodificador

correspondentes aos mintermos da função F obtém-se o circuito pretendido.

d)

Divide-se a função F em duas, F1 e F2, correspondentes a A=0 e A=1, respectivamente.

A=0

A=1

B C D F1

B C D F2

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

1

0

0

1

1

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

1

0

0

1

1

0

1

1

1

1

1

1

1

1

1

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

Implementando F1 e F2 com um descodificador 74LS138 e utilizando a entrada A para

seleccionar qual das funções é apresentada à saída obtém-se o seguinte circuito:

Note que a lógica utilizada para seleccionar entre F1 e F2, concretiza um MUX 2→1.

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

Problema 4 [Multiplexers, Descodificadores, Lógica Tri-State]

a)

b) Com multiplexers tri-state é possível ligar todas as saídas dos MUX, eliminando-

se assim a porta lógica OR. Note-se que o descodificador garante que apenas um dos

MUX está activo de cada vez.

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Departamento de Engenharia Electrotécnica e de Computadores

Sistemas Digitais

Instituto Superior Técnico - Universidade Técnica de Lisboa

Problema 5 [Multiplexer]

a)

A tabela de verdade da função e o circuito que a concretiza com um multiplexer são:

S3 S2 S1 A

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

0

S1

S1

1

b)

c)

A implementação com o multiplexer é preferível porque utiliza apenas um circuito

integrado.

Nota: As soluções propostas são indicativas e quaisquer dúvidas, erros ou gralhas devem ser esclarecidos

com os docentes da disciplina nos horários de dúvidas.

Baixar