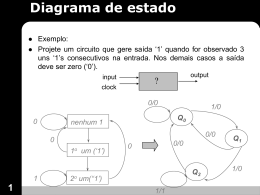

Hardware Description Language Aula 8 –Verilog HDL Prof. Afonso Ferreira Miguel, MSc Estrutura Geral Estrutura Geral Sinais x Operações em Verilog Sinais em Verilog Em Verilog, sinais (nós) podem ser de 3 tipos básicos: • wire ou tri; • wand ou triand; • wor ou trior. Tipos de informações em Verilog Sinais simples (wire) Vetores unidirecionais Vetores bidirecionais Especificação de vetores Definição dos sinais Definição dos sinais Saídas registradas Saídas registradas Primitivas predefinidas Primitivas predefinidas Primitiva Label • Exercício 7 Implementar uma memória ROM com um pino que controle a saída (OE) para TRISTATE. Utilize os mesmos dados armazenados do slide anterior. • Exercício 8 Implementar uma memória RAM com 3 bits de endereço e 4 bits de dados. Esta memória fica sempre habilitada (não tem CE) e escreverá um dado quando wr for para 1. Completar Clique aqui para fazer download do arquivo fonte Paralelismo de processos Processo 1 Processo 2 Processo 3 Processo 4 Processo 5 Arquitetura Paralelismo de processos Alterando A, os processos P1 e P2 são executados em paralelo Paralelismo de processos Alterando B, os processos P1 e P3 são executados em paralelo Paralelismo de processos Alterando C, apenas o processo P2 é executado Comunicação entre processos Processo P1 Processo P2 Processo P3 Comunicação entre processos Processo P1 Processo P2 Processo P3 Comunicação entre processos Evento em A Evento em D Evento em E Comunicação entre processos Comunicação entre processos Evento em D Comunicação entre processos • Exercício 4 Modifique o exercício 4 para que utilize dois processos (proc1 e proc2) para controlar as funções do latch e da saída respectivamente. Utilize um signal (s) para comunicar dados entre os processos. Evitar processos desnecessários Outros atributos array type or objects of the array type Outros atributos Signals attributes Contadores Contador Simples (UP – 3 bits - MOD 8) Tipo inteiro, unsigned ou signed Contadores Contador Simples (UP – 3 bits - MOD 8) O valor contado é incrementado e armazenado em uma variável do processo. Contadores Contador Simples (UP – 3 bits - MOD 8) Neste exemplo, a ação de incremento é sensível a rampa ascendente. Contadores Contador com Reset (UP – 3 bits - MOD 8) A variável de contagem é zerada ao receber um sinal de reset. Contadores Contador com Reset + Load (UP – 3 bits - MOD 8) A entrada é carregada quando load vai para 1. Contadores Contador UP/DOWN – 3 bits - MOD 8 A variável de contagem é incrementada ou decrementada em função da entrada up_down. • Exercício 5 – Implementar em AHDL um contador MOD5 decrescente que realize a contagem (6, 5, 4, 3, 2, 6, 5, ...). VHDL • Máquinas de estado de MOORE Definição dos estados 1 1 e1/1 e0/0 0 0 VHDL • Máquinas de estado de MOORE Definição das transições 1 1 e1/1 e0/0 0 0 VHDL • Máquinas de estado 1 1 e1/1 e0/0 0 0 Definição dos valores de saída • Exercício 6 – Implementar em VHDL uma máquina de estado de MOORE com 4 bits de entrada (+ o clock) e 1 bit de saída. O bit de saída inicialmente deve apresentar o valor ZERO, e deve ir para UM quando receber na entrada o valor 15. Caso ele receba a seqüência 7, 4, 3 a máquina deve voltar ao seu estado inicial ZERO.

Download