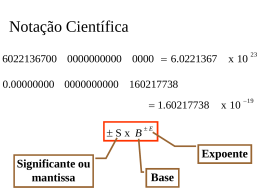

Aula 05: Arquitetura do Conjunto de Instruções ARQUITETURA DE COMPUTADORES DEPT. DE CIÊNCIA DA COMPUTAÇÃO - UFMG Modos de Endereçamento Modo de Endereçamento Exemplo Registrador Imediato Relativo Indexado Absoluto ou Direto Indireto Indireto em memória Autoincremento Autodecremento Escalado ADD R4,R3 ADD R4,#2 ADD R4,100(R1) ADD R4,(R1 + R2) ADD R4,(1001) ADD R4,(R1) ADD R4,@(R1) ADD R4,(R1)+ Significado Regs[R4] += Regs[R3] Regs[R4] += 2 Regs[R4] += Mem[Regs[R1] + 100] Regs[R4] += Mem[Regs[R1] + Regs[R2]] Regs[R4] += Mem[1001] Regs[R4] += Mem[Regs[R1]] Regs[R4] += Mem[Mem[Regs[R1]]] Regs[R4] += Mem[Regs[R1]] Regs[R1] += d ADD R4,-(R1) Regs[R1] -= d Regs[R4] += Mem[Regs[R1]] ADD R4,100(R1)[R2] Regs[R4] += Mem[Regs[R1] + Regs[R2] +100] Utilização Valores em regs Constantes Vars. locais Vetores Dados estáticos Pointers Pointer duplo ou *p Pilha (push) ou array Pilha (pop) ou array Arrays locais Modos de Endereçamento •Somente modos com frequência acima de 1% • Deslocamentos de 8, 16 e 32 bits • Modo registrador não foi considerado (50% dos operandos) Distribuição dos Deslocamentos Distribuição dos Deslocamentos Altamente concentrado em 0 bits 26-27% dos deslocamentos são 0 1% dos valores requerem mais que 16 bits Maioria dos deslocamentos > 14 bits referem-se a números negativos Deslocamentos de 12 bits: 75 % Deslocamentos de 16 bits: 99 % Instruções com Operandos Imediatos Distribuição de Valores para Imediatos Qual deve ser o Tamanho de um Imediato? Ocorrem mais em Loads e operações de ALU Operações em ALU: 1/2 argumento imediato Limites dos valores usados: Maioria são valores positivos 20% eram negativos para CINT2000 30% eram negativos para CFP2000 50% a 70% cabem em 8 bits 75% a 80% cabem em 16 bits Modo de Endereçamento para DSPs DSPs Streams de dados contínuos e infinitos Representados internamente por buffers circulares Modo de endereçamento módulo ou circular Endereçamento para FFT (bn ...b0 )2 (b0 ...bn )2 Frequência dos Modos de Endereçamento do TMS320C54x *ARx-0B *ARx-0% *ARx-0 *ARx-% *ARx*ARx+0B *ARx+0% *ARx+0 *ARx+(num)% *ARx+% *+ARx(num) *ARx+ *+Arx num *ARx ARx(num) #num Frequência 0 10 20 30 40 Distribuição dos Tamanhos dos Acessos de Dados Operações do Conjunto de Instrução Tipos de operação: aritmética e lógica transferência de dados controle sistema FP decimal string gráfica Exemplo do Conjunto de Instruções: 80x86 1 2 3 4 5 6 7 8 9 10 load cond. branch compare store add and sub move r-r call return 22% 20% 16% 12% 8% 6% 5% 4% 1% 1% 96% Velocidade de execução para essas instruções deve ser levado em consideração! Exemplo do Conjunto de Instruções: TMS320C540X 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 store mem16 32.2% load mem16 9.4% mem16 6.8% call 5.0% push mem16 5.0% subtract mem16 4.9% MAC mem16 4.6% move mem-mem16 4.0% change status 3.7% conditional branch 2.6% load mem32 2.5% return 2.5% store mem32 2.0% branch 2.0% repeat 2.0% multiply 1.8% NOP 1.5% add mem32 1.3% subtract mem32 0.9% Controle de Fluxo 4 tipos de instruções de controle de fluxo branch para desvios condicionais jump para desvios incondicionais Chamada e retorno de procedimentos Maneiras de se especificar endereço destino Relativo ao PC Usa menos bits de instrução Independente da carga do código Qualquer modo de endereçamento definido anteriormente Registrador Case, funções virtuais, ponteiros para funções, DLLs Frequência das Instruções de Controle de Fluxo Distância dos Branches em Termos do Número de Instr. Tipos de Condições de Branches Mecanismo para Controle de Salto Condition Code Condition register Compara e salta + setado p/ ALU setada p/ instr testa reg c/ resultado simples parte da instr. de branch 1 instr s/ controle 1 instr a + muito trabalho / instr Condition codes: 80x86, ARM, PPC, SPARC Condition register: Alpha, MIPS Compare and branch: PA-RISC, VAX Codificação de Instruções Um “RISC” Típico Formato de instrução fixo com 32 bits (3 formatos) 32 GPRs de 32 bits (R0 contém zero, par de registradores para DP) Instruções de ALU com 3-operandos, reg-reg Modo de enderaçamento único para load/store: base + deslocamento sem indireção Condições de branch simples Delayed branch veja: SPARC, MIPS, MC88100, AMD29000, i960, i860 PARisc, DEC Alpha, Clipper, CDC 6600, CDC 7600, Cray-1, Cray-2, Cray-3 Exemplo: MIPS Register-Register 31 26 25 Op 21 20 Rs1 16 15 Rs2 11 10 6 5 Rd 0 Opx Register-Immediate 31 26 25 Op 21 20 Rs1 16 15 0 immediate Rd Branch 31 26 25 Op Rs1 21 20 16 15 Rs2/Opx 0 immediate Jump / Call 31 26 25 Op 0 target ISA Mais Popular de Todos os Tempos: O Intel 80x86 1971: Intel inventa o microprocessador 4004/8008, 8080 em 1975 1975: Gordon Moore percebeu mais uma chance de construir novo ISA antes do ISA não se alterar mais por uma década Contratou pessoal de CS em Oregon Não estavam prontos ainda em 1977 (fizeram o 432 em 80) Iniciaram esforço para fazer processador de 16 bits 1978: 8086 com registradores dedicados, espaço de enderaçamento segmentado, 16 bits 8088; versão de barramento de 8 bits do 8086 Presente no núcleo de memória do DCC (DCC2600) ISA Mais Popular de Todos os Tempos: O Intel 80x86 1980: IBM seleciona o 8088 como base para o IBM PC 1980: Coprocessador de ponto flutuante 8087: adiciona 60 instruções usando um híbrido de pilha/registrador 1982: 80286 endereçamento em 24 bits, proteção 1985: 80386 endereçamento em 32 bits, registradores de 32 bits GPR, paginação 1989: 80486 & Pentium em 1992: pipelining e superescalar, mais rápido, FP melhorado Pentium com bug no algoritmo de divisão faz Intel perder um trimestre de lucros trocando chips defeituosos Intel 80x86 - Registradores Inteiros 31 EAX AX AH AL Accumulator EBX BX BH BL Base Addr Reg ECX CX CH CL Count Reg, String, Loop EDX DX DH DL Data Reg, Multiply, Divide ESP SP Stack Ptr. EBP BP Base Ptr (For base or stack seg.) ESI SI Index Reg, String Source Ptr. EDI DI Index Reg, String Dest. Ptr. CS Code Segment SS Stack Segment DS Data Segment ES Extra Segment FS Data Segment GS Data Segment IP Instruction Pointer EIP FLAGS 15 7 0 Condition Codes Intel 80x86 - Registradores de Ponto Flutuante 79 0 FPR0 FPR1 FPR2 FPR3 FPR4 FPR5 FPR6 FPR7 15 Status 0 Top of FP Stack FP Condition Codes Utilização dos Registradores de Ponto Flutuante do 80x86 Pilha (2o. operando ST(1)) Registr. (2o. operando ST(i), i>1) Memória NASA 7 Spice 0.3% 23.3% 76.3% 2.0% 8.3% 89.7% Pilha não é utilizada pelos compiladores para execução mais rápida Formato das Instruções do 80x86 Prefixo Opcode Espec. addr Desloc. Imediato Repeat Lock Seg. Override Addr. Override Size Override Opcode Opcode Ext. mod, reg, r/m sc, index, base Disp 8 Disp 16 Disp 24 Disp 32 Imm 8 Imm 16 Imm 24 Imm 32 (Base reg + 2Scale x Index reg) Codificação das Instruções do 80x86: Campos Mod, Reg, R/M rw=0 w=1 r/m 16b 32b 0 1 2 3 4 5 6 7 AL CL DL BL AH CH DH BH AX CX DX BX SP BP SI DI EAX ECX EDX EBX ESP EBP ESI EDI w do opcode 0 1 2 3 4 5 6 7 mod=0 mod=1 mod=2 mod=3 16b 32b 16b 32b 16b 32b addr=BX+SI addr=BX+DI addr=BP+SI addr=BP+SI addr=SI addr=DI addr=d16 addr=BX =EAX =ECX =EDX =EBX =(sib) =d32 =ESI =EDI same addr mod=0 +d8 SI+d8 DI+d8 BP+d8 BX+d8 same addr mod=0 +d8 (sib)+d8 EBP+d8 ESI+d8 EDI+d8 same addr mod=0 +d16 SI+d8 DI+d16 BP+d16 BX+d16 same same addr as mod=0 reg +d32 field (sib)+d32 “ EBP+d32 “ ESI+d32 “ EDI+d32 “ r/m depende de mod e modo da máquina Tamanho dos campos: Reg=3 bits, R/M=3 bits, Mod=2 bits Codificação das Instruções do 80x86: Campos Sc/Index/Base 0 1 2 3 4 5 Index EAX ECX EDX EBX no index EBP 6 7 ESI EDI Base EAX ECX EDX EBX ESP if mod = 0, d32 if mod != 0, EBP ESI EDI Base + Modo Indexado Escalado Usado quando: mod = 0,1,2 em modo de 32 bits e r/m = 4 2-bit Campo de Escala 3-bit Campo da Índice 3-bit Campo da Base Utilização dos Modos de Endereçamento para 80x86 em Modo de 32 bits Addressing Mode Register indirect Base + 8-bit disp Base + 32-bit disp Indexed Based indexed + 8b disp Based indexed + 32b disp Base + Scaled Indexed Base + Scaled Index + 8b disp Base + Scaled Index + 32b disp 32-bit Direct Gcc Espr. NASA7 Spice Avg. 10% 10% 6% 2% 7% 46% 43% 32% 4% 31% 2% 0% 24% 10% 9% 1% 0% 1% 0% 1% 0% 0% 4% 0% 1% 0% 0% 0% 0% 0% 12% 31% 9% 0% 13% 2% 1% 2% 0% 1% 6% 2% 2% 33% 11% 19% 12% 20% 51% 26% Distribuição do Comprimento das Instruções do 80x86 Instruction Counts: 80x86 v. DLX SPEC pgm x86 DLX DLX÷86 gcc 3,771,327,742 3,892,063,460 1.03 espresso 2,216,423,413 2,801,294,286 1.26 15,257,026,309 16,965,928,788 1.11 spice Conclusões sobre Intel 80x86 Projeto do conjunto de instruções do 8086 Endereçamento: 16 bits vs. 32 bits Proteção: segmentação vs. paginação Armazenamento temporário: acumulador vs. pilha vs. registradores “Algemas” da compatibilidade binária afeta a arquitetura depois de 20 anos Não é muito difícil de fazer mais rápido, como Intel tem mostrado x86 atualmente possui uma microarquitetura RISC Lista de Exercícios 2.1 2.4 2.5 2.6 2.11 2.15 2.19

Download