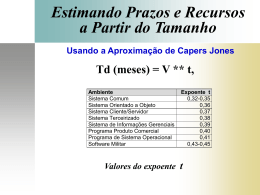

Multithreading e multiprocessamento DAP Spr.‘98 ©UCB 1 Multithreading simultâneo • Thread é um trecho de instruções de um programa • Comparação: – – – – Superescalar sem suporte para multithreading Superescalar com multithreading grosso Superescalar com multithreading fino Superescalar com multithreading simultâneo DAP Spr.‘98 ©UCB 2 Execução de Threads em paralelo Slots de emissão (despacho) tempo Horizontal – capacidade de emissão de instrução a cada ciclo Vertical – sequência de ciclos de clock Caixa branca – slot de emissão não usado naquele ciclo de clock Cores diferentes de branco – threads diferentes DAP Spr.‘98 ©UCB 3 Speedup no Power5 com e sem SMT SPECfp SPECint = 1,23 SPECfp = 1,16 SPECint DAP Spr.‘98 ©UCB 4 perda ganho Características de 4 processadores SMT DAP Spr.‘98 ©UCB 5 Desempenho para SPECint2000 DAP Spr.‘98 ©UCB 6 Desempenho para SPECft2000 DAP Spr.‘98 ©UCB 7 Eficiência em termos de área de silício e potência DAP Spr.‘98 ©UCB 8 Taxonomia das arquiteturas paralelas (Flynn, 1966) • • • • SISD – fluxo de instrução único, fluxo de dados único SIMD – fluxo de instrução único, fluxo de dados múltiplo MISD – fluxo de instrução múltiplo, fluxo de dados único MIMD – fluxo de instrução múltiplo, fluxo de dados múltiplo DAP Spr.‘98 ©UCB 9 MIMDs (Multiprocessadores) • Os MIMDs oferecem flexibilidade. Focaliza alto desempenho, para uma ou várias aplicações, executando muitas tarefas simultaneamente. • Podem se basear nas vantagens de custo-desempenho dos processadores de prateleira – os mesmos processadores usados nas estações de trabalho e servidores. • Os chips multicore aproveitam o investimento de projeto de um núcleo (core) de um processador fazendo a replicação. DAP Spr.‘98 ©UCB 10 Multiprocessador de memória compartilhada centralizada DAP Spr.‘98 ©UCB 11 Multiprocessador de memória distribuída DAP Spr.‘98 ©UCB 12 Desafios do processamento paralelo • Queremos alcançar um ganho de velocidade de 80 com 100 processadores. Que fração da computação original pode ser sequencial? 1 speedup fraçãomelhorada (1- fraçãomelhorada ) razãomelhoria 1 80 fração paralela (1 - fração paralela) 100 80 fraçãoparalela 100 (1- fraçãoparalela) 1 80 - 1 fraçãoparalela 0,9975 79,2 DAP Spr.‘98 ©UCB 13 Latência de acesso remoto à memória • Supor uma aplicação executada em um multiprocessador com 32 processadores, que possui tempo de 200 ns para memória remota. • Considerar que todas as referências, exceto às referentes à comunicação, atingem a memória local. • Os processadores são protelados numa solicitação remota, e a taxa de clock é de 2GHz. • Se o CPI de base (considerando que todas as referências atingem o cache) é 0.5, quanto mais rápido é o multiprocessador se não houver comunicação versus se 0.2% das instruções envolvem uma referência de comunicação remota? Solução: CPI = CPI base + Taxa de solicitação remota x Custo de solicitação remota = 0.5 + 0,2% x Custo de solicitação remota custo de acesso remoto 200ns custo de solicitação remota 400ciclos tempode ciclo 0,5ns Portanto CPI = 0.5 + 0,8 =1.3 e o speedup = 1.3/0.5 = 2.6. DAP Spr.‘98 ©UCB 14 Multiprocessador Simétrico (Symmetric Multiprocessor - SMP) Processor Processor Processor Cache Cache Cache Single bus Todos os processadores são iguais Na falha de um, um outro processador pode substitui-lo Memory I/O Usa sincronismo por memória compartilhada centralizada DAP Spr.‘98 ©UCB 15 CPU de um único thread RAM - quatro programas em execução Front end – busca até 4 instruções paralelas 7 Pipelines, sendo apenas o programa de cor vermelha em execução Nota-se os espaços em branco dos estágios pipeline ociosos DAP Spr.‘98 ©UCB 16 Single Threaded SMP (Symmetric Multiprocessor) Os diferentes programas são executados em CPUs distintos. Programa vermelho numa CPU amarelo em outra DAP Spr.‘98 ©UCB 17 Superthreading ou multithreading • CPU com capacidade para executar mais de um thread simultaneamente, porém, cada estágio do pipeline deve conter instruções de apenas um thread • Não se pode emitir instruções de threads distintos num mesmo instante DAP Spr.‘98 ©UCB 18 Simultaneous multithreading (SMT) ou Hyper-threading (HT) • Não existe restrição de emissão de instruções para threads diferentes em cada ciclo de clock. • Compara-se ao single-threaded SMP DAP Spr.‘98 ©UCB 19 Single-threaded SMP Chips de um único CORE Superescalar SMT DAP Spr.‘98 ©UCB 20 Processadores Multi-Core • Um único chip com múltiplos cores (CPUs), cada um executando threads distintos como em single-threaded SMP • Compatível em softare a uma arquitetura SMT porém tecnologicamente mais interessante, pois pode ser usada uma tecnologia que consome menos energia, e o desempenho aumenta com o número de CORES. DAP Spr.‘98 ©UCB 21

Baixar