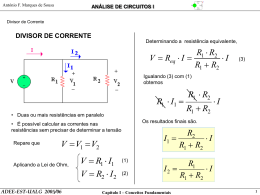

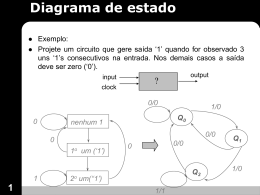

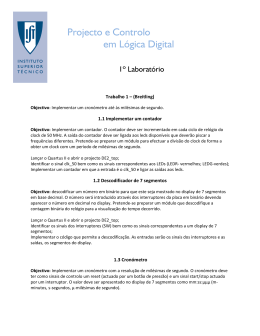

NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br AULA 14 – Aplicação com divisor de freqüência com o CI – 74293. Livro Texto – pág.197 a 200. 1. Contadores Assíncronos comerciais – CI 74293. 1.1 Configuração Interna. 1.2 Bloco contador assincrono ou modulante, tabela da verdade e configuração – CI 74293 R01 1 0 x 0 0 R02 1 x 0 x X CP0 x 1 1 ↓ 1 CP1 x 1 1 1 ↓ Estado Q’s Zera Q’s Mantém Q’s Mantém Q’s Q 0’ Q 1’ 1.3 Resposta em freqüência. Considerando – se o tempo de propagação de um F/F igual a 20ns, sendo o contador de 4 F/Fs então : 1 fMAX = 2. Divisor de freqüência para módulos diferentes de múltiplos de 2n. 2.1 Divisão por 3. a) Representação por diagrama de estados. 0 ↓/0 1 ↓/1 3 ↓/0 2 b) Tabela da verdade do divisor. CLK Q2 Q1 Saída 0 0 0 ↓ 0 1 0 ↓ 1 0 0 ↓ ← Meta Estado 1 1 1 ↓ Pág. 82 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br 3. Formas de Ondas. 3.1 Divisão por 5 Usando a configuração dos 3 F/Fs : a) Entrada por CP1’ e os bits de saída Q1, Q2 e Q3. 1 0 2 b) Tabela da verdade. 3 Q3 0 0 0 0 1 1 4 5 Q2 0 0 1 1 0 0 Q1 0 1 0 1 0 1 Estado 0 1 2 3 4 Meta c) Configuração do Contador 5.3 Divisão por 06 0 1 2 3 4 5 6 Pág. 83 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br a) Configuração do divisor e tabela da verdade Q3 0 0 0 0 1 1 1 Q2 0 0 1 1 0 0 1 Q1 0 1 0 1 0 1 0 Estado 0 1 2 3 4 5 Meta 6. Formas de Ondas. 6.1 Divisão por 10 Usando a configuração dos 4 F/Fs : a) Entrada por CP0’ e os bits de saída Q0, Q1, Q2 e Q3. b) Tabela da verdade. 0 1 2 3 4 9 8 7 6 5 10 Q3 0 0 0 0 0 0 0 0 1 1 1 Q2 0 0 0 0 1 1 1 1 0 0 0 Q1 0 0 1 1 0 0 1 1 0 0 1 Q0 0 1 0 1 0 1 0 1 0 1 0 Estado 0 1 2 3 4 5 6 7 8 9 Meta Pág. 84 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br c) Configuração do Contador 6.2 Formas de Ondas 7. Contadores Integrados – Série 74160 – 163. Binário e Decádicos. CLK ENP ENT CLR LOAD D C B A RCO QD QC QB QA QD QC QB QA CLR’ LOAD’ ENP ENT CLK L X X X X L X X X ↑ H L X X ↑ H H H H H H H L X H X L ↑ X X Função Clear Assíncrono Clear Síncrono Carga Síncrona Crescente n/ altera n/ altera Componente 160/161 162/163 Todos Todos Todos Todos Pág. 85 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br 7.1 Formas de Ondas para análise – Contador binário 74163 Aplicamos algumas condições de entrada para análise da operação do contador. 2. 74160 Pág. 86 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br 8. Outras divisões usando portas auxiliares. 7,11,13,14 e 15. 1. VHDL divisor módulo 5. -- Divisor módulo 5 com contador de 3 bits com Flip-flop JK e -- Realimentação pelas entradas Reset R01 e R02. ENTITY divisor_mod5 IS PORT ( clock :IN BIT; qsaida : BUFFER BIT_VECTOR ( 2 DOWNTO 0)); END divisor_mod5; ARCHITECTURE contador OF divisor_mod5 IS SIGNAL ALTO,m :BIT; COMPONENT neg_jk PORT (clk,j,k,clr :IN BIT; q :OUT BIT); END COMPONENT; BEGIN ALTO <='1'; m <= NOT (qsaida(0) AND qsaida(2) AND NOT qsaida(1)); ff0: neg_jk PORT MAP (j => ALTO, K => ALTO, clk => clock, clr => m, q => qsaida(0)); ff1: neg_jk PORT MAP (j => ALTO, K => ALTO, clk => qsaida(0), clr => m, q => qsaida(1)); ff2: neg_jk PORT MAP (j => ALTO, K => ALTO, clk => qsaida(1), clr => m, q => qsaida(2)); END contador; ENTITY neg_jk IS PORT (clk,j,k,clr q END neg_jk; :IN BIT; :OUT BIT); ARCHITECTURE ff OF neg_jk IS SIGNAL qestado :BIT; BEGIN PROCESS (clk) -- Sinais de entrada BEGIN IF clr = '0' THEN qestado <= '0'; -- Limpa Q ELSIF (clk'EVENT AND clk ='0') THEN -- Na borda de descida do clock IF J ='1' AND K ='1' THEN qestado <= NOT qestado; -- Set Q ELSIF J ='1' AND K ='0' THEN qestado <= '1'; Pág. 87 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina. NOTAS DE AULA NE7720 – SISTEMAS DIGITAIS - II AULA 14 - Prof. Luís Caldas www.luiscaldas.com.br END ELSIF J ='0' AND K ='1' THEN qestado <= '0'; END IF; END IF; END PROCESS; q <= qestado; ff; 2. Formas de Ondas divisor módulo 5. Pág. 88 Obs.: As notas de aulas são recursos para o aluno que assiste às aulas e preenche os espaços desta folha com conteúdo de aula. Estas notas não substituem o livro texto que é a referência da disciplina.

Baixar