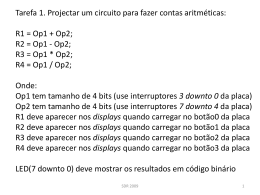

MIPS Monociclo Implementação em VHDL Moraes 03/maio/2011 Incrementada por Calazans em maio/2013 Instruções suportadas • ADDU, SUBU, AND, OR, XOR, NOR – Formato R • ORI, LW, SW – Formato I Hardware Bloco de Controle IR_out control_unit uins MIPS_V0 incpc pc uins.ce uins.rw uins.wreg uins.i • Puramente combinacional – Recebe código objeto da instrução em execução – Decodifica a instrução – Gera a microinstrução, ou seja, o conjunto de microoperações (sinais de controle) para: • • • • Controle dos multiplexadores (uins.i) Controle de escrita no banco de registradores (uins.wreg) Controle de leitura/escrita da/na memória (uins.ce, uins.rw (uins.bw)) Operação na ULA (uins.i) Código VHDL do controle library IEEE; use IEEE.Std_Logic_1164.all; use work.p_MI0.all; entity control_unit is port(ck, rst: in std_logic; -- estes sinais são inúteis nesta versão da -- Unidade de Controle, pois ela é combinacional uins : out microinstruction; ir : in reg32 ); end control_unit; architecture control_unit of control_unit is signal i : inst_type; begin uins.i <= i; i <= ADDU when ir(31 downto SUBU when ir(31 downto AAND when ir(31 downto OOR when ir(31 downto XXOR when ir(31 downto NNOR when ir(31 downto ORI when ir(31 downto LW when ir(31 downto SW when ir(31 downto invalid_instruction ; -- 26)="000000" and ir(10 downto 0)="00000100001" else 26)="000000" and ir(10 downto 0)="00000100011" else 26)="000000" and ir(10 downto 0)="00000100100" else 26)="000000" and ir(10 downto 0)="00000100101" else 26)="000000" and ir(10 downto 0)="00000100110" else 26)="000000" and ir(10 downto 0)="00000100111" else 26)="001101" else 26)="100011" else 26)="101011" else IMPORTANTE: condição "default" é invalid instruction; assert i /= invalid_instruction report "******************* INVALID INSTRUCTION *************" severity error; uins.ce <= '1' when i=SW or i=LW else '0'; uins.rw <= '0' when i=SW else '1'; uins.wreg <= '0' when i=SW else '1'; end control_unit; Esta atribuição corresponde ao processo de decodificação da instrução em si Demais sinais de controle Bloco de dados • Cada código objeto de uma instrução define seus operandos • Instruções tipo R: IR_out control_unit uins MIPS_V0 incpc reg_dest datapath +4 25..21 uins.ce uins.rw uins.wreg uins.i pc 20..16 result RD adRs R1 R1 U L A adRt 15..11 D PC ck rst Q i_address address data Memória de Instruções instruction adRD 20..16 R2 R2 d_address ck rst uins.i wreg uins.wreg uins.i zero uins.i 15..0 data ext32 uins.i Memória de Dados uins.rw uins.ce R2 uins.ce uins.rw ext_sinal ext_0 uins.i • Processo de controle dos multiplexadores: – instR <= '1' when uins.i=ADDU or uins.i=SUBU or uins.i=AAND or uins.i=OOR or uins.i=XXOR or uins.i=NNOR else'0'; -- sinal auxiliar que define quando instruçaõ é tipo R – adD <= instruction(15 downto 11) when instR='1' else instruction(20 downto 16); -- Mux: gera endereço de escrita no banco – op2 <= R2 when instR='1' else ext32; -- Mux: gera entrada inferior da ULA Bloco de dados • Instrução ORI: IR_out control_unit uins MIPS_V0 incpc reg_dest datapath +4 25..21 uins.ce uins.rw uins.wreg uins.i pc 20..16 result RD adRs R1 R1 U L A adRt 15..11 D PC Q i_address ck rst address data Memória de Instruções instruction adRD 20..16 R2 R2 d_address ck rst uins.i wreg uins.wreg uins.i zero Memória de Dados uins.i 15..0 data ext32 uins.i uins.rw uins.ce R2 uins.ce uins.rw ext_sinal ext_0 uins.i • 3 multiplexadores: – adD <= instruction(15 downto 11) when instR='1' instruction(20 downto 16); – op2 <= R2 when instR='1' else ext32; – ext32 <=x"FFFF" & instruction(15 downto 0) when (instruction(15)='1’ and (uins.i=LW or uins.i=SW)) else x"0000" & instruction(15 downto 0); -- extensão de zero! else -- Mux: gera segunda entrada da ULA Bloco de dados • Instruções LW / SW IR_out control_unit uins MIPS_V0 incpc reg_dest datapath +4 25..21 uins.ce uins.rw uins.wreg uins.i pc 20..16 result RD adRs R1 R1 U L A adRt 15..11 D PC Q i_address ck rst address data Memória de Instruções instruction adRD 20..16 R2 R2 ck rst uins.i wreg uins.wreg uins.i zero Memória de Dados uins.i 15..0 data d_address ext32 uins.i uins.rw uins.ce R2 uins.ce uins.rw ext_sinal ext_0 ENDEREÇO É A SOMA DO REG BASE+DESLOCAMENTO uins.i • 3 multiplexadores: – adD <= instruction(15 downto 11) when instR='1' instruction(20 downto 16) ; – op2 <= R2 when instR='1' else ext32; -- Mux: gera segunda entrada da ULA – else ext32 <=x"FFFF" & instruction(15 downto 0) when (instruction(15)='1’ and (uins.i=LW or uins.i=SW)) else x"0000" & instruction(15 downto 0); Código VHDL Código VHDL IR_out uins incpc +4 D PC ck rst uins.ce uins.rw uins.wreg uins.i pc Q i_address address data Memória de Instruções instruction • Memória de instruções é externa ao processador – ver testbench Código VHDL 25..21 uins.i RD adRs 20..16 R1 R1 U L A adRt 15..11 instruction adRD 20..16 R2 R2 uins.i ck 15..0 rst uins.i wreg uins.wreg ext32 ext_sinal ext_0 uins.i uins.i Código VHDL reg_dest result RD adRs R1 R1 U L A adRt adRD ck R2 rst R2 uins.wreg ext32 uins.i data uins.i zero uins.i wreg d_address uins.i uins.ce uins.rw Memória de Dados uins.rw uins.ce R2 ULA BANCO DE REGISTRADORES TOP

Baixar

![Laboratório (Estrutura de Controle [1]).](http://s1.livrozilla.com/store/data/000003987_1-23b321b4612307cfa1117b343103bc77-260x520.png)