Circuitos Integrados Digitais ELT017 Aula 1 INVERSOR LÓGICO DIGITAL CMOS ELT017 - Circuitos Integrados Digitais 2 Inversor Lógico Digital CMOS Elemento básico de qualquer tecnologia de fabricação/projeto de circuitos digitais Operação e características são estendidas/aplicadas no projeto de outras portas lógicas e sistemas mais complexos ELT017 - Circuitos Integrados Digitais 3 Inversor Lógico Digital CMOS Construção Dois transistores MOSFET do tipo enriquecimento casados Qn – canal n Qp – canal p Corpo (substrato) de cada transistor está conectado à sua fonte Elimina o efeito de corpo ELT017 - Circuitos Integrados Digitais 4 Inversor Lógico Digital CMOS Operação Casos extremos de operação vi = nível lógico baixo (≈ 0V) vo = nível lógico alto (≈ VDDV) Qn – canal n Transistor de comando (driver) Qp – canal p Transistor de carga ELT017 - Circuitos Integrados Digitais 5 Caso de Operação vi = VDD ELT017 - Circuitos Integrados Digitais 6 Inversor Lógico Digital CMOS Operação – Caso 1 (1) Caso vi = VDD vGSN = VDD vSGP = 0 vSGP < |Vt| Ponto de operação fica na junção das duas curvas i -v Saída ≈ 0V (10mV) D DS para QN iD-vSD para QP ELT017 - Circuitos Integrados Digitais 7 Inversor Lógico Digital CMOS Operação – Caso 1 (2) Circuito Equivalente Qual a consideração sobre a potencia dissipada em um Inversor Lógico Digital em CMOS? ELT017 - Circuitos Integrados Digitais 8 Inversor Lógico Digital CMOS Operação – Caso 1 (3) Circuito Equivalente Na condição estática Corrente entre o transistores é aproximadamente 0A Dissipação de potencia é tipicamente na casa de micro watts ELT017 - Circuitos Integrados Digitais 9 Inversor Lógico Digital CMOS Operação – Caso 1 (4) Ponto de operação possui grande inclinação Baixa resistência entre a saída e o terra ELT017 - Circuitos Integrados Digitais 10 Caso de Operação vi = 0V ELT017 - Circuitos Integrados Digitais 11 Inversor Lógico Digital CMOS Operação – Caso 2 (1) Caso vi = 0V vGSN = 0 vSGP = VDD vGSN < |Vt| Ponto de operação fica na junção das duas curvas iD-vSD para QP Saída ≈ 5V (5V-10mV) iD-vDS para QN ELT017 - Circuitos Integrados Digitais 12 Inversor Lógico Digital CMOS Operação – Caso 2 (2) Circuito Equivalente Na condição estática Corrente entre o transistores é aproximadamente 0A Dissipação de potencia é tipicamente na casa de micro watts ELT017 - Circuitos Integrados Digitais 13 Inversor Lógico Digital CMOS Operação – Caso 2 (3) Ponto de operação possui grande inclinação Baixa resistência entre a saída e o terra iD-vSD para QP iD-vDS para QN ELT017 - Circuitos Integrados Digitais 14 Operação em rede Pull-Up e Pull-Down ELT017 - Circuitos Integrados Digitais 15 Operação em rede Pull-Up e Pull-Down QN – dispositivo abaixador (pull-down) QN pode drenar uma corrente de carga relativamente alta quando vi em nível alto QP – dispositivo levantador (pull-up) QP pode fornecer uma corrente de carga relativamente alta quando vi em nível baixo ELT017 - Circuitos Integrados Digitais 16 Resistência de Entrada Como IG = 0 a resistência de entrada no inversor é infinita, portanto: Um dado inversor pode ter como carga infinitos outros inversores (ou outras portas lógicas) Porém aumenta-se a capacitância de carga e diminui a velocidade de operação ELT017 - Circuitos Integrados Digitais 17 Característica de transferência de tensão Característica de transferência de tensão do inversor CMOS Projeto considera que: Vtn = |Vtp| = Vt k’n(W/L)n = k’p(W/L)p Como µp é de 0,3 a 0,5 vezes o valor de µn, para que os transistores sejam casados o transistor QP deve ter largura de canal 3 a 4 vezes maior que QN Característica de transferência simétrica e fornecimento de corrente em ambos os lados ELT017 - Circuitos Integrados Digitais 19 Curva de Transferência de Tensão Ponto de Interesse 2 e 3 Margens de ruído do inversor Máximo valor de tensão na saída para nível lógico 0 – VIL Mínimo valor de tensão na saída para nível lógico 1 – VIH ELT017 - Circuitos Integrados Digitais 20 Curva de Transferência de Tensão Ponto de Interesse 2 e 3 Margens de ruído do inversor ELT017 - Circuitos Integrados Digitais 21 Operação dinâmica Atraso de propagação Um parâmetro de caraterização de uma tecnologia é medido pelo atraso de propagação do inversor ELT017 - Circuitos Integrados Digitais 23 Considerações para atraso de propagação Capacitor C representa: Capacitâncias internas de QN e QP Capacitâncias de linhas de interconexão entre o nó de saída do inversor e entrada de outras portas lógicas Capacitâncias de outras portas de carga Chaveamento do inversor ocorre por um pulso ideal Tempo de subida e descida nulos ELT017 - Circuitos Integrados Digitais 24 Operação dinâmica Supondo os transistores casados, o tempo de subida e de descida da forma onda serão iguais ELT017 - Circuitos Integrados Digitais 25 Operação dinâmica Após o chaveamento existe um tempo de descarregamento do capacitor C através de QN O atraso de propagação do nível lógico alto para baixo é tPHL ELT017 - Circuitos Integrados Digitais 26 Corrente e dissipação de potência Corrente no Inversor Digital CMOS Parcela de corrente por chaveamento Quando o inversor CMOS é chaveado, flui corrente entre QP e QN em função de vi Essa corrente dá origem a uma dissipação de potência dinâmica no inversor CMOS Parcela de corrente pela descarga do capacitor Parcela de maior importância A energia no capacitor ½ CVDD² é descarregada por QN e carregada através de QP Dissipação total de CVDD² ELT017 - Circuitos Integrados Digitais 28 Corrente no Inversor Digital CMOS Dissipação total de CVDD² Considerando uma operação dinâmica em uma frequência f, a dissipação de potência será de: PD = fCVDD² Como a frequência está relacionada com tempo de propagação: quanto menor o tempo de propagação, maior a frequência, logo maior dissipação de potência. Figura de mérito da tecnologia: produto atraso-potência (DP – delay-power product) DP = PDtP ELT017 - Circuitos Integrados Digitais 29 PROBLEMAS ELT017 - Circuitos Integrados Digitais 30 Problemas para solução e apresentação em sala 4.57 – Equipe 4.58 – Equipe 4.59 – Equipe 4.60 – Equipe 4.61 – Equipe ELT017 - Circuitos Integrados Digitais 31

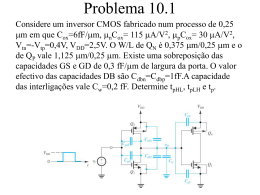

Baixar