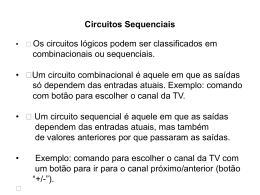

ORGANIZAÇÃO E ARQUITETURA DE COMPUTADORES I Circuitos Sequenciais prof. Dr. César Augusto M. Marcon prof. Dr. Edson Ifarraguirre Moreno 2 / 16 Sistemas Digitais Definição funcional: Aparato dotado de conjuntos finitos de entradas e saídas e capaz de processar informação representada sob forma discreta Representação estrutural: s0 e0 e1 em-1 Sistema Digital Processamento discreto de Informação Subdivisão: • Circuitos combinacionais • Circuitos seqüenciais s1 sn-1 3 / 16 Sistemas Digitais Sequenciais Definição: Circuito, cujo comportamento de cada saída é descrito como função dos valores instantâneos das entradas e de seus valores passados Intuitivamente esta definição leva ao conceito de memória, responsável por armazenar os valores passados Memórias requerem sinais de controle para determinar os instantes de carga e os valores de inicialização Representação: 4 / 16 Sistemas Digitais Sequenciais • • • • Circuito sequencial pode ser representado por um circuito combinacional associado à uma memória A parte combinacional tem como entradas, as entradas externas (entradas atuais) e as entradas internas, provenientes da memória (entradas passadas), que fornecem o estado do circuito A parte combinacional tem como saídas, as saídas externas (saídas do circuito sequencial) e as saídas internas (fornecem o cálculo do próximo estado) para o circuito A memória tem como entradas o valor do próximo estado que será armazenado e sinais de controle – Os principais sinais de controle são o relógio (do inglês, clock) e sinais de inicialização, tais como set, reset, clear, e outros. Estes últimos usados para iniciar a operação do circuito sequencial em um estado conhecido • Circuitos sequenciais são normalmente divididos em síncronos e assíncronos – Síncronos são aqueles cujas transições são dependentes do evento de um sinal único de sincronismo – normalmente chamado de relógio – Assíncronos são aqueles cujas transições não são coordenadas por um único sinal 5 / 16 Relógio • • Relógio é uma onda periódica com frequência, fase e amplitude. O objetivo deste sinal é determinar os instantes de tempo em que o circuito sequencial deve avaliar as suas entradas Exemplo: – Abaixo seguem dois relógios CK1 e CK2 com períodos 20ns e 30ns, respectivamente. Consequentemente com frequências 50MHz e 33,33MHz CK1 CK2 • Exercícios: 1. Desenhar um relógio com as seguintes características: frequência de 1GHz, com 25% do período em 1 e 75% em 0 2. Fazer o VHDL que corresponde ao relógio desenhado 6 / 16 Flip-Flops e Latchs • Flip-flop e latch são circuitos digitais pulsados capaz de servir como uma memória de um bit • São conhecidos como multivibradores biestável, por serem circuitos osciladores com capacidade de assumir dois estados (0 ou 1) • Latch e flip-flop diferem pela lógica de controle de carga da informação o Latch é sensível a um nível do sinal de controle o Flip-flop é sensível a um evento (i.e. uma transição) deste sinal de controle (e.g. relógio) • Nível de um sinal é todo o período de tempo que o sinal se mantem com um valor inalterado, seja este logicamente em 0 ou em 1 o Latchs são sensíveis ao nível 1 ou ao nível 0 • Eventos de relógio são quaisquer variações do sinal de relógio que são reconhecidas pelo flip-flop o FFs são sensíveis a variações de 0 para 1 e de 1 para 0. Ou seja, sensibilidade à borda de subida ou borda de descida 7 / 16 Flip-Flops e Latchs • Para que um flip-flop ou latch consiga armazenar a informação de forma adequada, é necessário que o sinal de entrada esteja estável antes da transição do sinal de controle. Este tempo de estabilização é conhecido como tempo de setup • Existem diversos tipos de flip-flops e latchs. Para a área de Ciência da Computação, o modelo mais elementar é o do tipo D (FFD ou LatchD) • Tanto para latch, quanto para flip-flop, o valor armazenado é amostrado na saída, normalmente chamada de Q, enquanto não ocorrer um novo evento de controle (i.e., nível ou borda) • Além das entradas D e CK (relógio ou clock), latchs e flip-flops têm normalmente as entradas de CE (chip enable) e clear ou preset. CE serve para habilitar o comportamento do biestável, enquanto clear e preset colocam o circuito com os valores 0 e 1 respectivamente 8 / 16 Flip-Flop D (FFD) • Exemplo de FFD, sensível à borda de subida, e apenas com as entradas D e CK Representação • Implementação com portas lógicas NAND PERGUNTA: Como um circuito com apenas portas lógicas consegue armazenar informação? 9 / 16 Equivalência entre Circuitos Combinacionais e Sequenciais • Circuitos combinacionais implementam funcionalidades de maneira espacial – Ou seja, teoricamente, instantaneamente sua funcionalidade pode suas ser obtida • Circuitos sequenciais implementam algoritmos de forma espaço-temporal – Ou seja, sua funcionalidade requer intervalos de tempo • Teoricamente, todo o circuito sequencial pode ser implementado de forma combinacional – O inverso, também é verdadeiro, já que um circuito combinacional é um caso especial de circuito sequencial sem memórias – Todavia, certas funcionalidades são tipicamente implementadas de forma puramente espacial, enquanto outras são implementadas de forma espaço temporal – Os requisitos e restrições de projeto são fatores determinantes para direcionar a implementação 10 / 16 Exercícios de Equivalência entre Circuitos Combinacionais e Sequenciais 1. Faça duas implementações de uma porta E de 4 entradas, utilizando portas lógicas e flip-flops D. Uma de forma combinacional e outra de forma sequencial 2. Faça duas implementações equivalentes de um somador de 4 bits de forma sequencial e de forma combinacional 3. Para ambos os casos acima, avalie vantagens e desvantagens de cada implementação. Principais aspectos a serem abordados: tempo de computação, escalabilidade do sistema, área ocupada, complexidade espaço temporal 11 / 16 Exercícios 4. (POSCOMP 2003 - 21) O contador da figura abaixo é: a. b. c. d. e. Síncrono Assíncrono Isócrono Anisócrono Auto-sincronizado 5. (ENADE 2005 Eng. II - 29) A figura abaixo apresenta um circuito básico para construção de máquinas seqüenciais. Com relação a este circuito, tem-se que: a. b. c. d. e. Se S = 1, então Q = 1 Se R = 1 e S = 1, então Q é indeterminado Na transição de SR = 11 para SR = 10, Q é indeterminado Na transição de SR = 11 para SR = 00, Q é indeterminado Na transição de SR = 00 para SR = 11, Q é indeterminado 12 / 16 Resposta de Exercícios 4. (POSCOMP 2003 - 21) O contador da figura abaixo é: a. b. c. d. e. Síncrono Assíncrono Isócrono Anisócrono Auto sincronizado 5. (ENADE 2005 Eng. II - 29) A figura abaixo apresenta um circuito básico para construção de máquinas sequenciais. Com relação a este circuito, tem-se que: a. b. c. d. e. Se S = 1, então Q = 1 Se R = 1 e S = 1, então Q é indeterminado Na transição de SR = 11 para SR = 10, Q é indeterminado Na transição de SR = 11 para SR = 00, Q é indeterminado Na transição de SR = 00 para SR = 11, Q é indeterminado 13 / 16 Exercícios 6. (ENADE 2005 Eng. II - 19) Os circuitos lógicos podem ser classificados como combinacionais ou sequenciais. Nos circuitos combinacionais, a saída é uma mera combinação lógica dos sinais de entrada. Nos circuitos sequenciais, a sequência dos sinais de entrada influencia a saída. Em outras palavras, os circuitos sequenciais guardam uma memória do passado e os combinacionais, não • Identificando a Lógica Combinacional pela letra C e a Lógica Sequencial pela letra S, as lógicas utilizadas pelos objetos acima representados seriam modeladas, respectivamente, como: 1. 2. 3. 4. 5. C-C-C C-S-S S-C-C S-C-S S-S-S 14 / 16 Resposta do Exercício 6. (ENADE 2005 Eng. II - 19) Os circuitos lógicos podem ser classificados como combinacionais ou sequenciais. Nos circuitos combinacionais, a saída é uma mera combinação lógica dos sinais de entrada. Nos circuitos sequenciais, a sequência dos sinais de entrada influencia a saída. Em outras palavras, os circuitos sequenciais guardam uma memória do passado e os combinacionais, não • Identificando a Lógica Combinacional pela letra C e a Lógica Sequencial pela letra S, as lógicas utilizadas pelos objetos acima representados seriam modeladas, respectivamente, como: 1. 2. 3. 4. 5. C-C-C C-S-S S-C-C S-C-S S-S-S 15 / 16 Exercícios 7. (POSCOMP 2011 - 33) Com base nos conhecimentos sobre projeto de circuitos sequenciais, considere as afirmativas a seguir I. O projeto de circuitos sequenciais usando flip-flops é crítico devido ao problema conhecido como transparência de flip-flops II. Uma vez que um flip-flop é sabidamente sensível a uma das bordas do relógio, o tempo de permanência do relógio em nível alto ou baixo não é mais crítico para o funcionamento do circuito sequencial III. Tempo de setup é o tempo durante o qual a entrada deve ser mantida estável antes da transição ativa do relógio IV. Um flip-flop tipo D pode ser implementado com dois latchs tipo D ou com um latch tipo D e um circuito detector de borda Assinale a alternativa correta a) Somente as afirmativas I e IV são corretas b) Somente as afirmativas II e III são corretas c) Somente as afirmativas III e IV são corretas d) Somente as afirmativas I, II e III são corretas e) Somente as afirmativas I, II e IV são corretas 16 / 16 Resposta de Exercícios 7. (POSCOMP 2011 - 33) Com base nos conhecimentos sobre projeto de circuitos sequenciais, considere as afirmativas a seguir I. O projeto de circuitos sequenciais usando flip-flops é crítico devido ao problema conhecido como transparência de flip-flops II. Uma vez que um flip-flop é sabidamente sensível a uma das bordas do relógio, o tempo de permanência do relógio em nível alto ou baixo não é mais crítico para o funcionamento do circuito sequencial III. Tempo de setup é o tempo durante o qual a entrada deve ser mantida estável antes da transição ativa do relógio IV. Um flip-flop tipo D pode ser implementado com dois latchs tipo D ou com um latch tipo D e um circuito detector de borda Assinale a alternativa correta a) Somente as afirmativas I e IV são corretas b) Somente as afirmativas II e III são corretas c) Somente as afirmativas III e IV são corretas d) Somente as afirmativas I, II e III são corretas e) Somente as afirmativas I, II e IV são corretas 17 / 16 Exercícios (POSCOMP 2014, Questão 43) Analise o diagrama abaixo e considere as afirmativas a seguir I. O contador realiza uma contagem sequencial e crescente. II. O módulo desse contador é 20. III. O contador é do tipo assíncrono (ripple counter). IV. A substituição dos flip-flops JK por flip-flops do tipo SR (Set-Reset) não altera sua operação como contador binário Assinale a alternativa correta. a) Somente as afirmativas I e II são corretas. b) Somente as afirmativas I e IV são corretas. c) Somente as afirmativas III e IV são corretas. d) Somente as afirmativas I, II e III são corretas. e) Somente as afirmativas II, III e IV são corretas. 18 / 16 Resposta de Exercícios (POSCOMP 2014, Questão 43) Analise o diagrama abaixo e considere as afirmativas a seguir I. O contador realiza uma contagem sequencial e crescente. II. O módulo desse contador é 20. III. O contador é do tipo assíncrono (ripple counter). IV. A substituição dos flip-flops JK por flip-flops do tipo SR (Set-Reset) não altera sua operação como contador binário Assinale a alternativa correta. a) Somente as afirmativas I e II são corretas. b) Somente as afirmativas I e IV são corretas. c) Somente as afirmativas III e IV são corretas. d) Somente as afirmativas I, II e III são corretas. e) Somente as afirmativas II, III e IV são corretas.

Baixar