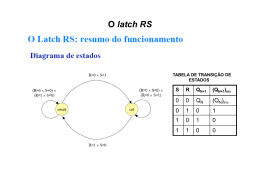

Eletrônica Digital prof. Victory Fernandes [email protected] www.tkssoftware.com/victory Circuitos combinacionais Em qualquer instante de tempo, níveis lógicos das saídas depende apenas dos níveis lógicos das entradas Condições de entrada anteriores não tem efeito sobre as saídas atuais Circuitos não tem memória Flip-Flops Elemento de memória Implementado a partir de portas lógicas Também conhecidos como FFs, latch e multivibrador biestável Flip-Flops Entradas de controle Nome depende do tipo de flip-flop em questão Saídas Q e Q’ Q é a saída normal do FF e Q’ a saída invertida Q representa o estado do FF Tipo SR Tipo JK Tipo D Flip-Flop SR SET/RESET(CLEAR) Q = 1 “setar” o flip-flop Q = 0 “resetar” o flip-flop Flip-Flop SR Latch com NAND Latch com NOR Entradas em repouso, então uma delas é pulsada sempre que se deseja alterar as saídas NAND Latch com NAND Latch com NAND Entradas em repouso (nível ALTO), então uma delas é pulsada (nível BAIXO) sempre que se deseja alterar as saídas Existem dois estados de saída igualmente prováveis quando SET=RESET=1 Latch com NAND Quando energizado não é possível prever o estado inicial da saída do FF se as entradas SET=RESET=1 Existem chances iguais de o estado inicial da saída ser Q=0 ou Q=1 Dependência de fatores como atrasos internos de propagação, capacitâncias parasitas e carga externa Latch com NAND Se Q=0 então NAND2 dá saída Q’=1 e consequentemente NAND1 dá saída Q=0 Latch com NAND Se Q=1 então NAND2 dá saída Q’=0 e consequentemente NAND1 dá saída Q=1 Latch com NAND Se um latch tiver de iniciar em um estado particular para garantir a operação adequada de um circuito, ele não deve ser iniciado com SET=RESET=1, ou seja, terá de ser colocado no estado desejado Aplicar pulso apropriado na entrada SET ou RESET no início da operação do circuito Setando o Latch Análise quando Q=0 ao energizar Quando SET=0 no instante t0, saída altera para Q=1 Quando retornamos SET=1 no instante t1, valor da saída permace Q=1 Setando o Latch Análise quando Q=1 ao energizar Quando SET=0 no instante t0 saída permanece Q=1 Quando retornamos SET=1 no instante t1, valor da saída permace Q=1 Setando o Latch Nos dois casos anteriores a saída assume valor Q=1 quando entrada SET é pulsada Resetando Latch Análise quando Q=0 ao energizar Quando RESET=0 no instante t0, valor da saída permanece Q=0 Quando retornamos RESET=1 no instante t1, valor da saída permace Q=0 Resetando Latch Análise quando Q=1 ao energizar Quando RESET=0 no instante t0, valor da saída altera para Q=0 Quando retornamos RESET=1 no instante t1, valor da saída permace Q=0 Resetando o Latch Nos dois casos anteriores a saída assume valor Q=0 quando entrada RESET é pulsada Latch com NAND Resumo SET=RESET=1 Estado normal de repouso Não tem nenhum efeito na saída Saída Q permace a mesma da condição anterior SET=0; RESET=1 (Setar o latch) Saída Q=1 Saída permance Q=1 mesmo se SET=1 SET=1; RESET=0 Saída Q=0 Saída permance Q=0 mesmo se RESET=1 Latch com NAND Resumo SET=RESET=0 Tenta a mesmo tempo setar e resetar o latch Produz Q=Q’=1 Se as entradas retornarem ao 1 simultaneamente o resultado é imprevisível Condição inválida Latch com NAND Resumo SET 0 0 1 1 RESET 0 1 0 1 Saída Inválida* Q=1 Q=0 Não muda * Produz Q=Q’=1 Representação Alternativas NOR Latch com NOR Latch com NOR Resumo SET 0 0 1 1 RESET 0 1 0 1 Saída Não muda Q=0 Q=1 Inválida* * Produz Q=Q’=0 Latch com NOR Entradas em repouso (nível BAIXO), então uma delas é pulsada (nível ALTO) sempre que se deseja alterar as saídas Existem dois estados de saída igualmente prováveis quando SET=RESET=0 Latch com NOR Quando energizado não é possível prever o estado inicial da saída do FF se as entradas SET=RESET=0 Existem chances iguais de o estado inicial da saída ser Q=0 ou Q=1 Dependência de fatores como atrasos internos de propagação, capacitâncias parasitas e carga externa Latch com NOR Se Q=0 então NOR2 dá saída Q’=1 e consequentemente NOR1 dá saída Q=0 Se Q=1 então NOR2 dá saída Q’=0 e consequentemente NOR1 dá saída Q=1 Latch com NOR Se um latch tiver de iniciar em um estado particular para garantir a operação adequada de um circuito, ele não deve ser iniciado com SET=RESET=0, ou seja, terá de ser colocado no estado desejado Aplicar pulso apropriado na entrada SET ou RESET no início da operação do circuito Latch com NOR Resumo SET=RESET=0 Estado normal de repouso Não tem nenhum efeito na saída Saída Q permace a mesma da condição anterior SET=1; RESET=0 (Setar o latch) Saída Q=1 Saída permance Q=1 mesmo se SET=0 SET=0; RESET=1 Saída Q=0 Saída permance Q=0 mesmo se RESET=1 Latch com NOR Resumo SET=RESET=1 Tenta a mesmo tempo setar e resetar o latch Produz Q=Q’=0 Se as entradas retornarem ao 0 simultaneamente o resultado é imprevisível Condição inválida Exemplo de aplicação Exemplo de aplicação Exemplo de aplicação Exemplo de aplicação Pulsos Digitais Borda de subida tr – Rise Time Borda de descida tf – Fall Time Tempo que a tensão leva para variar entre 10% e 90% do nível ALTO Duração, Largura do pulso tw – Width Time Tempo entre os pontos em que as bordas estão a 50% do nível alto Pulsos Digitais Sinal de Clock Sistemas assíncronos Sistemas síncronos Sinal de Clock Sistemas assíncronos Saída pode mudar de estado a qualquer momento em que uma ou mais entradas mudarem de estado Projeto e análise de defeitos são mais complicados Sinal de Clock Sistemas síncronos O momento exato em que uma saída qualquer muda de estado é determinado pelo sinal de clock Sinal de clock é um trem de pulsos retangulares (onda quadrada) Sinal de clock é distribuido para todo o sistema (sistema trabalha de forma sincronizada) Sistemas síncronos Velocidade da operação depende da frequência do clock (1Hz=1ciclo/segundo) É possível sincronizar eventos usando flipflops com clock Projetados para só mudar de estado em uma das transições o sinal de clock Flip-flop com Clock Entradas de controle síncronas Determina O QUE acontece com as saídas Entrada de clock é denominada CLK, CK ou CP Determina QUANDO as saídas serão alteradas Flip-flop com Clock Entrada de clock é disparada por borda de subida ou descida Flip-flop SR com Clock Resumo * Produz Q=Q’=0 Flip-flop SR com Clock Resumo Flip-flop SR com Clock Resumo * Produz Q=Q’=1 Flip-flop disparado por borda Circuito Interno Circuito interno dividido em 3 partes Latch NAND ou NOR Circuito direcionador de pulsos Circuito detector de borda Flip-flop disparado por borda Detector de borda Leva em consideração atraso de resposta das portas lógicas (nanosegundos) de forma a produzir um pulso estreito (spike) durante as bordas As saída Q é afetada por um curto período de tempo após a ocorrência da borda ativa Detector de borda Parâmetros de Temporização Devem ser observados para que o FF com clock responda forma confiável às entradas de controle quando ocorrer uma transição ativa da entrada CLK Tempo de Setup (ts) (preparação) Tempo de Hold (th) (manutenção) Parâmetros de Temporização Parâmetros de Temporização Tempo de Setup (ts) (preparação) Intervalo de tempo que precede imediatamente a transição ativa do sinal de clock durante o qual a entrada de controle deve ser mantida Tempo de Hold (th) (manutenção) Intervalo de tempo que segue imediatamente após a transição ativa do sinal de clock durante o qual a entrada de controle deve ser mantida Fabricantes determinam este valor e se não respeitado o FF pode responder de forma não confiável Parâmetros de Temporização Para garantir que o FF funcione corretamente quando ocorrer uma transição ativa do clock Entradas de controle não devem mudar de estado por pelo menos 1 intervalo de tempo ts(min) antes da transição de clock Entradas de controle não devem mudar de estado por pelo menos 1 intervalo de tempo th(min) após a transição de clock Parâmetros de Temporização Tempo de Setup (ts) (preparação) Valores mínimos na ordem de 5 a 50ns Tempo de Hold (th) (manutenção) • Valores mínimos na ordem de 0 a 10ns Tempos medidos entres os instantes em que as transições estão em 50% SN54279 QUADRUPLE S-R LATCHES SN54279 QUADRUPLE S-R LATCHES Sumô básico Sumô completo Dúvidas? Victory Fernandes E-mail: [email protected] Site: www.tkssoftware.com/victory Referências Básicas Sistemas digitais: fundamentos e aplicações - 9. ed. / 2007 - Livros FLOYD, Thomas L. Porto Alegre: Bookman, 2007. 888 p. ISBN 9788560031931 (enc.) Sistemas digitais : princípios e aplicações - 10 ed. / 2007 - Livros - TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. São Paulo: Pearson Prentice Hall, 2007. 804 p. ISBN 978-85-7605-095-7 (broch.) Elementos de eletrônica digital - 40. ed / 2008 - Livros - CAPUANO, Francisco Gabriel; IDOETA, Ivan V. (Ivan Valeije). São Paulo: Érica, 2008. 524 p. ISBN 9788571940192 (broch.) REFERÊNCIAS COMPLEMENTARES: Eletronica digital: curso prático e exercícios / 2004 - Livros - MENDONÇA, Alexandre; ZELENOVSKY, Ricardo. Rio de Janeiro: MZ, c2004. (569 p.) Introdução aos sistemas digitais / 2000 - Livros - ERCEGOVAC, Milos D.; LANG, Tomas; MORENO, Jaime H. Porto Alegre, RS: Bookman, 2000. 453 p. ISBN 85-7307-698-4 Verilog HDL: Digital design and modeling / 2007 - Livros - CAVANAGH, Joseph. Flórida: CRC Press, 2007. 900 p. ISBN 9781420051544 (enc.) Advanced digital design with the verlog HDL / 2002 - Livros - CILETTI, Michael D. New Jersey: Prentice - Hall, 2002. 982 p. ISBN 0130891614 (enc.) Eletronica digital / 1988 - Livros - Acervo 16196 SZAJNBERG, Mordka. Rio de Janeiro: Livros Técnicos e Científicos, 1988. 397p. Eletronica digital : principios e aplicações / 1988 - Livros - MALVINO, Albert Paul. São Paulo: McGraw-Hill, c1988. v.1 (355 p.) Eletrônica digital / 1982 - Livros - Acervo 53607 TAUB, Herbert; SCHILLING, Donald. São Paulo: McGraw-Hill, 1982. 582 p.

Baixar