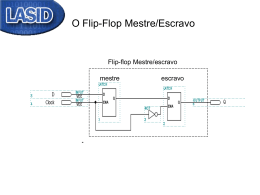

Eletrônica Digital Flip-Flops e Registradores de Deslocamento Prof. Wanderley Introdução Eletrônica Digital divide-se em lógica combinacional e lógica sequencial Circuitos combinacionais apresentam saídas dependentes das variáveis de entrada Circuitos sequenciais apresentam saídas dependentes das variáveis de entrada e de estados anteriores Os estados anteriores devem ser armazenados em algum local para uso posterior Os elementos de armazenamento são os chamados FLIPFLOPs FLIP-FLOPs Q (Saída principal) Entrada 1 Clock Entrada 2 Flip-Flop Q Q 0 Q 1 Q 1 Q 0 Clock 0 1 0 1 0 1 0 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 0 0 0 1 S R Qa Qf 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 0 0 1 0 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 0 1 0 1 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 0 1 1->0 0->1 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 0 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 1 0 0->1 1->0 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 1 0 1 0 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 1 1 0->1 1 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 inválido 1 1 1 Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Tabela Verdade Latch RS 1 1 1 0->1 S R Qa Qf 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 inválido 1 1 1 inválido Flip-Flop RS Básico Tabela Verdade S R Qa Qf 0 0 0 0 S R Saída 0 0 1 1 0 0 Não muda 0 1 0 0 0 1 Q=0 0 1 1 0 1 0 Q=1 1 0 0 1 1 1 inválido 1 0 1 1 1 1 0 inválido 1 1 1 inválido Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND Latch RS Q SET Latch RS RESET Q Flip-Flop RS Básico Construindo o flip-flop RS a partir de portas NAND FLIP-FLOP RS CLOCK Qf 0 Qa 1 Set CLOCK Reset ´FF RS Q Flip-Flop RS Q Flip-Flop RS Básico PROBLEMA: O FF RS NÃO ACEITA TODAS AS COMBINAÇÕES DE ENTRADA POSSÍVEIS! S R Saída 0 0 Não muda 0 1 Q=0 1 0 Q=1 1 1 inválido Flip-Flop JK TABELA VERDADE J CLOCK K Q Flip-Flop JK Q J K Qa S R Qf 0 0 0 0 0 Qa 0 0 1 0 0 Qa 0 1 0 0 0 Qa=0 0 1 1 0 1 0 1 0 0 1 0 1 1 0 1 0 0 Qa=1 1 1 0 1 0 1 1 1 1 0 1 0 Qa 0 1 Qa Flip-Flop JK TABELA VERDADE J K Qa S R Qf 0 0 0 0 0 Qa 0 0 1 0 0 Qa 0 1 0 0 0 Qa=0 0 1 1 0 1 0 1 0 0 1 0 1 1 0 1 0 0 Qa=1 1 1 0 1 0 1 1 1 1 0 1 0 Qa 0 1 J K Qf 0 0 Qa 0 1 0 1 0 1 1 1 Qa Qa TODAS AS ENTRADAS SÃO VÁLIDAS! Flip-Flop JK com PRESET e CLEAR CLEAR PRESET Qf 0 0 Não permitido 0 1 0 1 0 1 1 1 FF JK Flip-Flop JK Mestre-Escravo O FF JK apresenta uma característica indesejável. Quando o clock for 1, o circuito funciona como um circuito combinacional, de modo que qualquer mudança em J e/ou K fará com que a saída se altere. MESTRE ESCRAVO Flip-Flop JK Mestre-Escravo com Entradas Preset e Clear MESTRE ESCRAVO Flip-Flop T Pode ser obtido a partir de um FF JK Mestre-Escravo, com as entradas JK curto-circuitadas. J K T Qf 0 0 0 Qa 0 1 X X 1 0 X 1 1 1 X Qa T Qf 0 Qa 1 Qa T de Toggle (Comutado) Flip-Flop D Pode ser obtido a partir de um FF JK Mestre-Escravo, com a entrada K invertida em relação a J. J K D Qf 0 0 X X D Qf 0 1 0 0 0 0 1 0 1 1 1 1 1 1 X X O Registrador de Deslocamento Um flip-flop é capaz de armazenar um único bit. Se necessitamos armazenar uma informação contendo mais de um bit, o flip-flop será insuficiente. Para resolver esse problema, utilizamos o chamado Registrador de Deslocamento (Shift Register). O Registrador de Deslocamento Observe que a natureza das conexões entre registradores faz com que os JK funcionem como D. O Registrador de Deslocamento: Transferência Paralela de Dados Todos os bits são simultaneamente transferidos O Registrador de Deslocamento: Transferência Serial de Dados Os bits são sequencialmente transferidos O Registrador de Deslocamento: Conversor Série-Paralelo I=1010 O Registrador de Deslocamento: Conversor Paralelo-Série Enable=0 =>Funcionamento normal do registrador Enable=1=>Carregar entradas PRs nos flip-flops

Baixar