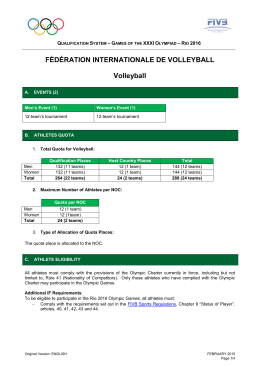

Power-Aware and BIST-Aware NoC Reuse on the Testing of Core-based Systems Érika Cota Flávio Wagner Luigi Carro Marcelo Lubaszewski UFRGS Porto Alegre, Brazil Context SoC core core core core core core back next home Reuse Model tester SoC core core core core core core back next home Reuse Model tester SoC core core core core core core back next home Reuse Model tester SoC core core core core core core back next home Goal Revisão dos principais Improve the reuse the on-chip network as objetivostest access mechanism e fatores de sucesso minimal area overhead zero pin overhead feasible test time Power consumption is an issue? Optimal set of BISTed cores? back next home Outline Revisão dos principais NoC-based Test objetivos Power consumption calculation e fatores de sucesso Modified scheduling Considering BISTed cores Experimental Results Final Remarks back next home Access Paths Within the NoC input CUT 1 input CUT 2 output output back next home Access Paths Within the NoC input CUT CUT1 CUT CUT2 back next home Access Paths Within the NoC CUT CUT1 input CUT CUT2 back next home Access Paths Within the NoC CUT CUT1 CUT CUT2 output back next home Access Paths Within the NoC CUT CUT1 CUT CUT2 output back next home Access Paths Within the NoC input CUT CUT1 CUT CUT2 back next home Access Paths Within the NoC input CUT CUT1 CUT CUT2 back next home Access Paths Within the NoC CUT CUT1 CUT CUT2 output back next home Access Paths Within the NoC CUT CUT1 CUT CUT2 output back next home Parallelism Within the NoC input input CUT 1 CUT 2 output output back next home Pipeline Within the NoC input input CUT 1 CUT 2 output CUT 3 output back next home Pipeline Within the NoC input input CUT 1 CUT 2 output CUT 3 output back next home Pipeline Within the NoC input input CUT 1 CUT 2 output CUT 3 output back next home Pipeline Within the NoC BOTTLENECKS! input CUT 1 CUT 2 CUT 3 output back next home Packets Scheduling input CUT 1 CUT 2 output CUT 3 back next home Packets Scheduling input CUT 1 CUT 2 output CUT 3 back next home Packets Scheduling input CUT 1 CUT 2 output CUT 3 back next home Packets Scheduling input CUT 1 CUT 2 output CUT 3 back next home Packets Scheduling input CUT 1 CUT 2 output CUT 3 back next home Reuse Algorithm Define test packets Define access paths for each core Select a packet Find available access path Schedule packet back next home Power Consumption Calculation Core 1 Core 2 Router Core 4 Core 3 Router Core 5 Router Router Core 6 Router Router back next home Power Consumption Calculation Core 1 Core 2 Router Core 4 Core 3 Router Core 5 Router Router Core 6 Router Router back next home Power Consumption Calculation • F(#ffs, #gates, switching rate) • per frequency) Core 2 cycle (any Core 3 • per packet Core 1 Router Core 4 Router Core 5 Router Router Core 6 Router Router back next home Power Consumption Calculation • F(length,width,switching rate) Core 1 (any frequency) Core 2 Core 3 • per cycle Router Core 4 Router Core 5 Router Router Core 6 Router Router back next home Power Consumption Calculation • F(#ffs, #gates, switching rate) • per cycle (any frequency) Core 2 Core 3 • per pattern Core 1 Router Core 4 Router Core 5 Router Router Core 6 Router Router back next home Power Consumption of One Packet input CUT CUT1 CUT 4*PW(router) + 3*PW(channel) + PW(CUT+wrapper) back next home Power-Aware Scheduling back next home Power-Aware Scheduling back next home Power-Aware Scheduling back next home Experimental Setup SOCIN Network – – – – under development at UFRGS Grid topology 32-bit channels deterministic routing (XY) ITC’02 SoC Test Benchmarks – d695, g1023 – Placement for synthetic applications back next home Experimental Results - d695 Cores consumption >> wrapper consumption 50000 Test time 40000 1 in / 1out 2 in / 2 out 3 in / 3 out 4 in / 4 out 30000 20000 10000 0 no 50% 40% 30% 20% 10% limit Power Limit back next home Experimental Results - g1023 Cores consumption >> wrapper consumption Inputs/ No power Outputs Limit 50% 30% 20% 10% 1/1 52145 52145 52296 51853 33521 (0%) (0.29%) 2/2 31898 31547 33032 41016 67962 (-1.1%) (3.56%) 3/3 22648 24869 25873 37757 64557 (9.8%) (14.2%) 4/4 18851 19776 (4.9%) 31488 (67%) 37871 66088 back next home Experimental Results - d695 Test time Cores consumption wrapper consumption 80000 70000 60000 50000 40000 30000 20000 10000 0 1 in / 1out 2 in / 2 out 3 in / 3 out 4 in / 4 out no 50% 40% 30% 20% 10% limit Power Limit back next home Experimental Results - g1023 Cores consumption wrapper consumption Inputs/ No power Outputs Limit 50% 30% 20% 10% 1/1 52145 835 - - - 2/2 31898 34355 61 61 - 3/3 22648 38598 102 61 - 4/4 18851 38633 158 61 - back next home BIST-Aware Scheduling Each core has a BISTed version – 30% more area – 50% more power consumption – 2x the number of test vectors All cores BISTed – system test time = largest test time among cores – power consumption may be na issue back next home BIST-Aware Scheduling 1) All cores BISTed – maximum parallelization – minimum test time? 2) Define test scheduling considering power constraints 3) Replace the core with largest test time by its external tested version 4) Repeat 2 and 3 until test time increases back next home Experimental Results - p22810 No power constraints BISTed Cores back next home Experimental Results - p22810 No power constraints BISTed Cores back next home Experimental Results - p22810 No power constraints BISTed Cores back next home Experimental Results - p22810 Multiple BIST model BISTed Cores back next home Final Remarks Alternative TAM for NoC-based SoCs good trade-off test time x area X pin overhead even under power constraints (ETW’03) Selection of the optimal set of BISTed cores for test time minimization (TRP’03) Further selection of the best BIST method for the cores in the system back next home

Baixar