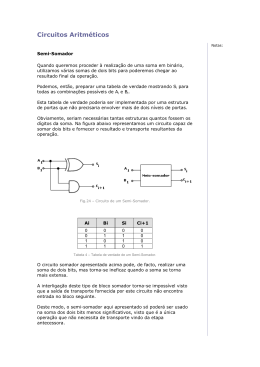

Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 1 (Trabalho sem Relatório) Semana 20 de Setembro a 24 de Setembro Objectivos: Verificação de equivalência de representações através de expressões booleanas, tabelas de verdade e esquemáticos. Contacto com tecnologias de implementação: famílias lógicas TTL/HC/HCT Exercício 1: De tabelas de verdade para expressões booleanas Considerando a seguinte tabela de verdade, encontre a expressão para a saída C: a) Considerando a 1ª forma canónica; b) Considerando a 2ª forma canónica. A B C 0 0 1 1 0 1 0 1 0 1 1 0 Exercício 2: De expressões booleanas para tabelas de verdade Para cada uma das funções abaixo representadas, apresente as tabelas de verdade associadas. a) f1(x,y) = x. y (NAND de 2 entradas) b) f2(x,y) = x. y + x. y Exercício 3: Do esquemático para expressões booleanas Identifique as expressões associadas as várias funções presentes no seguinte esquemático: Exercício 4: De esquemático para tabelas de verdade Apresente a tabela de verdade associada às várias funções encontradas no esquemático do Exercício 3. Exercício 5: De expressões booleanas para esquemáticos Considerando as expressões obtidas no exercício 1, apresente os esquemáticos associados. Exercício 6: Simplificação algébrica de expressões booleanas Simplifique as expressões booleanas abaixo, por aplicação de teoremas da álgebra de Boole: a) (a + b.c).(b + c.d ) b) (a + b.c).(d + b.e) Exercício 7: Implementação de funções booleanas elementares Realize a montagem do esquemático do Exercício 3, utilizando as bases de experimentação disponíveis no laboratório. Compare os resultados obtidos com a tabela de verdade obtida no Exercício 4. Para a detecção de eventuais falhas na montagem utilize as pontas de prova disponíveis no laboratório. DEE-FCT-UNL Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 2 (Trabalho com Relatório) Semana 27 de Setembro a 1 de Outubro Objectivos: Transformação de funções booleanas permitindo a utilização exclusiva de NANDs ou NORs. Simplificação de funções booleanas através de mapas de Karnaugh. Simplificação de funções booleanas incompletamente especificadas através de mapas de Karnaugh. Exercício 8: Suficiência do NOR e do NAND Para cada uma das funções abaixo representadas: a) Apresente expressões equivalentes que recorram apenas a portas NAND para a sua implementação. b) Apresente expressões equivalentes que recorram apenas a portas NOR para a sua implementação. c) Apresente expressões equivalentes que recorram apenas a portas NAND de duas entradas para a sua implementação. d) Apresente expressões equivalentes que recorram apenas a portas NOR de duas entradas para a sua implementação. f1 = a.b f2 = a + b f3 = a.b.c f4 = a + b + c f5 = a .b + a. c + a.b Exercício 9: Um sistema de alarme Considere que pretende realizar um sistema para utilizar numa empresa de inspecção de veículos, em que, com base na recepção de quatro variáveis booleanas (ABCD), detecte as situações em que o carro não pode circular. Considera-se que a variável A está associada a uma deficiência grave, enquanto as três restantes entradas B, C e D, estão associadas a deficiências menores. a) Apresente a tabela de verdade da função que seja activada sempre que exista pelo menos uma deficiência grave ou duas menores. b) Recorra a mapas de Karnaugh para encontrar expressão simplificada. Exercício 10: Simplificação de funções através de mapas de Karnaugh Para cada uma das funções abaixo representadas: a) Apresente a sua representação equivalente recorrendo a listas de mintermos ou maxtermos, dependendo da situação; b) Simplifique as funções recorrendo a mapas de Karnaugh. f1(A,B,C,D) = Σ(1,4,5,6,12,14,15) f2(D,C,B,A) = Σ (2,3,10,11,12,13,14,15) f3(A,B,C,D) = Π(0,5,7,13,14,15) f4(D,C,B,A) = Π(0,2,5,7,8,10,13,15) f5(A,B,C) = ∑ (2,3,4,5) f6(A,B,C) = ∑ (2,3,4,5) + d (0,1) f7(C,B,A) = Π(0,1,6,7) f8(C,B,A) = Π(0,1,6,7) + d(2,3) Exercício 11: Implementação de funções booleanas Realize a montagem de uma das expressões (não elementares) encontradas num dos Exercícios 8, 9 ou 10, utilizando as bases de experimentação disponíveis no laboratório verificando os resultados obtidos comparando com a tabela de verdade respectiva. Para a detecção de eventuais falhas na montagem utilize as pontas de prova disponíveis no laboratório. DEE-FCT-UNL Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 3 (Trabalho com Relatório) Semana 4 de Outubro a 12 de Outubro Objectivos: Realização de funções booleanas utilizando descodificadores. Realização de funções booleanas utilizando multiplexers. Reutilização de módulos previamente obtidos em novas situações. Exercício 12: Realização de funções utilizando Descodificadores Considere o circuito integrado 74139, um duplo descodificador (invertido) com 2 linhas de endereço e 4 linhas de dados com activação (e.g. enable) usando lógica negativa (e.g. activo a zero). a) Utilizando o 74139 e alguma lógica adicional (se necessário), projecte um descodificador com três linhas de endereço e oito linhas de saída. b) Utilizando o descodificador realizado na alínea anterior e alguma lógica adicional, projecte um circuito que permita gerar a função: F(X3,X2,X1,X0) = X1X0 + X0X3 + X2X3 + X3X1 Exercício 13: Realização de funções utilizando Multiplexers PARTE I – Projecte um multiplexer de 4 entradas de selecção utilizando um descodificador e 4 multiplexers de 2 entradas de selecção com activação, e lógica combinatória elementar adicional. PARTE II – Considere agora as seguintes funções de 4 variáveis: 1. F(A,B,C,D) = Σ(1,4,5,6,10,12,14) 2. F(A,B,C,D) = Σ(1,5,7,11,14,15) + d(0,2,4) 3. F(D,C,B,A) = Π(2,3,10,11,12,13,14,15) a) Realize as funções usando o multiplexer projectado na primeira parte. b) Realize as funções apresentadas com base em multiplexers de 4 bits (i.e. 2 bits de selecção). c) Realize as funções utilizando unicamente um multiplexer de 2 bits de selecção e lógica adicional. d) Verifique experimentalmente, a solução da alínea c) para a função 1. DEE-FCT-UNL Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 4 (Trabalho com Relatório) Semana 13 de Outubro a 15 de Outubro Objectivos: Simplificação de funções booleanas através do método de Quine-McCluskey. Simplificação de funções booleanas incompletamente especificadas através do método de Quine-McCluskey. Realização de conversores de código. Exercício 14: Simplificação de funções através do método de Quine-McCluskey Para cada uma das funções apresentadas abaixo, efectue o seguinte: 1. F(A,B,C,D) = Σ(1,4,5,6,10,12,14) 2. F(A,B,C,D) = Σ(1,5,7,11,14,15) + d(0,2,4) 3. F(D,C,B,A) = Π(2,3,10,11,12,13,14,15) a) Simplificar a função recorrendo ao método de Quine-McCluskey. b) Comparar o resultado com aquele obtido por mapas de Karnaugh. Exercício 15: Conversor Código (Binário Natural -> Visualizador 8 segmentos) Quer-se criar um visualizador para alguns operadores lógicos e aritméticos, nomeadamente +, -, x, /, *, >, <, ∧, ∨. Os operadores são codificados através de 4 bits (x,y,w,z). Pretende-se então, realizar o circuito conversor de código binário natural para o código do visualizador de 8 segmentos, de acordo a figura abaixo, em que se representa o código presente à entrada e os segmentos que se necessitam activar para se poder visualizar o operador correspondente. h a g f b c e d 0 1 2 3 4 5 6 7 8 a) Apresente a tabela de verdade que permite obter o circuito conversor de código referido. b) Determine as respectivas expressões algébricas por simplificação através de mapas de Karnaugh, tanto pelos 1s como pelos 0s. c) Desenhe a estrutura de portas (i.e. esquemático) que realiza as diferentes funções. d) Implemente duas das funções: b, d, f, h. DEE-FCT-UNL Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 5 (Trabalho com Relatório) Semana 18 de Outubro a 22 de Outubro Objectivos: Realização de blocos comparadores. Realização de blocos somadores. Exercício 16: Comparadores Pretende-se realizar um comparador de dois números binários X e Y. O resultado deve ser apresentado através de três saídas: Z(ero) que é activada quando X=Y, m(enor) que é activada quando X<Y, e M(aior) que é activada quando X>Y. a) Projecte o circuito comparador para números X e Y de dois bits cada. b) Utilizando blocos comparadores (do tipo projectado na alínea anterior), projecte um comparador de dois números X e Y de quatro bits cada. Como resultado deverá apresentar o esquemático associado. c) Com base nos resultados anteriores, projecte agora um comparador de dois números X e Y de 8 bits cada. Como resultado deverá apresentar o esquemático associado. Exercício 17: Aritmética (Soma) Pretende-se projectar um circuito que realize a soma de 2 números X e Y de dois bits cada. PARTE I – RESOLUÇÃO “CLÁSSICA” a) Identifique o número de saídas necessárias e construa a tabela de verdade para cada saída. b) Determine as respectivas expressões algébricas simplificadas por mapas de Karnaugh. PARTE II – COMPOSIÇÃO MODULAR a) Projecte o circuito somador, utilizando somente blocos do tipo somador-completo de 1bit. b) Projecte o circuito somador, utilizando somente blocos do tipo semi-somador de 1bit e alguma lógica adicional que lhe pareça conveniente. c) Projecte um circuito somador que permita a soma de 2 números X e Y de quatro bits cada, utilizando somente blocos do tipo somador-completo de 1bit PARTE III – SOMADOR PARALELO a) Realize a montagem e verifique experimentalmente o funcionamento de um somador de números de 4 bits utilizando o circuito integrado 7483 DEE-FCT-UNL Departamento de Engenharia Electrotécnica Sistemas Lógicos (LEI) – 2010/2011 Laboratório 6 (Trabalho com Relatório) Semana 25 de Outubro a 29 de Outubro Objectivos: Realização de módulo somador-subtractor. Utilização de ambiente Xilinx WebPack de edição de esquemáticos e simulação. Realização de um latch assíncrono SR. Exercício 18: Somador-subtractor Considere um módulo somador de dois números binários de 4 bits, semelhante ao circuito integrado 7483 utilizado na aula anterior. PARTE I – Com base no referido módulo, projecte um somador/subtractor que utilize números em representação de complemento para 1. PARTE II – Partindo da solução anterior, projecte um somador/subtractor que utilize números em representação de complemento para 2. PARTE III – Editar os esquemáticos das soluções encontradas e proceder à sua simulação no ambiente WebPack da Xilinx disponível no laboratório. Nota: Recomenda-se a leitura de um documento com um tutorial sobre o ambiente, disponível na página moodle da disciplina. Exercício 19: Latch SR Tendo em atenção a tabela de funcionamento de um latch SR apresentada seguidamente. S 0 0 1 1 R 0 1 0 1 Qt+δ Qt 0 1 * a) Projecte um latch SR utilizando só portas do tipo NOR. b) Projecte um latch SR utilizando só portas do tipo NAND. DEE-FCT-UNL ~Qt+δ ~Qt 1 0 *

Baixar