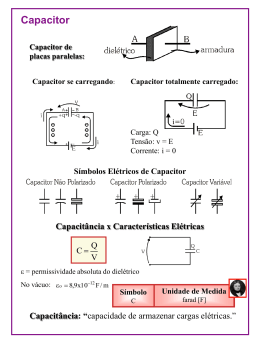

Dispositivos Lógicos Programáveis (PLD) • Os dispositivos lógicos programáveis (PLD – Programmable Logic Device) são circuitos integrados programáveis pelo usuário, que possui um grande número de portas lógicas (AND, OR, NOT), flip-flops e registradores que estão ligados em um mesmo CI. Dispositivos Lógicos Programáveis (PLD) Arranjos Lógicos Programáveis • Um arranjo lógico programável consiste de um circuito que possui uma estrutura interna baseada em um conjunto de portas AND-OR (o conjunto de portas AND e OR são chamados de arranjos). Arranjos Lógicos Programáveis • As entradas desse circuito são ligadas às entradas das portas AND e as saídas das portas AND são ligadas às entradas das portas OR e suas saídas representam as saídas do circuito Arranjos Lógicos Programáveis Memória PROM (Programmable ROM) • A memória ROM programável (PROM) é uma memória apenas de leitura que pode ser gravada uma vez pelo usuário através da queima dos fusíveis internos. Na memória PROM o arranjo AND é pré-definido em fábrica (arranjo fixo) e somente o arranjo OR é programável. Memória PROM (Programmable ROM) Na memória PROM o arranjo AND é prédefinido em fábrica (arranjo fixo) e somente o arranjo OR é programável. Memória PROM (Programmable ROM) Funções programadas Programação da saída O2 PAL - Programmable Array Logic X – ligações fixas - ligações programáveis • O PAL tem as a portas AND programáveis, ou seja, enquanto as portas OR são pré-conectadas em fábrica, então todas as portas AND podem ser programadas. Arranjos OR fixos Arranjos AND programáveis PLA - Programmable Logic Arrays X – ligações programáveis - ligações programáveis • Um PLA possui tanto a matriz de portas AND quanto a matriz de portas OR programáveis combinando as características de uma PROM e de um PAL Arranjos OR programáveis Arranjos AND programáveis Arranjos de Portas Programáveis • Os arranjos de portas programáveis são estruturas mais genéricas e versáteis que as baseadas na estrutura tradicional ANDOR dos arranjos lógicos programáveis. Arranjos de Portas Programáveis • A principal vantagem deste tipo de circuito é a possibilidade de reprogramação do comportamento de um circuito quantas vezes for necessária, ao contrário dos arranjos lógicos programáveis que só podem ser programados uma vez, ou seja, definida sua função lógica ela não poderá ser mudada. CPLD - Complex PLD • Os CPLDs podem ser vistos como dispositivos que utilizam em sua estrutura vários PLD´s (PLA ou PAL). Cada PLA ou PAL formam células que são interligadas através de conexões programáveis, CPLD - Complex PLD Os CPLDs podem ser vistos como dispositivos que utilizam em sua estrutura vários PLD´s (PLA ou PAL). Cada PLA ou PAL formam células que são interligadas através de conexões programáveis FPGA- Field Programmable Gate Array • É um dispositivo lógico programável que possui uma arquitetura baseada em blocos lógicos configuráveis, chamados de CLB (Configuration Logical Blocks) que são formados por portas lógicas e flip-flops que implementam funções lógicas. O FPGA também é formado por estruturas chamadas de blocos de entrada e saída (IOB – In/Out Blocks), os quais são responsáveis pelo interfaceamento entre as saídas provenientes das combinações de CLBs FPGA- Field Programmable Gate Array É um dispositivo lógico programável que possui uma arquitetura baseada em blocos lógicos configuráveis, chamados de CLB (Configuration Logical Blocks) que são formados por portas lógicas e flip-flops que implementam funções lógicas. Linhas de Roteamento Blocos de Entrada e Saída Blocos Lógicos Configuráveis Matriz de Roteamento FPGA- Field Programmable Gate Array O FPGA também é formado por estruturas chamadas de blocos de entrada e saída (IOB – In/Out Blocks), os quais são responsáveis pelo interfaceamento entre as saídas provenientes das combinações de CLBs Linhas de Roteamento Blocos de Entrada e Saída Blocos Lógicos Configuráveis Matriz de Roteamento FPGA- Field Programmable Gate Array A típica estrutura interna de um bloco lógico configurável de um FPGA, consiste em flip-flops, um determinado número de multiplexadores e uma estrutura de função combinatória para implementar as funções lógicas. Memória SRAM – Diagrama interno barramento de entrada célula de armazenamento decodificação de endereço barramento de saída – tri-state mux lógica de controle Memória DRAM – RAM dinâmica • É um tipo de memória volátil onde cada bit de dados é armazenado em um minúsculo capacitor, que conserva sua carga por apenas alguns milésimos de segundo, precisando ser continuamente recarregado. Memória DRAM – RAM dinâmica •Fabricada com tecnologia MOS •Alta capacidade (armazena informações em pequenos capacitores) •Baixo consumo Memória DRAM – Diagrama interno sw2 entrada de dados sw3 sw4 sw1 saída de dados C vref amplificador sensor Representação de uma célula de memória dinâmica Memória DRAM – escrita na célula sw2 entrada de dados sw3 sw4 sw1 saída de dados C vref amplificador sensor 1 – Lógica de leitura/escrita fecham as chaves sw1 e sw2, deixando sw3 e sw4 abertas 2- O dado de entrada é levado ao capacitor C (“1” carrega o capacitor, “0” descarrega o capacitor) Memória DRAM – Diagrama interno sw2 entrada de dados sw3 sw4 sw1 saída de dados C vref amplificador sensor 3 – A seguir as chaves são abertas de modo que o capacitor fique desconectado do restante do circuito 4- Idealmente o capacitor reteria sua carga indefinidamente, mas há sempre uma fuga pelas chaves desligadas, de forma que o capacitor perde sua carga gradualmente Memória DRAM – leitura da célula sw2 entrada de dados sw3 vcc sw4 vc sw1 C vref gnd saída de dados amplificador sensor 1 – Na leitura as chaves sw2 e sw3 e sw4 são fechadas e sw1 é mantida aberta 2 – Isso conecta a tensão armazenada no capacitor ao amplificador sensor que compara essa tensão com um valor de referência (Vref) para produzir uma tensão bem definida na saída de dados que define o nível “0” ou “1” (Vc > Vref saída de dados = “1” (vcc) ; Vc < Vref saída de dados = “0” (gnd)) 3 – O amplificador também restaura a tensão no capacitor, ou seja, o bit de dado na célula de memória é restaurado cada vez que é lido (refresh) Arranjo das células em uma DRAM (16 x 1) entrada de endereço da coluna A0 A1 decodificador de coluna A3 A2 decodificador de linha entrada de endereço da linha célula de memória 4 linhas 4 colunas Diagrama interno de uma DRAM (16 x 1) entrada de endereço da coluna A0 A1 CAS (columm address strobe) decodificador de coluna temporização e controle A3 A2 célula de memória decodificador de linha temporizaçao e controle entrada de endereço da linha (row address strobe) RAS 4 linhas 4 colunas Ciclo de escrita em uma RAM Dinâmica A B C D RAS CAS endereço LINHA COLUNA R/W Entrada de dados DADOS VÁLIDOS A – sinal RAS é aplicado indicando que no barramento existe endereço da linha B – sinal CAS é aplicado indicando que no barramento existe endereço da coluna C,D – pulso de R/W escreve o dado válido na célula de memória endereçada Ciclo de leitura em uma RAM Dinâmica A B C D RAS CAS endereço LINHA COLUNA R/W saída de dados DADOS VÁLIDOS A – sinal RAS é aplicado indicando que no barramento existe endereço da linha B – sinal CAS é aplicado indicando que no barramento existe endereço da coluna C,D – sinal R/W em nível “1” indica leitura e o dado válido da célula de memória endereçada aparece na saída de dados Módulos de Memória • Módulo SIMM (Single–in–line-module ) – é um cartão de circuito impresso com 30 ou 72 pontos de contatos nas duas faces do cartão. Usa chips DRAM de +5 V que variam de capacidade de 1 a 16 Mbits em encapsulamento para montagem em superfície • Módulo DIMM (Dual-in-line-module) – tem 168 pinos, 84 em cada face do cartão, são usados em PCs com barramento de dados de 64 bits em versões de +3,3V e +5V • SODIMM (Small-outline dual-in-line module) – usado em aplicações compactas como computadores laptop Exemplos de DRAM comerciais SIMM – 30 pinos SIMM – 72 pinos DIMM – 168 pinos pode ser apagada e reprogramada eletricamente no circuito byte a byte pode ser apagada e reprogramada eletricamente no circuito por setor ou em bloco pode ser apagada e reprogramada com luz UV fora do circuito (tem que ser retirada da placa) não pode ser apagada EEPROM Flash EPROM ROM ou PROM complexidade e custo do dispositivo Relações entre memórias semicondutoras não voláteis Aplicações de memória não voláteis • Memória bootstrap – Armazena programas denominados programas bootstrap cuja função é carregar o sistema operacional da memória de massa (disco) para a memória principal •Tabelas de dados – Armazenar tabelas de dados que não são alteradas, por exemplos tabelas trigonométricas(seno, coseno, tangente, etc) • Conversor de dados – Converte os dados expressos em um tipo de código em outro tipo de código (BCB, ASCII, EBCDIC, etc) • Gerador de funções – Funções booleanas diversas

Baixar