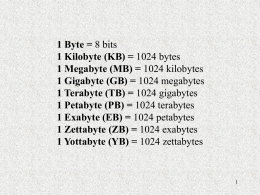

Arquitectura de Computadores II 8. BUS e Armazenamento 2004/2005 8.1. Bus Paulo Marques Departamento de Eng. Informática Universidade de Coimbra [email protected] Intel’s Chipset 850 MCH = Memory Controller HUB ICH = I/O Controller HUB 2 Existem diversos Buses e Controladores num sistema... 3 Transacção num BUS 4 Decisões no desenho de um BUS Option Bus width Data width Transfer size Bus masters Split transaction Clocking High Performance separate address and data lines wider is faster multiple data words have less bus overhead multiple (requires arbitration) Yes - separate request and reply packets allow higher bandwidth synchronous Low Cost multiplex address and data lines narrower is cheaper single word transfer is simpler single master (no arbitration) No - continuous connection is cheaper and has low latency asynchronous 5 Exemplo de dois I/O buses 6 Evolução dos barramentos de sistema 7 PCI e PCI Express Slots (x1) 8 PCI Express (Multiple Lanes – x16) 9 Arquitectura de Computadores II 8. BUS e Armazenamento 2004/2005 8.2. Armazenamento Paulo Marques Departamento de Eng. Informática Universidade de Coimbra [email protected] Discos 11 Mercado Desktop – Actualmente... dois standards PATA = Parallel ATA ATA = AT Attachment ATAPI = ATA Packet Interface SATA = Serial ATA 12 Transferências de Dados O processador tem, de alguma forma, conseguir ordenar as transferências de dados entre os discos e a memória Os comandos ATA representam a especificação dessas ordens de transferência e controlo Modos de transferência: Transferência programada (Modos PIO): o CPU está directamente envolvido nas transferências Transferência directa para memória (Modos DMA e UltraDMA): as transferências de dados são geridas por um controlador especial 13 Especificações ATA/ATAPI Modos PIO Relógio (ns) BW (MB/s) Especificação 0 1 2 3 4 600 383 240 180 120 3.3 5.2 8.3 11.1 16.7 ATA-1 ATA-1 ATA-1 ATA-2 ATA-2 Relógio (ns) BW (MB/s) Especificação 480 150 120 5.2 13.3 16.7 ATA-1 ATA-2 ATA-2 Relógio (ns) BW (MB/s) Especificação 240 160 120 90 60 40 30 16.7 25.0 33.3 44.4 66.7 100.0 133.3 ATA/ATAPI-4 ATA/ATAPI-4 ATA/ATAPI-4 ATA/ATAPI-5 ATA/ATAPI-5 ATA/ATAPI-6 ATA/ATAPI-7 Modos DMA (multiword) 0 1 2 Modos UltraDMA 0 1 2 3 4 5 6 16bits dados + 16 bits controlo Cabo de 40/80 condutores BW máxima = 133MB/s 14 SATA = Serial ATA Em vez de utilizar um conjunto de condutores paralelos, os comandos e dados são enviados e recebidos em série. Utiliza o mesmo conjunto de comandos (ATA) Largura-de-Banda: 150 MB/s (inicial) Ligação ponto-a-ponto, série (2 pares de cobre) Tensão de funcionamento mais baixa ( 0.6V) Connectores simples (7 pinos) Plug-and-plag (s/ jumpers, configurações master/slave) Hot-Swapable 15 Material para ler Computer Architecture: A Quantitative Approach, 3rd Ed. Secções 7.1, 7.2 (discos) e 7.3 R. Monteiro et. al., “Tecnologia dos Equipamentos Informáticos”, FCA Editora de Informática, Março 2004 Secção 2.3.3.1 (IDE/PATA e SATA) Secção 2.3.2.6 (PCI) 16 Algumas coisas que não discutimos... Hypertransport SCSI e SAS (Serial Attached SCSI) Norma para interligação de dispositivos rápidos que está a ser suportada por toda a gente excepto a Intel (AMD, nVIDIA, Apple, Cisco, Sun, Transmeta, Broadcom, etc.) Bus point-to-point, transmissão série BW = até 22.4GB/s (até 10x mais rápido do que PCI Express) SCSI Equivalente ao IDE para servidores SAS Equivalente ao SATA para servidores RAID Redundant Array of Inexpensive Discs Robustez e performance pela junção de vários discos Já estudado na cadeira de Sistemas Operativos 17

Download