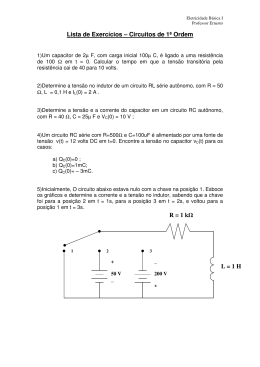

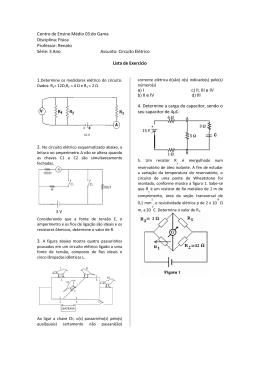

Departamento de Eletrônica e Computação ELC 1021 – Estudo de Casos em Engenharia Elétrica 4ª Lista de Exercícios – Circuitos RL e RC 1) Para cada um dos seguintes circuitos: a) verifique se a equação diferencial que descreve o comportamento do circuito está correta; b) resolva a equação diferencial, encontrando a corrente e a tensão sobre o indutor ou o capacitor; c) encontre a expressão da energia e da potência dissipada no resistor; d) faça um esboço dos gráficos da tensão, corrente, energia e potência no indutor ou no capacitor e e) explique o comportamento da tensão e corrente sobre o indutor ou capacitor no circuito. Nos nós e malhas dos circuitos foram empregadas as leis de Kirchhoff para correntes e tensões, respectivamente. Os valores dos componentes são R = 1x,y kΩ, L = 3xx µH e C = 1yy µF (x e y são os dois últimos algarismos de sua matrícula). a No nó a: vC + + R - C - − iC + iR = 0 iR iC dv ⎞ v ⎛ −⎜−C C ⎟ + C = 0 dt ⎠ R ⎝ vR Logo, b C⋅ dvC vC + = 0 dt R Figura 1 – Circuito RC. A tensão inicial no capacitor é 10 V. Na malha 1: a + vL − vL + vR = 0 iR iL L 1 b + R - ⎛ di ⎞ − ⎜ − L ⎟ + iL ⋅ R = 0 ⎝ dt ⎠ vR Logo, L diL + iL ⋅ R = 0 dt Figura 2 – Circuito RL. A corrente inicial no capacitor é 0,1 A. 2) Usando a solução geral para as respostas dos circuitos RL e RC, escreva as equações da tensão e da corrente no indutor ou capacitor, para os circuitos apresentados a seguir. Nos diagramas, considere R = R1 = 1x,y kΩ, R2 = 4x kΩ, R3 = 60 kΩ, C = 1xx µF, L = 2yy µH, VG = V2 = 20 V e V1 = 40 V (x e y são os dois últimos algarismos de sua matrícula). Faça um esboço do gráfico das equações encontradas. t=0 R Vg iL + - vL L Figura 3 – Circuito RL. A corrente do indutor antes que a chave seja fechada é 0 A. R1 V2 R2 iC + - vC t=0 V1 R3 C + Figura 4 – Circuito RC. Considere que no instante t = 0‐ s, o circuito está em regime permanente. t=0 R1 Vg R2 iL + - L vL Figura 5 – Circuito RL. Considere que no instante t = 0‐ s, o circuito está em regime permanente. 3) Foi medida a tensão sobre o capacitor de um circuito cujo diagrama esquemático é apresentado na Figura 6. R = 27 KΩ VG = 5 V + - t=0 vC C = 470 μF Figura 6 – Diagrama esquemático do circuito usado para medir a resposta a um degrau de um circuito RC. Os valores da tensão VC sobre o capacitor para t = 0 s a t = 60 s, em passos de 5 s, são mostrados na Tabela 1. Tabela 1 – Valores experimentais da tensão sobre o capacitor para o experimento cujo diagrama esquemático é apresentado na Figura 6. Tempo (s) 0 5 10 15 20 25 30 Tensão no Capacitor (V) 0,00 1,50 2,80 3,50 3,95 4,30 4,50 Tempo (s) 35 40 45 50 55 60 Tensão no Capacitor (V) 4,62 4,74 4,81 4,86 4,89 4,91 +VCC Porta inversora 1 0 R vC vC Nível lógico Do diagrama esquemático e com os dados obtidos experimentalmente: a) Encontre a equação teórica da tensão sobre o capacitor no tempo. b) Faça um gráfico (faça a mão e usando papel milimetrado) da curva teórica e experimental da tensão sobre o capacitor no tempo. Porque a diferença entre as duas curvas? c) Faça um gráfico com as curvas teóricas e experimentais da corrente do capacitor no tempo. d) Trace uma reta tangente à curva experimental da tensão no capacitor para t = 0 s. Escreva a equação ݕൌ ݕሺݐሻ desta reta. Qual o valor do tempo t para que o valor y desta reta seja 0? Determine a constante de tempo do circuito usando esta reta tangente a t = 0 s. Compare com o valor teórico da constante de tempo. 4) O circuito (que pode ser melhorado) apresentado na Figura 7 é usado para gerar um sinal RESET, inicializando um circuito digital toda vez que o mesmo é ligado. Considere que a tensão no capacitor é 0 V no momento em que a alimentação do circuito é ligada. A medida que o tempo passa, a tensão sobre o capacitor aumenta, tendendo a tensão de alimentação do circuito +Vcc, que neste problema será igual a 5,0 V. Neste problema será considerado que se a tensão no capacitor VC está entre 0,0 V e 0,8 V, a saída da porta inversora terá nível lógico 1 e se a tensão no capacitor VC estiver entre 2,0 V e 5,0 V a saída da porta terá nível lógico 0. Calcule valores de R e C para que o sinal RESET permaneça em nível lógico 1 pelo menos 0,1 s (no gráfico da Figura 7, t0 deve ser pelo menos 0,1 s). RESET 0 t0 t (s) C terra (0 V) Figura 7 – Ilustração de um circuito RC usado para gerar um sinal RESET toda vez que o circuito é ligado (a alimentação é ligada).

Baixar