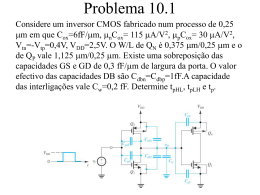

Capítulo 4 Conversão de corrente contínua em alternada A corrente quase contínua que o conjunto rectificador / bobina_alisamento fornece tem de ser modificada de forma a possuir características que lhe permitam ser injectada na rede eléctrica de distribuição pública. As características impõem: • Corrente alternada de componente fundamental sinusoidal e com 50Hz. • Baixo conteúdo harmónico. Para obter essas características a corrente passa por um inversor que a torna alternada e por um filtro que lhe baixa o conteúdo harmónico de alta frequência. L Idc C fonte corrente inversor corrente corrente sinusoidal filtro AC Figura 4.1 - Esquema geral da conversão dc-ac. A entrada em corrente do conversor DC/AC obriga ao uso de um inversor de corrente que tem características e funcionalidades diferentes do convencional inversor de tensão. Para minimizar o conteúdo harmónico o inversor de corrente é comandado através da técnica de modulação de largura de impulsos (PWM). Esta técnica permite mudar os harmónicos gerados pela comutação dos interruptores para frequências elevadas, simplificando assim a sua filtragem. Simultaneamente o PWM permite regular a amplitude da componente fundamental, evitando que a fonte de corrente contínua que alimenta o inversor tenha necessidade de ser controlada. 51 Conversão de corrente contínua em alternada 1 Inversor de corrente 1.1 Introdução Como o próprio nome indica o inversor de corrente é um dispositivo que permite transformar a corrente contínua com que é alimentado, em corrente alternada com determinadas características. Para o efeito, a corrente DC à entrada é cortada em impulsos através dos interruptores que ligam a entrada às três fases da saída. Idc g1h g2h g3h IR Idc IS IT g1L g2L g3L Figura 4.2 - Esquema básico do inversor de corrente. O comando dos interruptores tem de ser efectuado de modo a que as componentes espectrais sejam as desejáveis. O uso de interruptores rápidos e com capacidade de serem comandados nos dois estados (corte e condução) permite o uso da técnica de modulação de largura de impulsos (PWM - Pulse Width Modulation). Esta técnica permite o controlo da amplitude da componente fundamental da corrente de saída e afastar os harmónicos para frequências elevadas, simplificando a filtragem. Normalmente o inversor de corrente é ligado a uma carga que pode ser modelizada por um sistema de tensões trifásico equilibrado, e alimentado por uma fonte que consiste numa fonte de tensão DC em série com uma bobina de alisamento. L alisamento Idc g1h g2h g3h V dc inv V dc fonte g1L g2L IR VR IS VS IT VT g3L Figura 4.3 - Utilização normal do inversor de corrente. 52 Conversão de corrente contínua em alternada Dependendo do esfasamento entre a corrente de saída e a tensão de carga, os interruptores podem ter de suportar tensões inversas aos seus terminais. Isto leva a que os interruptores tenham de ser implementados com dispositivos que suportem as respectivas tensões. O inversor de corrente pode ser modelizado quer do lado DC, quer do lado AC, pelo esquema indicado na figura seguinte: Idc Idc V dc Inversor de corrente Valores que não dependem do inversor: IR VR IS VS IT VR (t) = VS (t) = 2 3 2 3 2 3 VC sin(2π . f r . t) VC sin(2π . f r . t − 23 π ) VT (t) = VC sin(2π . f r . t − 43 π ) I DC (t) = I DC VC ⇒ tensao composta da rede VT f r ⇒ frequencia da rede Parâmetros de controlo: im -> índice de modulação [0..1] θ -> esfasamento entre a corrente de saída e a tensão de carga [-π..π] Valores impostos pelo inversor: I R (t) = I DC sin(2 π.f r .t − θ).im I S (t) = I DC sin(2 π.f r .t − 23 π − θ).im I T (t) = I DC sin(2 π.f r .t − 43 π − θ).im VDC = 23 ⋅ im ⋅ VC ⋅ cos (θ) Figura 4.4 - Modelação do inversor de corrente. A relação entre a potência activa e reactiva vista pela carga, é dada pelo esfasamento imposto entre a corrente de saída e a tensão de carga. Se a corrente DC de entrada não depender do inversor (Ex: Se a fonte de corrente for ideal ou num caso mais realista e praticável, se a fonte de tensão DC de entrada for controlada de forma a manter a corrente constante), o trânsito de potência activa (P) e reactiva (Q) pode ser controlado independentemente um do outro através do índice de modulação (im) e do esfasamento (θ): P= Q= 3 2 ⋅ Idc ⋅ Vc ⋅ im ⋅ cos(θ) 3 2 ⋅ Idc ⋅ Vc ⋅ im ⋅ sin(θ) (4.1) onde Idc é a corrente DC de entrada e Vc é a tensão composta da carga. Se a corrente DC de entrada tiver de ser controlada através da tensão Vdc gerada pelo inversor à sua entrada, o trânsito das potências activa e reactiva fica condicionado uma vez que os parâmetros de controlo do inversor im e θ ficam relacionados pela seguinte fórmula: VDC = 3 2 im cos(θ) Vc (4.2) pelo que a sua escolha fica dependente da tensão que o inversor tem de gerar à entrada, deixando de ser independentes. 53 Conversão de corrente contínua em alternada 1.2 Regras para o controlo Ao contrário do inversor de tensão onde cada fase do inversor pode ser controlada individualmente e independentemente das outras duas1, no inversor de corrente o controlo das três fases tem de ser feito em conjunto. A primeira regra surge pela necessidade de haver sempre um caminho por onde a corrente da bobina de alisamento circular. Se em algum instante a corrente não tiver um circuito por onde fluir, criará uma sobretensão aos terminais do inversor de modo a ‘abrir caminho’ para a corrente fluir e dissipar a energia armazenada na bobina. Naturalmente esta sobretensão levará à destruição do inversor. Por este facto a primeira regra indica que em cada instante pelo menos um dos três interruptores superiores (g1h, g2h e g3h) e pelo menos um dos três interruptores inferiores (g1L, g2L e g3L) devem estar ligados para permitir um caminho à corrente. A segunda regra surge pela necessidade de se garantir que a forma de onda da corrente de saída das três fases depende unicamente do controlo do inversor, e não da tensão existente e criada pela carga nas fases. Suponha-se que num dado instante os interruptores g1h e g2L estão ligados e que na bobina passa a corrente Idc. Neste caso a corrente nas fases R, S e T está bem definida e vale respectivamente Idc, -Idc e zero. Idc Idc g1h g2h Idc g1L g2L I R = -I S = I dc g1h g3h g3L IR VR IS VS IT VT g2h g3h Idc g1L g2L IR VR IS VS IT VT ?? g3L I R - I S = I dc I R e I S desconhecidos pelo controlador Dependem das tensões V S e V T Figura 4.5 - Demonstração da necessidade de haver apenas 1 interruptor a conduzir nos grupos superior e inferior. Suponha-se agora que o interruptor g3L também está ligado. Neste caso a repartição da corrente Idc pelas fases R e T depende das tensões Vrs e Vts fluindo maioritariamente pela fase que oferecer menor resistência (menor tensão). Neste caso o comando do inversor nunca poderia garantir qual a corrente que está a circular nas 3 fases, uma vez que a distribuição de correntes dependeria também das tensões de carga. Realmente, se não fossem os díodos em serie (ver secção 3), neste caso onde estão 3 interruptores ligados, poderia inclusive, dar-se o caso de haver uma corrente de circulação da fase com maior tensão para a fase com menor tensão. 1 Na realidade a única regra a cumprir no caso do inversor de tensão é garantir que os dois interruptores de cada fase nunca estão simultaneamente ligados, de forma a evitar que a fonte de tensão DC seja curto-circuitada. 54 Conversão de corrente contínua em alternada Assim a segunda regra indica que apenas um interruptor de cada grupo superior e inferior pode estar a conduzir num dado instante. Estas duas regras combinam-se para gerar a regra de ‘ouro’ para o inversor de corrente: Em cada instante deve estar um e um só interruptor ligado em cada grupo, superior e inferior. Para se controlar a potência entregue à carga, em vez de se abrirem os 6 interruptores como no caso do inversor de tensão, fecham-se alternadamente os dois interruptores de cada fase efectuado assim uma ‘roda livre’ na corrente da bobina e isolando a corrente de carga da corrente de entrada DC. 1.3 Base de PWM O PWM usado neste trabalho baseia-se no método descrito por Ohnishi e Okitsu [8]. Segundo os autores, este PWM melhora a eliminação dos harmónicos de ordens mais baixas e o ganho para o lado DC (a tensão rectificada obtida é mais elevada e o “ripple” mais baixo) em relação às outras técnicas existentes. O PWM baseia-se no facto de apenas duas das três referências da corrente de saída serem independentes, uma vez que a soma das 3 correntes deve ser nula em cada instante de tempo. I (t ) + I (t ) + I (t ) = 0 R S T (4.3) Isto significa que depois de se definirem os pulsos de PWM para duas correntes, os pulsos para a terceira ficam automaticamente definidos. A construção do PWM desenvolve-se pela composição de duas moduladoras (M1 e M2) obtidas a partir das três correntes pretendidas (IR, IS e IT). Os sinais M1 e M2 são obtidos dividindo o período das correntes IR, IS e IT em seis intervalos iguais. Em cada intervalo, S1 e S2 são compostos tomando o valor absoluto dos sinais IR, IS e IT de menor valor absoluto. IR IS IT t M1 t M2 T1 T2 T3 T4 T5 T6 I R se t ∈ T1 − I se t ∈ T S 2 se t ∈ T I 3 S M1 ( t ) = − I se t ∈ T 4 T I se t ∈T 5 T − I R se t ∈ T6 I T se t ∈ T1 − I se t ∈ T T 2 se t ∈ T I 3 R M 2 ( t ) = − I se t ∈ T 4 R I se t ∈T 5 S − I S se t ∈ T6 t Figura 4.6 - Construção das moduladoras M1 e M2. As moduladoras obtidas vão modular duas portadoras (P1 e P2) com frequência: f P = ( 6. m + 3). f r (4.4) 55 Conversão de corrente contínua em alternada onde fr é a frequência das moduladoras e m é um número inteiro. A restrição da frequência das portadoras pela equação anterior, deve-se ao facto de ser necessário garantir algumas simetrias entre os 6 intervalos de tempo em que as moduladoras são divididas. A modulação é efectuada através da comparação entre a portadora e a moduladora em cada instante de tempo: 1 se m(t ) > p(t ) r (t ) = 0 se m(t ) ≤ p(t ) (4.5) onde r(t) é o resultado da modulação, m(t) é a moduladora e p(t) é a portadora. Figura 4.7 - Operação de modulação. A relação entre a amplitude das portadoras P1 e P2 e a amplitude das correntes de referência IR, IS e IT indica a relação entre a corrente IDC e a amplitude das correntes obtidas na saída do inversor. Para simplificar, mantêm-se a amplitude das portadoras igual a 1 e varia-se a amplitude das correntes de referência entre 0 e 1 através da sua multiplicação por um factor im, o qual se denomina por índice de modulação. Desta forma , o índice de modulação ao determinar a amplitude das correntes de referência: I R = im.sin(ω. t ) I S = im.sin(ω. t − 23 π ) I T = im.sin(ω. t − 43 π) (4.6) impõe a relação entre a corrente IDC e a amplitude das correntes obtidas na saída do inversor. Da modulação entre M1 e P1 resulta o sinal S1 e da modulação entre M2 e P2 o sinal S2. Um terceiro sinal: S3, é obtido através da negação de um “ou” lógico entre os sinais S1 e S2: S 3 = S1 + S 2 56 (4.7) Conversão de corrente contínua em alternada IDC g1h g2h g3h IRs ISs ITs g1L g2L g3L Figura 4.8 - Inversor de corrente. Os sinais de comando dos interruptores (g1h, g2h, g3h, g1l, g2l, g3l) são calculados a partir dos sinais S1, S2 e S3 e a partir do intervalo de tempo T1..T6 correspondente ao momento, a partir das seguintes expressões lógicas: g1h = T1 . S1 g2h = T1 . S 3 g3h = T1 . S 2 g1l = g2l = T1 g3l = + T2 T2 . S 3 + T2 . S1 T2 . S 2 + T3 . S 2 + T3 . S1 + T3 . S 3 + T3 + T4 + T4 . S 2 + T4 . S 3 + T4 . S1 + + + + T5 . S 3 T5 . S 2 T5 . S1 T5 + + + + T6 T6 . S1 T6 . S 2 T6 . S 3 (4.8) Analisando as expressões anteriores é possível verificar que este PWM garante o respeito das regras indicadas na Secção (1.2). Em cada instante de tempo existe sempre um e apenas um IGBT a conduzir nos ramos superior (g1h, g2h, g3h) e inferior (g1l, g2l, g3l) do inversor. Em cada intervalo de tempo os sinais S1 e S2 dão os instantes em que o inversor injecta corrente na saída. O sinal S3 dá os instantes em que o inversor desliga as saídas, ligando o IGBT superior e inferior do mesmo ramo, fazendo a corrente de entrada circular em roda livre. Verifica-se assim que este PWM controla a “quantidade” de corrente injectada na carga, variando o tempo em que o inversor está em roda livre. Para índices de modulação próximos da unidade S3 é pequeno, crescendo à medida que o im desce, ficando o inversor permanentemente em roda livre com o im igual a zero. As correntes de saída IRs, ISs e ITs são obtidas a partir do comando das gates e da corrente de entrada IDC. I Rs = I DC . ( g1h − g1l ) I Ss = I DC . ( g 2h − g 2l ) I Ts = I DC . ( g 3h − g 3l ) (4.9) Para controlar a fase das correntes de saída toma-se como referência a fase R da tensão da rede (VR) para a qual o inversor debita corrente. O esfasamento entre a tensão da rede e a corrente de referência IR, impõe a fase das correntes debitadas pelo inversor (IRs, ISs e ITs) em relação à tensão da rede. As figuras seguintes exemplificam o processo de construção do PWM. Para que os impulsos consigam ser visualizados com clareza no gráfico, optou-se por fazer m=3. Isto significa que 57 Conversão de corrente contínua em alternada as portadoras têm uma frequência de 21 vezes a frequência das correntes de referência (eq.4.4). Figura 4.9 - Geração dos sinais de comando do inversor e correntes obtidas na saída para im=1 58 Conversão de corrente contínua em alternada Figura 4.10 - Geração dos sinais de comando do inversor e correntes obtidas na saída para im=0.5 59 Conversão de corrente contínua em alternada Figura 4.11 - Geração dos sinais de comando do inversor e correntes obtidas na saída para im=0.1 1.4 Implementação do PWM O controlo dos interruptores é feito directamente a partir do µC. Como não é possível obter fórmulas explícitas, simples e rápidas de calcular os impulsos de controlo, optou-se por tabelar os sinais de comando. Uma definição que ajuda a compreender a forma de controlo do inversor implementada e a construção das tabelas de comando é o “estado de inversor” (est_inv). O est_inv indica se os interruptores estão ligados ou desligados e durante quanto tempo assim permanecem. A forma escolhida para representar o estado do inversor é a seguinte: 60 Conversão de corrente contínua em alternada estado = g1h ; g 2h ; g 3h ; g1l ; g 2l ; g 3l ; tempo estado = estado _ gates ; tempo _ estado (4.10) onde gij assume os valores 1 ou 0 consoante o respectivo interruptor está ligado ou desligado, e tempo representa a duração temporal do estado. O termo “estado_gates” tem origem no sinal que comanda o interruptor utilizado: o IGBT. Como é óbvio, é possível representar todo o comando de um inversor a partir de uma sequência de estados. Como exemplo, mostra-se a sequência de estados para o controlo em onda quadrada. Figura 4.12 - Forma de onda das correntes de saída para um controlo em onda quadrada e respectiva sequência de estados de controlo. Das Figuras 4.9 a 4.11 verifica-se que os sinais S1, S2 e S3 repetem-se a cada 1/6 de período das ondas de referência. O sinal S2 pode ser obtido se invertermos S1 no tempo, isto é: S2(t) = S1(-t). O sinal S3 é obtido a partir de S1 e S2 segundo a equação 4.7. Isto quer dizer que todo o controlo do inversor fica definido a partir do sinal S1 durante o primeiro 1/6 de período (T1). As transições do sinal S1 (durante T1) são dadas pelos pontos de intersecção dos sinais P1 e M1, conforme pode ser visto na figura seguinte. 2π m1 = im sin t T Os tempos de cruzamento t1..t14 são calculados por processos numéricos. Figura 4.13 - Transições do sinal S1 em função de P1 e M1. Os pontos de transição são obtidos resolvendo numericamente para x, equações da forma: 61 Conversão de corrente contínua em alternada a. x + b = im.sin( x ) (4.11) A partir da equação 4.8 e definindo os sinais: C1, C2, e C3 respectivamente como S1(t), S1(-t) e S 2 (t) ou S 2 (t) apenas durante o primeiro 1/6 período, é obtida a tabela de controlo dos interruptores do inversor que se representa na seguinte tabela. g1h g2h g3h g1L g2L g3L T1 c1 c3 c2 0 1 0 T2 1 0 0 c3 c2 c1 T3 c2 c1 c3 0 0 1 T4 0 1 0 c1 c3 c2 T5 c3 c2 c1 1 0 0 T6 0 0 1 c2 c1 c3 Tabela 4.1 - Sinais que devem ser aplicados no comando dos interruptores em função do intervalo de tempo respectivo. Como se verifica na Figura 4.14, existe uma mudança de estado sempre que C3 possui uma transição. Desta forma, os tempos de duração dos estados são dados pelos tempos do sinal C3, e como é óbvio repetem-se a cada 1/6 de período. Uma outra simetria que é visível no sinal C3 é a repetição na segunda metade do sinal, dos valores da primeira metade por ordem inversa. Figura 4.14 - Obtenção do sinal de comando dos interruptores durante o primeiro 1/6 de período (T1) Desta forma a obtenção da sequência de estados no caso do PWM utilizado é conseguida através dos tempos de transição do sinal C3 e do intervalo de tempo considerado (T1..T6) segundo a Tabela 4.1. A sequência total dos estados obtidos é indicada na próxima tabela. Os valores de tempo referidos são obtidos através da Figura 4.14. Naturalmente, os intervalos de tempo d1..d15 são calculados a partir dos intervalos de tempo do sinal C1 (k1..k15) que são obtidos a partir da modulação realizada como se mostra na Figura 4.13. 62 Conversão de corrente contínua em alternada Tabela 4.2 - Constituição da tabela de controlo do inversor para o PWM usado neste trabalho. A frequência das portadoras é de 45 vezes a frequência das correntes de referência. Os tempos d1..d15 são função do índice de modulação. 63 Conversão de corrente contínua em alternada Cada índice de modulação (im) possui uma tabela de controlo. Como é óbvio a sequência do comando dos interruptores é igual para todos os im. O que varia é o tempo de permanência em cada estado. Por outras palavras: o que varia com o im são os tempos d1..d15. A redundância de informação na tabela é grande. Para 174 “tempos” de estado, apenas 15 são diferentes e colocados por uma ordem perfeitamente definida. Isto sugere que se crie apenas uma tabela com a sequência do comando dos interruptores para todos os im, e uma tabela com os valores d1..d15 para cada im. No entanto, para o µC conseguir controlar o inversor com eficiência e para que a rotina que executa a mudança de estado seja executada no menor tempo possível, a construção das tabelas é feita de uma forma ligeiramente diferente, ficando com alguma redundância de informação. Durante o cálculo dos valores d1..d15 não se coloca nenhuma restrição ao seu valor. No entanto a duração de um estado está restringida às seguintes condições: • O tempo de um estado está limitado inferiormente pelo tempo mínimo de condução ou corte dos interruptores. Optou-se por fazer a duração mínima de condução ou corte dos IGBTs de 10µs. • O tempo de um estado está limitado inferiormente pelo tempo que a rotina do µC que executa a mudança de estado demora a ser executada. Esta rotina demora no máximo 8.6µs a ser executada. • A resolução do tempo de um estado está limitada à resolução do contador que implementa o controlo do tempo. Como o contador tem uma resolução de 200ns (rct), o tempo tem de respeitar a seguinte fórmula: tempo = nc . 200ns , n inteiro (4.12) onde nc representa o valor colocado no contador do µC. Como é óbvio as duas primeiras restrições são combinadas numa só, limitando a duração mínima a 10µs. Isto significa que o valor mínimo de nc é 50 (10µs/200ns). A influência destas restrições no tempo de duração dos estados de PWM é analisada na secção (1.7). 1.5 Comando do inversor O módulo de software responsável pelo comando do inversor recebe o índice de modulação através da variável global G_pwm_im e da função muda_im_pwm(). A fase é indicada através da função muda_fase_pwm(fase). Depois de receber estes dois valores, o módulo é responsável por todos os acontecimentos relativos ao comando do inversor. 64 Conversão de corrente contínua em alternada arranque_ inversor() paragem_ inversor() G_pwm_im muda_im_pwm() G_flag_erro_pwm_fase G_erro_pwm_fase Modulo de comando do inversor G_flag_erro_zero_rede G_erro_zero_rede G_flag_erro_pwm_sync_bruta G_erro_pwm_sync_bruta muda_fase_pwm(fase) inicializa_inversor() Figura 4.15 - Modelo do módulo de software de comando do inversor. As flags e as variáveis de saída indicam erros na sincronização do PWM com a rede eléctrica. O seu significado é explicado nas secções seguintes. Com o intuito de sincronizar a onda da corrente de saída com a onda da tensão da rede, existe um sinal de sincronismo (Ssync) que gera uma interrupção no µC sempre que a onda da tensão VR passa por zero no sentido ascendente. Esta interrupção vai servir não só para manter o sincronismo, mas também para medir o período real (em cada ciclo) da rede eléctrica. O módulo possui uma base de dados com as tabelas necessárias ao controlo do inversor para 1000 índices de modulação. A forma como as tabelas estão construídas e colocadas na memória do µC está optimizada para que a rotina responsável pela mudança de estado do inversor seja executada no menor tempo possível. Isto leva necessariamente a uma elevada redundância de informação contida na base de dados do PWM. A quantidade de memória ocupada pela base de dados não é preocupante, uma vez que a plataforma utilizada possui memória suficiente. Pelo contrário o tempo de execução da rotina que implementa a mudança de estado do inversor é um factor de extrema importância uma vez que limita o tempo mínimo de duração dos estados e é executada durante 174 vezes (o número de estados) durante cada período da rede eléctrica (20ms). Para além da base de dados com as tabelas de PWM e do sinal de interrupção para sincronismo o módulo de controlo do inversor utiliza ainda os seguintes recursos do µC: • Temporizador / Contador T6 - Para a contagem do tempo de duração dos estados, provocando uma interrupção que executa a mudança de estado sempre que o tempo de duração do estado anterior expira. • Temporizador / Contador T1 - Para a contagem do tempo que decorre entre duas interrupções consecutivas do sinal de sincronismo. Gera ainda uma interrupção que assinala um erro no caso do sinal de sincronismo não surgir ao fim de 26ms contados a partir da ultima passagem por zero detectada. • Temporizador / Contador T3 - Utilizado para implementar o controlo do esfasamento entre a corrente de saída e a tensão da rede. Controla o tempo que decorre entre uma interrupção de sincronismo Ssync (passagem por zero da tensão da rede) e a colocação na origem do PWM (passagem por zero da corrente de saída). • Porta P7 - Porta utilizada para controlar os interruptores do inversor (P7.0 P7.5) e manter o sincronismo do PWM com a rede (P7.6 e P7.7). 65 Conversão de corrente contínua em alternada • 2 bancos de registos (pwm_regs e sync1_regs) - Para processamento e armazenamento de dados entre chamadas de rotinas. A utilização de registos para armazenamento de informação entre chamadas de rotinas permite tornar essas rotinas mais rápidas uma vez que não é feito acesso à memória convencional. • Apontador DPP0 (“data page pointer 0”) - É utilizado para aceder à informação das tabelas do PWM como se fossem variáveis do tipo “near”. O acesso a variáveis através dos “data page pointer” (variáveis “near”) é mais rápido do que o acesso tipo “extended page” ou “extended segment”. A maior parte das rotinas responsáveis pelo comando do inversor foram escritas em assembly de modo a optimizar o tempo de execução. O código está descrito no Anexo C e encontra-se documentado. No entanto a sua total compreensão exige o conhecimento da arquitectura do C167 e do seu assembly. 1.5.1 Organização e armazenamento das tabelas de PWM A rotina que executa a mudança de estado do inversor utiliza o apontador DPP0 para aceder à informação necessária a cada estado: o estado dos interruptores (gates) e a duração do respectivo estado (tempos). Na Secção 1.4 foi visto que 15 valores (d1..d15) são suficientes para indicar o tempo de duração dos estados para cada índice de modulação (im). Aparentemente a melhor forma de construir as tabelas seria formar uma tabela de 15 valores para cada im. Esta tabela seria alternadamente percorrida nos dois sentidos sendo assim obtida a sequência correcta dos tempos. No entanto, isto leva a que a rotina que executa a mudança de estado tenha de incluir uma condição para verificar em que sentido está a percorrer a tabela. Isto significa um tempo de execução que pode ser poupado se a tabela for percorrida apenas num sentido. Desta forma, a tabela de tempos para cada im é constituída por 29 valores correspondentes a 1/6 de período das correntes de saída. Cada valor da tabela é armazenado em 16 bits. Para indicar o fim da tabela é colocado o valor FFFFh (valor negativo em complemento para dois). Embora 8 bits fossem suficientes, é mais rápido mover e operar 16 bits neste µC do que 8 bits. Alem disso para se usar 8 bits seria necessário baixar a resolução do contador de 200ns para 400ns, o que levaria a piorar a linearidade entre Vdc e im conforme é exposto na Secção 1.7. Atendendo a que o tamanho das tabelas de tempo é sempre o mesmo para cada im, o valor que indica o fim da tabela é dispensável se a rotina que executa a mudança de estado possuir um contador que sinalize que chegou ao fim da tabela. No entanto, incrementar e verificar o contador demora tempo. Assim cada tabela de tempo ocupa (29+1)∗2 = 60bytes. Deve ser notado que a tabela de tempos pode possuir valores com zero, correspondentes aos estados eliminados por terem uma duração inferior ao limite imposto. 66 Conversão de corrente contínua em alternada d1 d2 d3 ...... d14 d15 d14 ...... d3 d2 d1 FFFFh Figura 4.16 - Tabela com a duração dos estados do PWM. Os 29 valores correspondem aos estados durante 1/6 de período que depois se repetem para os restantes 5/6. A tabela é percorrida no sentido descendente e o seu final é sinalizado com o valor FFFFh. Cada im possui uma tabela deste tipo que ocupa 60bytes. Como a sequência de gates é sempre a mesma, aparentemente apenas seria necessário uma tabela de gates para todos os índices de modulação. No entanto a informação necessária a cada estado deve estar contida dentro do alcance do apontador DPP0. O DDP0 permite aceder apenas a uma página (16kb) de memória do µC. Como é óbvio as tabelas de tempo para os 1000 im não cabem em 16kb. Assim em cada página de memória onde existam tabelas de tempo, tem de existir uma tabela com a sequência de gates. A posição de gates relativamente ao início de cada página tem de ser a mesma, de modo a que o apontador que mantêm a posição actual de gates esteja sempre certo, independentemente da página a ser usada. 4 páginas são suficientes para guardar as tabelas de PWM, pelo que a tabela de gates é repetida 4 vezes no início dessas 4 páginas. A tabela de gates indica se os interruptores estão ligados ou desligados em cada estado do inversor. Como o sinal da porta do µC que controla os interruptores é invertido no condicionamento de sinal, um “0” indica que interruptor está fechado e um “1” indica que está aberto. Como existem 6 interruptores no inversor, seriam necessários apenas 6 bits para codificar o seu estado. No entanto a organização ao byte da memória do µC e atendendo a que neste µC é mais rápido mover e operar 16bits do que 8bits leva a que cada estado de gates ocupe 16bits. A tabela de gates é terminada com um zero. Desta forma a tabela ocupa (29∗6+1) ∗2=350bytes. Para localizar a tabela correspondente a um determinado im existem dois vectores que estão ordenados por ordem crescente do im a que se referem. Um dos vectores indica a página de memória, e o outro indica o deslocamento da tabela de tempos do respectivo im. 67 Conversão de corrente contínua em alternada A figura seguinte fornece o panorama geral da organização das tabelas. Os im são espaçados de 1/1000=0.001.Com a limitação inferior do tempo de duração dos estados, as tabelas de tempos para os im inferiores a 0,027 são iguais. Desta forma o im mais baixo que se tabela é o 0,027, que corresponde a manter o inversor permanentemente em “roda livre”. ptr_gates 015Dh 015Eh ptr_tempos_ RELOAD g 171 g 172 g 173 g 174 0000h d 1 0.294 d 2 0.294 d 3 0.294 d 14 d 15 d 14 offset DPP0 ..... g 171 g 172 g 173 g 174 0000h d 1 0.561 d 2 0.561 d 3 0.561 015Dh 015Eh 0.561 0.561 0.561 g g g g 1 2 3 4 ..... g 171 g 172 g 173 g 174 0000h d 1 0.828 d 2 0.828 d 3 0.828 ..... ..... d 14 d 15 d 14 Página D 0000h d 14 d 15 d 14 0.828 0.828 0.828 ..... ..... ..... d 3 0.294 d 2 0.294 d 1 0.294 FFFFh d 1 0.295 d 2 0.295 d 3 0.295 d 3 0.561 d 2 0.561 d 1 0.561 FFFFh d 1 0.562 d 2 0.562 d 3 0.562 d 3 0.828 d 2 0.828 d 1 0.828 FFFFh d 1 0.829 d 2 0.829 d 3 0.829 0.028 0.028 0.028 ..... d 14 d 15 d 14 0.295 0.295 0.295 0199h 019Ah ..... ..... im = 0.562 d 14 d 15 d 14 0199h 019Ah d 14 d 15 d 14 0.562 0.562 0.562 im = 0.829 0199h 019Ah im = 0.295 d 14 d 15 d 14 0.829 0.829 0.829 ..... ..... ..... ..... d 3 0.028 d 2 0.028 d 1 0.028 FFFFh d 3 0.295 d 2 0.295 d 1 0.295 FFFFh d 3 0.562 d 2 0.562 d 1 0.562 FFFFh d 3 0.829 d 2 0.829 d 1 0.829 FFFFh d1 d2 d3 im = 0.293 d 14 d 15 d 14 0.293 0.293 0.293 3F86h d1 d2 d3 im = 0.560 3F86h d 14 d 15 d 14 ..... 0.293 0.293 0.293 01D5h ..... ..... ..... 0.560 0.560 0.560 3F86h d1 d2 d3 d 14 d 15 d 14 ..... 0.560 0.560 0.560 01D5h ..... ..... ..... ..... ..... ..... 0.827 0.827 0.827 29AEh d1 d2 d3 im = 1.000 01D5h d 14 d 15 d 14 0.827 0.827 0.827 1.000 1.000 1.000 ..... ..... 1.000 1.000 1.000 ..... ..... ..... ..... d 3 0.293 d 2 0.293 d 1 0.293 FFFFh d 3 0.560 d 2 0.560 d 1 0.560 FFFFh d 3 0.827 d 2 0.827 d 1 0.827 FFFFh d 3 1.000 d 2 1.000 d 1 1.000 FFFFh pof(0.027) pof(0.028) pof(0.029) pof(0.030) 3FC1h DPP0 -> aponta para o inicio de uma das páginas A, B, C ou D DPP0 = *página ( im ) ptr_gates_RELOAD -> indica o offset page do inicio da tabela gates ptr_gates_RELOAD = 0 0 0 0 h ptr_tempos_RELOAD -> indica o offset page do inicio da tabela tempos do actual im ptr_tempos_RELOAD = *page_offset ( im ) page_offset -> vector para indicar o ptr_gates_RELOAD dos varios im página -> vector para indicar a página a ser utilizada para cada im 29E9h 29EAh page offset 3FC1h 3185h 3186h página im = 0.028 1 2 3 4 ..... ..... ..... ..... 3FC1h 015Dh 015Eh g g g g d 3 0.027 d 2 0.027 d 1 0.027 FFFFh d 1 0.028 d 2 0.028 d 3 0.028 ..... 01D5h 0.294 0.294 0.294 Página C 0000h ..... ptr_tempos im = 0.294 im = 0.027 0199h 019Ah 0.027 0.027 0.027 offset DPP0 ..... ..... d 14 d 15 d 14 1 2 3 4 gates g g g g ptr_gates_ RELOAD ..... g 171 g 172 g 173 g 174 0000h d 1 0.027 d 2 0.027 d 3 0.027 Página B 0000h im = 0.828 offset DPP0 im = 0.561 1 2 3 4 im = 0.827 gates 015Dh 015Eh g g g g gates Página A 0000h gates offset DPP0 ptr_gates -> indica o offset page do estado dos interruptores no proximo estado do inversor ptr_gates -> varia entre ptr_gates_RELOAD e ptr_gates_RELOAD+ 2 * 6 * 2 9 ptr_tempos -> indica o offset page da duração do proximo estado do inversor ptr_tempos -> varia entre ptr_tempos_RELOAD e ptr_tempos_RELOAD+ 2 * 2 9 3921h page_offset ..... pof(0.997) pof(0.998) pof(0.999) pof(1.000) pag(0.027) pag(0.028) pag(0.029) pag(0.030) página ..... pag(0.997) pag(0.998) pag(0.999) pag(1.000) Figura 4.17 - Organização das tabelas usadas na síntese do PWM. 1.5.2 Mudança de estado A mudança de estado do inversor é realizada através de uma rotina (gera_pwm()) chamada por interrupção. A interrupção é gerada pelo contador T6 sempre que o seu valor chega a zero (T6INT). 68 Conversão de corrente contínua em alternada Sempre que o contador T6 chega a zero, alem de gerar a interrupção, é recarregado automaticamente por hardware com o valor guardado no registo T6RELOAD (correspondente à duração do próximo estado), começando uma nova contagem decrescente. A rotina gera_pwm() quando for chamada devido ao tempo do estado i-1 ter expirado, deve efectuar a sobreposição de condução entre os estados i-1 e i, colocar o inversor no estado i e actualizar o registo T6RELOAD com o tempo de duração do estado i+1. Deve ser reparado que quando a rotina é chamada, já o T6 foi carregado com a duração do estado i que estava no registo T6RELOAD. O tempo do estado i que a rotina coloca em T6RELOAD, é corrigido através da soma de um valor de correcção (CORRIGE_TEMPO) ao valor retirado da tabela de tempos (tmp) (ver Secções 1.5.4.1 e 1.5.4.2). No caso do valor de tmp ser zero (devido ao seu tempo calculado ser inferior ao mínimo imposto) a rotina salta para o próximo estado e soma 2 vezes o valor de CORRIGE_TEMPO ao novo tmp de forma a que a correcção global aos 174 estados de um período se mantenha igual. Deve-se notar que a correcção do período do PWM vale 174*CORRIGE_TEMPO*200ns. A sobreposição de condução é conseguida efectuando um “and” entre o estado dos interruptores do estado i-1 e do estado i. É efectuado um “and” e não um “or” porque a lógica de comando dos interruptores é negada. Sequência Gates(x)= Gates(1)= Gates(2)= Sequência P7 -> 7 - de valores na tabela gates - g3L g2L g1L g3H g2H g1H 1 0 1 1 0 1 1 1 0 1 0 1 de valores na porta P7 do yC 6 5 4 3 2 1 0 1 0 1 1 0 1 <-> valor antes da rotina gera_pwm ser chamada 1 0 0 1 0 1 <-> valor de sobreposição 1 1 0 1 0 1 <-> valor depois da rotina acabar Figura 4.18 - Esquema para realizar a sobreposição de condução. Os apontadores para o início das tabelas gates e tempos são mudados pela rotina que muda o índice de modulação. O valor de correcção do período é mudado pelas rotinas de sincronização com a rede. Os apontadores actuais para as tabelas gates e tempos também são mudados pelas rotinas que mudam o índice de modulação e que sincronizam com a rede. A rotina foi escrita em assembly e foi optimizada de forma a correr no menor tempo possível. Para o efeito todas as variáveis foram mantidas num banco de registos (pwm_regs) e acedidas com o apontador DPP0 que é usado exclusivamente1 na síntese do PWM. 1 Deve-se ter muito cuidado em garantir, que as eventuais rotinas fornecidas por terceiros, não utilizem o apontador DPP0. 69 Conversão de corrente contínua em alternada Em regime normal, a rotina é executada em 7,10µs com uma sobreposição de condução de 1,95µs. Se a rotina encontrar um estado de duração nula, ou efectuar o reload1 da tabela de tempos é executada em 7.85µs com uma sobreposição de 2,70µs. Se a rotina efectuar um reload simultâneo às tabelas de tempos e gates é executada em 8,60µs com 2,70µs de sobreposição. 1 O reload de tabela significa que o ultimo valor foi obtido, pelo que é necessário voltar ao início da tabela. 70 Conversão de corrente contínua em alternada T6INTerrupt T6 = T6RELOAD T6 está em contagem decrescente e vai provocar uma interrupção T6INT quando chegar a zero gera_pwm Porta_P7 = Porta_P7 and Proxima_gate ( passo 1 ) Proximo_tempo = [ ptr_tempos ] ptr_tempos = ptr_tempos + 1 não Proximo_tempo = 0 aux_correcção = corrige_tempo Estado eliminado Avança para o próximo sim Proximo_tempo = [ ptr_tempos ] ptr_tempos = ptr_tempos + 1 ptr_gates = ptr_gates + 1 aux_correcção = 2 * corrige_tempo NOTAS: As tabelas de "tempos" não podem ter o primeiro valor igual a zero. O tempo que decorre entre os passos 1 e 2, é o tempo de sobreposição de condução aaa = [ ptr ] -> significa que aaa recebe o conteudo da memoria apontada por ptr . N o p r o g r a m a r e a l , a s s u m e - s e q u e DPP0 (data page pointer 0) está com o valor correcto. Proximo_tempo = FFFFh não sim Reload da tabela de tempos ptr_tempos = ptr_inicio_tempos Proximo_tempo = [ ptr_tempos ] ptr_tempos = ptr_tempos + 1 Porta_P7 = Proxima_gate ( passo 2 ) Proxima_gate = [ ptr_gates ] ptr_gates = ptr_gates + 1 Proxima_gate = 0 não sim Reload da tabela de gates ptr_gates = ptr_inicio_gates Proxima_gate = [ ptr_gates ] ptr_gates = ptr_gates + 1 T6RELOAD = Proximo_tempo + aux_correcção FIM gera_pwm Figura 4.19 - Fluxograma usado na rotina gera_pwm(). Esta rotina é executada por interrupção quando o contador T6 chega a zero. 71 Conversão de corrente contínua em alternada A prioridade da interrupção T6INT deve ser a mais alta possível de forma a minimizar os atrasos na mudança do estado do inversor. A única interrupção de nível superior é a do ADC que fica a funcionar via PEC. As interrupções do µC nunca são desactivadas para minimizar a latência da interrupção. Até agora não se utilizou um Sistema Operativo, mas no caso de se vir a utilizar é necessário ter em atenção o seu efeito na latência desta interrupção, uma vez que ao a inibir temporariamente pode estar a introduzir um conteúdo harmónico considerável. 1.5.3 Mudança de índice de modulação A mudança do índice de modulação é efectuada pela rotina muda_im_pwm() e consiste em colocar o apontador ptr_tempos_inicio para o início da tabela de tempos correspondente ao índice de modulação indicado pela variável global G_pwm_im, e colocar o DPP0 a apontar para a página correcta. O apontador para a tabela de tempos (ptr_tempos) é mudado de forma a apontar para o mesmo estado na sequência de PWM. EX: se o apontador indica a 5ª posição da tabela de tempos para im=0.4, e o im pretendido agora é 0.9, o apontador deve indicar a 5ª posição da tabela de tempos para im=0.9. O apontador para o início da tabela de gates (ptr_gates_inicio) não precisa de ser mudado porque as tabelas ocupam sempre a mesma posição nas 4 páginas ocupadas pelas tabelas de PWM. O mesmo se passa para o apontador actual de gates (ptr_gates). Para garantir a consistência dos apontadores no caso desta rotina ser interrompida pela gera_pwm(), é necessário modifica-los numa sequência de operações indivisível. Como é óbvio esta sequência deve ser executada o mais rapidamente possível para não afectar grandemente a latência da interrupção que chama gera_pwm(). A página das tabelas (gates e tempos) dos índices de modulação é obtida a partir da tabela página (Figura 4.17) e o offset da tabela gates é obtido a partir da tabela page_offset (Figura 4.17). A variável G_pwm_im (com valores entre 0 e 973 com incrementos de 1) indica a posição do índice de modulação pretendido (respectivamente 1 e 0.027 com incrementos de 0.001). A rotina é escrita em assembly e opera unicamente sobre os registos que guardam os valores dos apontadores pwm_regs e sobre o DPP0. 72 Conversão de corrente contínua em alternada muda_im_pwm Para se garantir a consistência dos dados, estas operações têm de ser realizadas sem serem interrompidas. É necessário garantir a sua atomicidade. aux = ptr_inicio_tempos guarda o offset inicial do im anterior pag = página( G_pwm_im ) off = page_offset( G_pwm_im ) obtem a pá gina e o offset do novo im ptr_inicio_tempos = aux ptr_tempos = ptr_tempos - aux + off DPP0 = pag FIM gera_pwm ptr_inicio_tempos ptr_tempos 1 2 3 4 5 6 tabela de tempos do im anterior 1 2 3 4 5 6 tabela de tempos do novo im apontadores antes da rotina ser executada ptr_inicio_tempos ptr_tempos 1 2 3 4 5 6 tabela de tempos do im anterior 1 2 3 4 5 6 tabela de tempos do novo im apontadores depois da rotina ser executada Figura 4.20 - Fluxograma usado para mudar o índice de modulação. Desta forma, para se mudar o índice de modulação do inversor é necessário actualizar a variável global G_pwm_im e executar a rotina muda_im_pwm(). 1.5.4 Adaptação do PWM às variações de frequência da rede eléctrica. Deve ser notado que as tabelas são construídas para uma frequência fixa: a frequência da rede eléctrica onde o sistema está ligado (neste caso 50Hz). Num sistema onde se requeiram correntes de saída com frequência variável, multiplicam-se os valores d1..d15 de forma a corrigir a frequência pretendida. Esta correcção dos tempos d1..d15 pode ser conseguida através da multiplicação valor a valor, ou através da variação do período do contador que executa a contagem do tempo. De uma forma ou de outra, o µC escolhido não é adequado para o efeito. No caso de escolhermos a primeira opção, uma plataforma baseada em DSP seria a mais aconselhável devido à facilidade e rapidez com que estes µP executam varias multiplicações. No segundo caso é necessário um µC que possua um contador com possibilidade de ajuste fino do seu período de contagem mantendo uma período aceitável para a resolução requerida. 73 Conversão de corrente contínua em alternada O µC utilizado consegue criar um contador com período variável através da concatenação/reload de dois contadores. No entanto a resolução do período de contagem seria muito grande para a aplicação em causa (o contador deste µC utilizado nesta aplicação possui um período de contagem de 200ns). Repare-se que ao fazer variar os tempos d1..d15 desta forma, o que se está a fazer é variar a frequência de comutação, uma vez que neste PWM a relação freq._corren._saída / freq_comutação é constante (neste caso vale 1/45). Para manter a frequência de comutação em valores aceitáveis seria necessário criar tabelas para varias relações freq._corren._saída / freq_comutação. Desta forma as grandes variações de frequência das correntes de saída são efectuadas através da selecção da tabela que contêm a frequência pretendida (entre fxmax e fxmin na Figura 4.21). Os ajuste finos de frequência são obtidos variando os tempos d1..dx . Figura 4.21 - Esquema básico para obtenção de frequência variável com um PWM tabelado. Embora o sistema seja definido para funcionar a 50HZ, o problema é que no local onde o sistema vai ser instalado, a frequência da rede eléctrica é caracterizada por grandes desvios de frequência. Esta variação é grande para efeitos da rede eléctrica, mas é um pequeno desvio se pensarmos num sistema a frequência variável. 1.5.4.1 Solução adoptada A solução encontrada para satisfazer este requisito foi somar/subtrair um pequeno valor aos tempos de duração de cada estado. Esta correcção faz variar a frequência das correntes na saída à custa de um ligeiro aumento dos harmónicos. Note-se que ao somar/subtrair um certo valor à duração de cada estado, o período da onda está a ser aumentado/reduzido. Esta correcção é realizada muito facilmente pelo µC uma vez que é executada através da soma de dois registos do µC através da rotina que realiza a mudança de estado do inversor: gera_pwm(). 74 Conversão de corrente contínua em alternada Como um período da corrente de saída é gerado através de 174 estados e a resolução do contador é de 200ns, o período obtido e a respectiva frequência são dados por: T = 20ms + n ∗ 174 ∗ 200ns 1 f = 20ms + n ∗ 174 ∗ 200ns (4.13) onde n representa o valor somado ao tempo de cada estado. Naturalmente, n é negativo para valores de f superiores a 50HZ. O µC para calcular n, utiliza o período medido da rede (Trede) da seguinte forma: n= Trede − 20ms 174 ∗ 200ns (4.14) Como é óbvio o valor de n tem ser truncado para um inteiro. Alguns valores de frequência obtida em função do valor de correcção são indicados na tabela seguinte: Tabela 4.3 - Valores de frequência obtida em função do valor de correcção. 1.5.4.2 Rotina calcula_correcao_periodo() O período real da rede Trede é medido através do timer T1 com uma resolução de 400ns e guardado na variável G_periodo. Desta forma o valor que ajusta o período do PWM ao período real da rede (n) é dado pela seguinte equação (ver eq.4.14): G _ periodo ∗ 400ns − 20ms 174 ∗ 200ns (4.15) G _ periodo − 50000 . ∗10 − 3 ∗ G _ periodo − 574.7 = 1149 87 (4.16) n= n= Pela equação anterior verifica-se que é necessário realizar uma divisão (ou uma multiplicação não inteira (float real)) para calcular o valor n . Como este valor é calculado a cada 20ms e uma divisão (ou multiplicação float) no C167 demora bastante mais tempo do que uma 75 Conversão de corrente contínua em alternada multiplicação simples de dois inteiros (words), aproveita-se o sistema de multiplicações inteiras do C167 para calcular n com uma única multiplicação inteira. 2 16 50000 G _ periodo − 50000 87 n= = 16 G _ periodo − 87 87 2 n≅ A multiplicação por 753 2 16 753 ∗ G _ periodo − 574 2 16 (4.17) (4.18) é realizada segundo o esquema no Anexo B. O valor de n é guardado no registo R1 do conjunto de registos sync1_regs (variável n_correcao_periodo). 1.5.5 Sincronismo com a rede e controlo da fase. Sempre que a tensão da fase R da rede eléctrica passa por zero no sentido ascendente, surge uma interrupção: passagem_zero_rede(). O timer T1 mede o intervalo de tempo que decorre entre duas interrupções consecutivas. Naturalmente este tempo indica o período da rede eléctrica (Trede). O valor de Trede também é utilizado para calcular o valor (n), que deve ser somado à duração de cada estado do inversor, pela rotina que implementa a mudança de estado: gera_pwm. O valor n é calculado pela rotina calcula_correcao_periodo(). Sempre que a medida do período da rede saí fora de um limite inferior ou superior (respectivamente 19ms e 21ms), é gerado um sinal de erro através da flag G_flag_erro_zero_rede, e a variável que indica o número de erros ocorridos é incrementada: G_erro_zero_rede. Este controlo do período medido, evita erros de sincronização provocados por interrupções intempestivas devidas a ruído. O timer T1 é um contador de 16 bits com uma resolução de 400ns. Isto significa que T1 pode medir intervalos de tempo até 26.3ms. Se ao fim de 26.3ms não surgir uma interrupção de passagem por zero da rede, o timer T1 fica em overflow e provoca uma interrupção: passagem_zero_rede_falhada(). Esta interrupção sinaliza o erro através da flag G_flag_erro_zero_rede e da variável G_erro_zero_rede. Devido à filtragem que é realizada no circuito que detecta a passagem por zero da rede, a interrupção é gerada com um determinado atraso em relação à verdadeira passagem por zero. A filtragem é necessária para evitar falsas detecções de passagem por zero. 76 Conversão de corrente contínua em alternada Fase R da tensão da rede Trede passagem_zero_rede() atraso tempo Figura 4.22 - Atraso nas interrupções da detecção de passagem por zero da tensão da rede provocadas pela filtragem. A compensação deste atraso é feita através da calibração do controlo da fase das correntes de saída do inversor. EX: para um esfasamento nulo, o tempo tfase (Figura 4.23) vale tcal. O controlo da fase é conseguido através do temporizador T3 que impõe o tempo que decorre desde o surgimento da interrupção de passagem por zero da rede até à passagem por zero do inversor. A passagem por zero do inversor num determinado instante significa que a passagem do ultimo estado (174) para o primeiro se dá nesse instante. Fase R da corrente do inversor Fase R da tensão da rede passagem_zero_rede() passagem_zero_rede() t cal T3 T3 t fase t fase estado 174 estado 174 estado 1 acerta_fase_pwm() estado 1 acerta_fase_pwm() Figura 4.23 - Controlo do esfasamento entre a tensão da rede e a corrente gerada pelo inversor. Durante a interrupção passagem_zero_rede() o timer T3 é carregado com o valor tfase (Figura 4.23) e posto em contagem decrescente. Quando T3 atingir o valor zero, surge uma interrupção (acerta_fase_pwm()) que é responsável por garantir que a passagem por zero do inversor se dá neste instante. 77 Conversão de corrente contínua em alternada O valor tfase é calculado pela rotina calcula_tempo_fase() e guardado na variável G_pwm_fase conforme é exposto na Secção 1.5.5.1. Como o período da rede pode sofrer ligeiras oscilações (Trede), o valor tfase tem de ser ajustado para o valor actual de Trede. Note-se que G_pwm_fase é calculado para um período de rede de 20ms. Este ajuste é realizado pela rotina calcula_tempo_fase_atribui_T3(), que coloca o resultado do ajuste directamente no timer T3. O timer T3 é posto em contagem decrescente pela interrupção passagem_zero_rede() através do bit de controlo T3R (T3R=1) e é parado pela interrupção acerta_fase_pwm() fazendo T3R=0. Desta forma, quando a interrupção passagem_zero_rede surgir, o bit T3R deve valer zero, significando que a interrupção acerta_fase_pwm() já foi atendida. Se tal não acontecer, significa que houve duas detecções de passagem por zero da tensão da rede consecutivas, sem que a interrupção acerta_fase_pwm() fosse atendida. Normalmente isto significa que o valor de tfase é maior que o período da rede. Se tal acontecer, significa que existem problemas na sincronização. O facto é sinalizado através da flag G_flag_erro_pwm_fase, e a variável que indica o número de erros ocorridos é incrementada: G_erro_pwm_fase. Como é óbvio a sincronização só é efectuada se não houver erros devido ao período da rede estar fora de limites ou devido ao valor tfase . É melhor não sincronizar o PWM do que sincronizá-lo com base em valores errados. A decisão de parar o sistema em caso de erro (sinalizado através das flags G_flag_erro_zero_rede e/ou G_flag_erro_pwm_fase) é tomada por outras rotinas que estão numa posição hierarquicamente superior na estrutura do controlador. O fluxograma da interrupção passagem_zero_rede() é indicado na Figura 4.24. 78 Conversão de corrente contínua em alternada interrupção externa CC0INT P2.0 passagem_zero_rede obtem o valor do contador e prepara-o para a próxima medida G_periodo = T1 T1=0 G_periodo > MINIMO e G_periodo < MAXIMO não Verifica se o período medido está dentro dos limites sim T3R = 1 sim não G_flag_erro_pwm_fase = 1 incrementa G_erro_zero_pwm_fase G_flag_erro_rede = 1 incrementa G_erro_zero_rede Verifica se o timer T3 já está parado. Se não estiver, significa que a interrupção que sincroniza o PWM ( acerta_fase_pwm() ) ainda não foi executada. calcula_correcao_periodo calcula_tempo_fase_atribui_T3 T3R=1 Obtem o valor que é necessário somar á duração de cada estado de forma a ajustar o período do PWM ao período real da rede Coloca no timer T3 o valor necessário para a fase pretendida. O valor é ajustado em função do período real da rede. Coloca o timer T3 a funcionar Quando o timer T3 chegar a zero, provoca a interrupção acerta_fase_pwm() que obriga o PWM a passar por zero nesse instante. FIM passagem_zero_rede Figura 4.24 - Fluxograma da interrupção passagem_zero_rede(). 1.5.5.1 Rotina muda_fase_pwm(fase) Esta rotina é utilizada para calcular o intervalo de tempo entre o surgimento da interrupção de passagem por zero (passagem_zero_rede()) e a passagem por zero do PWM (acerta_fase_pwm()). Quando a rotina passagem_zero_rede() é chamada, carrega o timer T3 com um determinado valor correspondente à fase pretendida. Quando o timer T3 chega a zero, chama a rotina acerta_fase_pwm() que se encarrega de garantir que o PWM passa por zero nesse instante. O intervalo de tempo é controlado pelo timer T3 com uma resolução de 400ns. 79 Conversão de corrente contínua em alternada T3 = 50000 0º 90º 180º 270º 360º θ T3 = 12500 T3 = 25000 T3 = 139∗ θ T3 = 37500 Figura 4.25 - Correspondência entre o valor de T3 e a fase. O valor de T3 correspondente a 360º é dado por: T3360 = 20ms = 50000 400ns (4.19) O valor de T3 correspondente a θº é dado por: T3θ = 50000∗ θ ≅ 139∗ θ 360 (4.20) Este valor tem de ser compensado devido ao atraso que o filtro introduz na interrupção. O valor que provoca um esfasamento nulo (tcal) tem de ser determinado experimentalmente. Naturalmente, o atraso do filtro é dado por atraso = 50000- tcal . passagem_zero_rede() T3 = 50000 θ1 T 3 = 1 3 9 ∗ θ 1 + t cal T 3 = t cal atraso atraso T 3 = 1 3 9 ∗ θ 2 - atraso T 3 = 1 3 9∗ θ 2 θ2 T 3 = 1 3 9∗ θ1 Figura 4.26 - Compensação devido ao atraso provocado pelo filtro no circuito de detecção de passagem por zero da rede. Desta forma, o valor real de T3 a que corresponde uma determinada fase é dado por: aux = 139∗ θ aux − atraso se aux ≥ atraso T3θ = se aux < atraso aux + t cal 80 (4.21) Conversão de corrente contínua em alternada A rotina recebe como parâmetro a fase pretendida (-360..360) e coloca o tempo correspondente na variável G_pwm_fase . O fluxograma da função é ilustrado na Figura 4.27. Naturalmente, a função só é chamada quando se pretende mudar o esfasamento. Função para mudar o esfasamento entre a corrente de saída do inversor e a tensão da rede fase = -360 .. 360 ; inteiro muda_fase( fase ) fase < 0 sim fase = fase + 360 139 = 20ms / 400ns / 360 aux = fase * 139 não aux > atraso G_pwm_fase = aux + tcal sim Os valores 'atraso' e 'tcal' são determinados experimentalmente. tcal + atraso = 50000 G_pwm_fase = aux - atraso FIM muda_fase( fase ) O resultado é guardado na variável global G_pwm_atraso Figura 4.27 - Fluxograma da rotina muda_fase_pwm(fase). 1.5.5.2 Rotina calcula_tempo_fase_atribui_T3() O tempo correspondente a uma determinada fase (obtido pela rotina muda_fase_pwm(fase) e guardado em G_pwm_fase) é calculado para um período de 20ms. Embora o período real da rede não se afaste muito deste valor, o desvio é suficiente para variar a fase correspondente ao valor de tempo guardado em G_pwm_fase . A rotina calcula_tempo_fase_atribui_T3() é chamada pela rotina passagem_zero_rede() a cada período da rede eléctrica e tem como objectivo ajustar o valor de G_pwm_fase (correspondente a uma dada fase) em função do período real da rede indicado em G_periodo (medido a cada período da rede). A seguir deduz-se a relação entre G_pwm_fase e o valor correcto n, em função do período real da rede G_periodo : 20ms θ 400ns 360 o TREAL θ G _ periodo∗400ns θ n= o = 400ns 360 400ns 360 o G _ pwm_ fase = 81 Conversão de corrente contínua em alternada n= G _ pwm_ fase∗ G _ periodo 50000 (4.22) Para evitar a divisão por 50000 ou a multiplicação real por 2 E - 5 é utilizado o estratagema indicado no Anexo B. G _ pwm_ fase∗ G _ periodo ∗42951 16 2 G _ pwm_ fase∗ G _ periodo n= ≅ ∗2 (4.23) 16 50000 2 A rotina é escrita em assembly e o valor n é guardado directamente no timer T3. 1.5.5.3 Rotina acerta_fase_pwm() Esta rotina é responsável por manter a passagem por zero da corrente de saída do inversor (passagem do ultimo estado do inversor (174) para o primeiro) no instante em que é chamada. Deste modo não será um exagero afirmar que esta rotina é o coração do sistema de sincronização com a rede. A sincronização é feita de dois modos distintos: • Sincronização suave; • Sincronização abrupta. A escolha entre os dois tipos de sincronização é feita com base no nível de “dessincronização” entre a passagem por zero das correntes de saída do inversor (PWM) e a passagem por zero pretendida (instante em que a rotina acerta_fase_pwm() é chamada). Sempre que a dessincronização é superior a um determinado intervalo de tempo, é realizada uma sincronização abrupta. Naturalmente no caso contrário é realizada uma sincronização suave. A quantificação do nível de dessincronização é feita com base nos estados do inversor. Na Figura 4.28 é ilustrado o princípio da quantificação. 82 Conversão de corrente contínua em alternada nº do estado do inversor ... 173 174 1 2 ............. 86 87 88 89 ............. 173 174 1 2 ......... fase R da corrente de saída do inversor PWM sincrono 169 170 171 172 173 174 1 2 3 4 5 6 chamada de acerta_fase_pwm() PWM adiantado requer sincronização suave 169 170 171 172 173 174 PWM adiantado requer sincronização abrupta 1 2 3 4 5 6 169 170 171 172 173 174 1 PWM atrasado requer sincronização suave 169 170 171 172 173 174 1 2 3 4 5 6 2 3 4 5 6 PWM atrasado requer sincronização abrupta 169 170 171 172 173 174 1 2 3 4 5 6 Figura 4.28 - Quantificação do nível de dessincronização do PWM. Desta forma, sempre que a dessincronização do PWM excede 3 estados é realizada uma sincronização abrupta. Os 3 estados correspondem a um intervalo de tempo de aproximadamente 200µs (angulo de 3.5º). Uma sincronização suave é feita através de uma ligeira modificação do período do PWM. Esta modificação do período, permite que o ponto de passagem por zero do PWM, deslize face ao ponto de passagem por zero da rede. Se o PWM estiver adiantado, o seu período deve ser aumentado de modo a que a sua passagem por zero deslize em direcção ao instante em que a rotina acerta_fase_pwm() é chamada. Naturalmente, se o PWM estiver atrasado é necessário diminuir ligeiramente o seu período. A modificação do período do PWM não pode ser muito grande sobe pena de levar à instabilidade no controlo. Se o nível de dessincronização for muito elevado (maior que 3 estados) o tempo de sincronização será grande. Desta forma é necessário ter um método de sincronização mais rápido: a sincronização abrupta. Uma sincronização abrupta consiste em obrigar a que o próximo estado do inversor seja o primeiro, independentemente do seu estado actual. Para a rotina acerta_fase_pwm() decidir como deve sincronizar o PWM, tem de identificar o estado em que o PWM se encontra. Os 174 estados são agrupados em três grupos: • PWM adiantado (estados 72,173 e 174); • PWM atrasado (estados 1, 2 e 3); • PWM dessincronizado (estados 4 a 171); 83 Conversão de corrente contínua em alternada Os três grupos são identificados por dois bits que são agregados ao estado das gates do estado do inversor. Desta forma, a tabela de gates alem de conter a informação sobre os IGBTs que estão a conduzir, também identifica qual o grupo a que o estado actual pertence. Deve ser notado que esta informação só tem validade quando a rotina acerta_fase_pwm() é chamada, uma vez que as noções de adiantado, atrasado e dessincronizado só fazem sentido nessa altura. Os dois bits que identificam os três grupos são transferidos juntamente com os seis bits que controlam os IGBTs para a porta P7 do C167. Como é óbvio, estas portas não podem ser utilizadas como entradas/saídas para outra função. Desta forma a rotina acerta_fase_pwm() apenas precisa de ler os bits nº6 e 7 da porta P7 para identificar a que grupo pertence o estado actual. tabela de gates atrasado dessincronizado adiantado 7 estado 6 grupo 5 4 3 2 1 0 g1H g2H g3H g1L g2L g3L 1 2 3 4 5 6 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 0 0 1 0 0 0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 0 169 170 171 172 173 174 0 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 1 0 1 bit Porta P7 grupo g1H g2H g3H g1L g2L g3L P7.7 P7.6 P7.5 P7.4 P7.3 P7.2 P7.1 P7.0 Figura 4.29 - Identificação do grupo do estado actual do PWM. A variação do período do PWM para a sincronização é feita de modo semelhante ao ajuste do período do PWM ao período da rede eléctrica (secção 1.5.4.1). Ou seja, através da soma/subtracção de um tempo à duração de cada estado. Desta forma a variável que indica o tempo total de correcção do período do PWM (CORRIGE_TEMPO, secção 1.5.2) é composta por duas componentes: • Ajuste do período do PWM ao período da rede eléctrica (n_correcao_periodo); • Ajuste do período do PWM para sincronização suave (n_sincr_periodo). A componente n_sincr_periodo é limitada a ± 2 para que o sistema não se torne instável. Com 174 estados e uma resolução no contador de 200ns, isto significa uma variação no período de ± 174∗2∗200ns = 69.6 ys . O valor ± 2 foi determinado experimentalmente. Com a variável n_sincr_periodo limitada ± 2, a sincronizações abruptas são quase inexistentes, surgindo apenas quando existem variações bruscas da frequência, o que naturalmente, raramente acontece na rede eléctrica. 84 Conversão de corrente contínua em alternada O fluxograma da rotina acerta_fase_pwm() é ilustrado na Figura 4.30. A paragem do timer T3 é necessária para evitar que a rotina fosse chamada consecutivamente por overflow do timer T3 no caso de não haver detecções de passagem por zero da rede. O bit T3R também é utilizado pela rotina passagem_zero_rede() para determinar se a rotina acerta_fase_pwm() já foi atendida. T3INTerrupt T3 gera a interrupção quando decorrer o tempo pretendido entre a passagem por zero da rede e paasagem por zero do PWM acerta_fase_pwm T3R = 0 Pára o timer T3 Está dessincronizado. Requer uma sincronização abrupta grupo = 0 0 sim coloca_PWM_origem não Está adiantado. grupo = 1 0 n_sincr_periodo = 0 sim Aumenta período G_erro_pwm_sync_bruta = G_erro_pwm_sync_bruta + 1 não n_sincr_periodo = n_sincr_periodo + 1 Está atrasado. grupo = 0 1 G_flag_pwm_sync_bruta = 1 sim Diminui período n_sincr_periodo >2 n_sincr_periodo = n_sincr_periodo - 1 não n_sincr_periodo < -2 não não sim Incrementa a variável que indica o numero de sincronizações abruptas e sinaliza a ocorrencia com a flag. n_sincr_periodo = 2 sim n_sincr_periodo = -2 CORRIGE_TEMPO = n_correcao_periodo + n_sincr_periodo FIM acerta_fase_pwm Figura 4.30 - Fluxograma da rotina acerta_fase_pwm(). No caso do PWM estar dessincronizado, é realizada uma sincronização abrupta: a variável n_sincr_periodo é colocada a zero e a rotina coloca_PWM_origem() é chamada. A rotina coloca_PWM_origem() consiste em colocar os apontadores actuais para as tabelas de gates e tempos de modo a que o próximo estado seja o primeiro. Para que a mudança se faça o mais 85 Conversão de corrente contínua em alternada rapidamente possível, o temporizador que mede a duração dos estados (T6), é colocado a zero, de modo a gerar a interrupção neste instante. Como é óbvio, uma sincronização abrupta é bastante violenta para o conteúdo harmónico das correntes de saída do inversor. Felizmente este tipo de sincronização só surge quando existem variações muito rápidas da frequência da rede eléctrica. 1.5.5.4 Inicialização, arranque e paragem do inversor A inicialização das rotinas e variáveis que comandam o inversor é efectuada pela rotina inicializa_inversor(), que se encarrega de preparar as portas do µC, os timers, as interrupções, etc. O timer T6 só é posto em funcionamento no arranque (não existem mudanças de estado, pelo que os seis IGBTs continuam desligados). O arranque do inversor é feito pela rotina arranca_inversor(). O arranque é efectuado com o índice de modulação máximo, e um esfasamento nulo. O arranque é feito sincronamente com a rede da seguinte maneira: • A interrupção de passagem por zero é permitida e o timer T1 que mede o período da rede é ligado; • Quando a interrupção surgir o timer T3 é carregado com o valor correspondente a um esfasamento nulo; • Quando o timer T3 chegar a zero, permite o funcionamento do timer T6 que controla a duração dos estados de PWM. (Nesta altura os apontadores das tabelas de PWM apontam para a passagem por zero de PWM) A paragem do inversor é realizada pela rotina paragem_inversor() que inibe a interrupção de passagem por zero da rede eléctrica, pára os timers T1, T3 e T6, e desliga os seis IGBTs. É preciso cuidado ao desligar o inversor devido à corrente IDC na bobina de alisamento. Antes de desligar o inversor é necessário ligar o IGBT de protecção. 1.5.5.5 Comando do IGBT da protecção DC O comando do IGBT de protecção é realizado por três rotinas cuja função é óbvia: • inicializa_protecao_dc(); • activa_igbt_protecao(); • desliga_igbt_protecao(); Deve ser notado que o IGBT de protecção também pode ser activado directamente pela detecção de sobretensão e pelo sinal de erro do inversor. 86 Conversão de corrente contínua em alternada 1.6 Características do PWM Nas análises seguintes assumem-se as seguintes condições: • A saída do inversor está ligada a uma fonte de tensão trifásica e perfeitamente sinusoidal. Isto quer dizer que se desprezam os efeitos do filtro AC, das impedâncias da rede e dos eventuais harmónicos da rede. • O inversor é alimentado por uma fonte ideal de corrente contínua. Isto quer dizer que a corrente de entrada é perfeitamente constante. • A frequência de comutação do inversor é de 50 (6*m+3; m=7) vezes a frequência das correntes de referência. Como as correntes de referência tem 50Hz, as portadoras tem 2250Hz. • As comutações da corrente são ideais: ° As comutações dão-se em tempo nulo. ° Não existe sobreposição de condução. • Não existem tempos mínimos de condução e/ou de corte. Isto quer dizer que o tempo de condução ou de corte de um dado interruptor pode ser tão pequeno quanto o PWM o exija. Estas assumpções são válidas numa primeira abordagem e servem para estudar as características do PWM se os componentes que constituem o inversor forem ideais. 1.6.1 Harmónicos da corrente de saída As figuras 4.31 a 4.33 mostram o espectro típico das correntes na saída do inversor. O espectro relativo é obtido através de: I ( n) harm(n) = 20 * log I (1) ( DB) (4.24) onde harm(n) é o valor do espectro relativo do harmónico n, I(n) é o harmónico número n e I(1) é a componente fundamental. Naturalmente o valor do espectro relativo da componente fundamental é sempre zero. Esta forma de representar logaritmicamente o espectro torna mais simples a ánalise do “peso” das componentes harmónicas face à componente fundamental na forma de onda analisada. A representação gráfica logarítmica tem a vantagem de poder representar no mesmo gráfico, valores muito diferentes entre si, sendo possível analisar a sua relação. Repare-se que a relação entre os harmónicos e a componente fundamental é dada por: harm(n) I ( n) = 10 20 I (1) (4.25) o que significa que se harm(n)=-20, o harmónico I(n) é 10 vezes mais pequeno que I(1). 87 Conversão de corrente contínua em alternada im = 1 im = 0.5 im = 0.5 Figura 4.31 - Espectro das correntes de saída do inversor para vários índices de modulação. 88 Conversão de corrente contínua em alternada im = 1 im = 0.5 im = 0.1 Figura 4.32 - Espectro relativo das correntes de saída do inversor para vários índices de modulação. 89 Conversão de corrente contínua em alternada im = 1 im = 0.5 im = 0.1 Figura 4.33 - Espectro relativo das correntes de saída do inversor para vários índices de modulação (zoom das fig:.4.32 ) Analisando os gráficos verifica-se que espectro apenas possui as componentes número: 6i - 1 e 6i + 1. Isto é: não possui harmónicos pares nem os múltiplos de 3. Os 5º, 9º e 11º são sempre inferiores a -50db ( 300 vezes mais pequenos que a fundamental) 90 Conversão de corrente contínua em alternada O espectro possui componentes significativas em torno das frequências múltiplas da frequência das portadoras P1 e P2 (fP) Esta frequência corresponde ao harmónico número nfP = 6m+3 conforme a equação (4.4). No caso em ánalise m=7 sendo nfP = 45. Em torno de nfP as componentes mais significativas são as de ordem nfp ± 2 e nfp ± 4 . Em torno de 2.nfP as componentes mais significativas são as de ordem 2.nfp ± 1 , 2.nfp ± 5 e 2.nfp ± 7 . Figura 4.34 - Evolução da componente fundamental e dos harmónicos nfp ± 2 e nfp ± 4 com o índice de modulação. Da figura 4.34 conclui-se que a componente fundamental da corrente de saída varia linearmente com índice de modulação (im). Os harmónicos nfp + 2 e nfp − 2 são iguais, o mesmo se passando com os harmónicos nfp + 4 e nfp − 4 . I saida RMS fundamental = Figura 4.35 - Evolução dos harmónicos 1 .I DC .im 2 (4.26) 2.nfp ± 1 , 2.nfp ± 5 e 2.nfp ± 7 .com o índice de modulação 91 Conversão de corrente contínua em alternada Figura 4.36 - Evolução dos harmónicos relativos (DB) do 13º até ao 49. Figura 4.37 - Evolução dos harmónicos relativos (DB) do 53º até ao 67. Figura 4.38 - Evolução dos harmónicos relativos (DB) do 71º até ao 97. 92 Conversão de corrente contínua em alternada As componentes entre a fundamental e nfp - 2 são desprezáveis: inferiores a -30db. ( 30 vezes mais pequenos que a fundamental) A corrente de saída do inversor só depende do índice de modulação. O seu esfasamento relativamente à tensão de carga só influencia a tensão à entrada como se verá na próxima secção. 1.6.2 Tensão à entrada Tensão de carga: IDC g1L g2L g1L VR IRs ISs VDC g1L g2L g1L VS VT VR = VS = VT = 1 3 1 3 1 3 Vc pico .sin(2 π. f r .t ) Vc pico .sin(2 π. f .r .t − 13 2 π ) Vc pico .sin(2 π. f .r .t − 23 2 π) Tensão à entrada: Vdc ITs Figura 4.39 - Esquema utilizado para analisar a tensão à entrada do inversor A partir daqui, Vdc(t) representa a forma de onda da tensão à entrada do inversor e VDC o seu valor médio . As figuras seguintes mostram a forma de onda da tensão Vdc(t) para vários im e vários esfasamentos (θ) entre a corrente de saída e a tensão de carga. (O esfasamento é dado tomando como referência a fase R da tensão de carga: Vr). Para melhor visualização dos impulsos de Vdc(t) nos gráficos, optou-se por fazer a frequência das portadoras igual a 21 vezes a frequência de referência (m=3 na eq.4.4). A tensão Vdc(t) é dada pela seguinte expressão em função do comando dos interruptores e da tensão de carga: Vdc (t ) = ( g1h − g1l ).VR + ( g 2h − g 2l ).VS + ( g 3h − g 3l ).VT (4.27) 93 Conversão de corrente contínua em alternada Figura 4.40 - Forma de onda da tensão Vdc em função da tensão da rede e das correntes do inversor 94 Conversão de corrente contínua em alternada Figura 4.41 - Comparação da tensão gerada à entrada do inversor para vários índices de modulação e esfasamentos. Pelas figuras anteriores, verifica-se que Vdc(t) se repete a cada 1/6 de período das tensões de carga. O espectro de Vdc(t) é mostrado nas figuras seguintes. Apenas possui componentes de ordem par 6i. As componentes mais significativas encontram-se em torno da frequência das portadoras em nfp ± 3 , 2.nfp ± 6 e 2.nfp . O espectro é analisado com frequência das portadoras (P1 e P2) correcta (m=7 na eq.4.4). Como é óbvio, o espectro relativo de Vdc(t) está referido à componente contínua do sinal. 95 Conversão de corrente contínua em alternada im=1 DB im=0.5 DB im=0.1 DB Figura 4.42 - Espectro e espectro relativo da tensão à entrada do inversor para fase=0o e vários índices de modulação. As próximas figuras representam a evolução da componente contínua e dos harmónicos mais significativos de Vdc(t) em função do índice de modulação e do esfasamento entre a corrente de saída e a tensão de carga. 0 (fundamental) 90 42=48 84=96 Numero harmonico Figura 4.43 - Evolução da componente contínua e dos principais harmónicos da tensão à entrada do inversor em função do índice de modulação para um esfasamento nulo. 96 Conversão de corrente contínua em alternada im=1 im=0.75 im=0.5 im=0.25 Fase Figura 4.44 - Evolução da componente contínua da tensão à entrada do inversor em função do esfasamento para vários índices de modulação. Das figuras anteriores conclui-se que a componente contínua da tensão gerada à entrada do inversor é dada pela seguinte equação: VDC = 15 . im cos(θ) Vs pico VDC = 15 . 2 im cos(θ) Vs VDC = 15 . 2 3 im cos(θ) Vc = (4.28) 3 2 im cos(θ) Vc onde im representa o índice de modulação, θ o esfasamento entre a corrente de saída e a tensão de carga e Vs pico, Vs e Vc representam respectivamente as tensões de carga: simples de pico, simples e composta. 1.6.3 Tensões aos terminais dos interruptores Como se vê na figura seguinte, os dispositivos que formam o inversor, tem de possuir capacidade para suportar tensões inversas. Para maior clareza optou-se por fazer a frequência das portadoras igual a 21 vezes a frequência de referência (m=3 na eq.4.4). 97 Conversão de corrente contínua em alternada Figura 4.45 - Forma de onda da tensão aos terminais dos interruptores do inversor. 1.7 Características do PWM implementado A implementação do PWM no µC requer que se imponham algumas limitações ao tempo de duração de cada estado de PWM: • A duração tem de ser um número inteiro da resolução do contador: t = n*400ns. • A duração de um estado não pode ser inferior a um determinado tempo imposto pela rotina que muda o estado e pela velocidade de comutação dos IGBTs (10µs). A limitação dos tempos dos estados a um número inteiro da resolução do contador usado para a contagem do tempo, leva a uma não linearidade de VDC em função do im. Esta não linearidade aumenta à medida que a resolução dos im aumenta (maior número de índices de 98 Conversão de corrente contínua em alternada modulação). Alias, esta é a razão pela qual não se aumenta o número de im (não faz sentido utilizar um grande número de im se depois a tensão obtida para o im(i) é igual a tensão para o im(i-1) e im(i+1)). A introdução de tempos mínimos de condução e de corte provoca um comportamento diferente nas características do PWM. Como é óbvio estas diferentes só existem nos índices de modulação que são afectados por essa limitação inferior nos tempos. As diferenças mais significativas provocadas pela limitação temporal inferior são a introdução de componentes harmónicas que eram desprezáveis no caso do PWM ideal e o agravamento da não linearidade de VDC em função do im. Figura 4.46 - Evolução dos harmónicos de corrente em função do índice de modulação. 99 Conversão de corrente contínua em alternada har: 23..49 har: 53..67 har: 71..97 Figura 4.47 - Evolução dos harmónicos relativos de corrente em função do índice de modulação. 2 Trânsito de energia activa e reactiva Tal como o conteúdo harmónico injectado na rede, o consumo de energia reactiva é um facto que deve ser evitado a tudo custo. O seu trânsito na rede acarreta maiores perdas de energia, sobredimensionamento dos dispositivos devido à corrente ser mais elevada para a mesma potência activa, flutuações na tensão da rede, etc. Em certas condições, o inversor de corrente pode compensar o consumo de energia reactiva de um sistema, através da produção de uma quantidade de energia reactiva igual à consumida pelo sistema. 100 Conversão de corrente contínua em alternada Desta forma, nos sistemas onde é necessário um inversor de corrente, evita-se o uso das tradicionais baterias de condensadores para compensar o factor de potência,. Deve ser notado, que mesmo que o inversor de corrente não seja requerido pelo sistema, é uma opção a ter em consideração quando se pretende um compensador dinâmico do factor de potência. Isto é particularmente interessante quando o consumo de reactiva varia fortemente ao longo do tempo. A possibilidade do inversor produzir energia activa e reactiva de forma independente, depende da fonte de corrente que o alimenta. Se a corrente que alimenta o inversor for independente do seu funcionamento (Ex: Se a fonte de corrente for ideal, ou num caso mais realista, se for uma fonte de tensão variável em série com uma bobina) as energias activa e reactiva são independentes. Se o inversor tiver de controlar a sua corrente de entrada, a quantidade de energia reactiva que é possível produzir, passa a estar dependente da energia activa. Nas Secções 1.6.1 e 1.6.2 concluiu-se que: 1 .I DC .im 2 (4.29) .VC .im.cos(θ) (4.30) I REDE = VDC = 3 2 onde: I REDE é o valor eficaz da corrente injectada na rede, VC o valor eficaz da tensão composta da rede, I DC o valor da corrente à entrada do inversor, VDC o valor tensão gerada pelo inversor à entrada, im o índice de modulação e θ o esfasamento entre a corrente e a corrente e a tensão da rede. A potência activa entregue à rede é dada por: P = VDC .I DC = 3.I REDE . VC .im.cos(θ) = 3 2 (4.31) .I DC .VC .im.cos(θ) e a reactiva: Q = 3 2 .I DC .VC .im.sen(θ) = P.tan(θ) (4.32) 101 Conversão de corrente contínua em alternada A potência aparente (S) depende apenas da corrente I DC (a tensão da rede é fixa) e do índice de modulação: S= 3 2 .I DC .VC .im (4.33) 2.1 Corrente IDC independente do inversor Se o inversor for alimentado por uma fonte que imponha a corrente no barramento DC (IDC) independentemente da tensão gerada pelo inversor (VDC), o inversor consegue entregar uma potência reactiva independentemente da potência activa. IREDE I dc V DC P Inversor de corrente L IDC VC Vf DC V DC P,Q IREDE Inversor de corrente VC P,Q P Figura 4.48 - Alimentação do inversor com uma corrente independente. A determinação dos parâmetros de comando do inversor é muito simples: A partir da relação entre as potências activa (P) e reactiva (Q) determina-se o esfasamento: Q θ = arct P e a partir de P ou Q (um que não seja zero) determina-se o índice de modulação: im = Q 3 2 .I DC .VC .sen(θ) = P 3 2 .I DC .VC .cos(θ) . Este conjunto é uma opção para realizar a compensação do factor de potência de forma dinâmica. Se a potência activa for zero, a potência reactiva consumida ou gerada (consoante θ = 90º ou θ = 270º ) é dada por: Q= 3 2 .I DC .VC .im (4.34) A máxima potência reactiva que é possível gerar ou consumir é unicamente dependente da corrente IDC imposta pela fonte de corrente. Para manter a corrente IDC constante a fonte de corrente tem de compensar a tensão gerada pelo inversor: VDC = 3 2 .VC .im.cos(θ) e como é óbvio, tem de fornecer a potência activa entregue pelo inversor à rede. 102 (4.35) Conversão de corrente contínua em alternada 2.2 Corrente IDC controlada pelo inversor Se a fonte de corrente que alimenta o inversor for constituída por uma fonte de tensão não controlada em série com uma bobina, a corrente IDC tem de ser controlada através da tensão gerada pelo inversor à sua entrada (VDC). IDC L Vf DC V DC IREDE VC Inversor de corrente P,Q P Figura 4.49 - Alimentação do inversor por uma fonte de tensão não controlada. Como a tensão VDC tem de controlar a corrente IDC, os parâmetros de comando do inversor ficam presos pela relação: VDC im.cos(θ) = 3 2 .VC (4.36) pelo que a potência activa fica definida: P= 3 2 .I DC . VC .[im.cos(θ)] (4.37) Alias, isto é óbvio, porque se a fonte VfDC fornecer a corrente IDC, a potência activa envolvida no sistema fica automaticamente definida: P = Vf DC .I DC (4.38) Desta forma a potência reactiva fica limitada entre o valor zero e um valor máximo (QMAX) que se determina a seguir. A potência reactiva é maximizada quando o valor: im.sen(θ) for o maior possível e o valor: im.cos(θ) o menor possível de modo a maximizar sen(θ) . Isto significa que para maximizar a energia reactiva, o índice de modulação deve ser o mais alto possível (1), e o esfasamento o mais próximo possível de 90º ou 270º. Da relação (4.36) e fazendo im=1 tira-se que: cos(θ) = VDC 3 2 .VC (4.39) 103 Conversão de corrente contínua em alternada pelo que o valor de [ im.sen(θ) ]vale: 2 VDC im.sen(θ) = ± 1 − 3 VC 2 (4.40) Desta forma o valor máximo de energia reactiva produzida ou consumida vale: Q MAX = 3 2 2 VDC . I DC . VC . 1 − 3 VC 2 (4.41) 2 Q MAX 3 VC −1 = P. 2 VDC (4.42) de onde se conclui que a potência reactiva máxima que o inversor consegue fornecer ou absorver, cresce com a potência activa e com a relação VC/VDC. 2.3 Aplicação no SRED A possibilidade do inversor de corrente poder fornecer energia reactiva à rede, leva-nos a pensar que o SRED poderá funcionar com um factor de potência unitário, sem o recurso aos condensadores de compensação. Isto não é possível, porque quando a máquina está a rodar a velocidades perto da velocidade de sincronismo, a potência disponível no rótor e transmitida ao inversor é baixa. Desta forma, quando a máquina rodar a velocidades perto da de sincronismo, a potência reactiva que o inversor pode fornecer à rede, está limitada pela potência activa fornecida pelo rótor ao inversor, segundo a equação (4.42). Apesar da potência activa disponível no rótor da máquina ser baixa a essas velocidades, o consumo de energia reactiva pelo estátor é elevada, devido às correntes de magnetização. Desta forma, a energia reactiva consumida pela máquina para a sua magnetização, tem de ser compensada por uma bateria de condensadores. Como se pode observar nos gráficos da Figura 4.50, o consumo de potência reactiva, aumenta com a velocidade de rotação na situação em funcionamento como gerador (ω>ωs), e com o aumento da corrente no barramento DC (com a subida da potência activa disponível no rótor). Este aumento é originado pelas reactâncias de fugas do estátor e do rótor. 104 Conversão de corrente contínua em alternada Figura 4.50 - Consumo de potência reactiva em função da corrente no barramento DC e em função da velocidade para vários valores de VDC. Desta forma, o inversor deve fazer a compensação dinâmica do excesso de reactiva que surge com o aumento da corrente no barramento DC. No entanto, no SRED usado neste trabalho, o inversor não consegue realizar essa compensação dinâmica porque a altas velocidades a tensão gerada pelo rótor leva a que a relação VC/VDC diminua. Isto limita a potência reactiva que o inversor pode fornecer, como se verifica na equação (4.42). Isto acontece, porque o inversor para gerar uma tensão VDC semelhante à tensão que os rectificadores do rótor originam, tem de manter o esfasamento nulo e o índice de modulação unitário. Existem várias soluções, de forma a que o inversor possa efectuar a compensação dinâmica da energia reactiva variável consumida nas reactâncias de fugas do estátor e do rótor: • aumento da tensão da rede do lado do inversor; • diminuição da tensão da rede no estátor da máquina; • uso de uma máquina com uma relação do número de espiras estátor/rótor que baixe a tensão no rótor. Obviamente, qualquer uma destas soluções dá origem a que a relação VC/VDC aumente, aumentando assim a máxima potência reactiva que o inversor pode fornecer para a mesma potência activa. Como no caso em questão, a compensação dinâmica do factor de potência não pode ser feito em toda a gama de funcionamento, optou-se por não a fazer de todo. Desta forma, o inversor vai funcionar com esfasamento sempre nulo, sendo controlado apenas com o índice de modulação. 105 Conversão de corrente contínua em alternada 3 Descrição da montagem utilizada Como interruptores do inversor foram utilizados semicondutores IGBT (Insulated Gate Bipolar Transistor). Atendendo a que o projecto se trata de um protótipo os IGBTs foram sobredimensionados, usando-se dispositivos de 1200V e 1000A. Como a tensão aos terminais de cada interruptor atinge valores negativos, o dispositivo que implementa o interruptor tem de possuir capacidade para bloquear a tensão inversa. Atendendo a que os IGBTs não tem esta capacidade é necessário colocar um díodo em serie com cada IGBT de forma a que este bloqueie a tensão e não a deixe aparecer aos terminais do IGBT. Os díodos em anti-paralelo com os IGBTs são incorporados nas caixas dos IGBTs disponíveis comercialmente. Isto acontece porque normalmente estes dispositivos são utilizados em inversores de tensão e estes necessitam dos díodos em anti-paralelo para o seu funcionamento. Naturalmente estes díodos não são necessários para o inversor de corrente nem tem qualquer efeito no seu funcionamento. 15V comando on/off reset erro +15V - 8V Figura 4.51 - Dispositivos que implementam um interruptor: IGBT, díodo, supressor e driver isolado. Os supressores de tensão colocados em paralelo com cada IGBT servem para proteger estes contra as sobretensões geradas durante as comutações de corrente. Estas sobretensões surgem devido às elevadas derivadas de corrente que atravessam as indutâncias parasitas existentes nos cabos e barras de ligação entre os vários componentes do inversor. O supressor de tensão usado (DSAS 8U da ABB) não deixa que a tensão aos seus terminais suba acima de 800V. Se a tensão tiver tendência para continuar a subir, a corrente que atravessa o supressor cresce desmesuradamente até que o supressor queima por excesso de temperatura, ficando em curto-circuito. Esta é alias, uma grande vantagem do DSAS face as tradicionais VDR que ficam em circuito aberto depois de queimarem. Desta maneira o DSAS continua a proteger o IGBT mesmo depois de queimar (é claro que nestas condições o inversor deixa de funcionar correctamente uma vez que interruptor protegido fica sempre fechado). Como curiosidade relata-se um acontecimento ocorrido durante um ensaio do inversor: Quando um dos supressores entrou em condução, a corrente que o atravessou foi de tal ordem que o cabo de aproximadamente 5mm de diâmetro que o ligava ao IGBT derreteu. Depois de 106 Conversão de corrente contínua em alternada retirado, constatou-se que mesmo assim o supressor estava em curto-circuito, não tendo sido aberto apesar da grande corrente que o atravessou. Cada IGBT é comandado por um driver que fornece isolamento entre o IGBT e a placa de controlo. Os 6 drivers são alimentados por uma fonte de 15V independente, uma vez que o seu consumo é considerável. Os drivers têm uma característica que lhes permite monitorar a tensão Colector - Emissor (VCE) dos IGBTs e retirá-los de condução se essa tensão estiver acima de um certo limite enquanto o IGBT estiver a conduzir. Isto permite evitar que o IGBT queime por excesso de dissipação numa situação de defeito ou excesso de corrente. É claro que durante a entrada em condução, a tensão VCE demora algum tempo a descer, pelo que o driver só verifica o VCE a partir de um certo tempo a contar da entrada em condução. Quer este tempo quer o limite de tensão a partir do qual o driver retira o IGBT de condução são configuráveis através de resistências e condensadores na placa do driver. Os IGBTs também são retirados de condução se a alimentação do driver ficar demasiado baixa ou instável. Isto garante que o sinal de gate que o driver fornece ao IGBT está sempre nos níveis correctos de tensão. O sinal de erro é activado sempre que o driver retira o IGBT de serviço por excesso de VCE ou devido à alimentação do driver, de forma a avisar o controlador do facto. A saída deste sinal é activa em baixo em “open colector” pelo que os sinais dos 6 drivers são ligados num único ponto realizando-se assim um “wired OR”. O sinal de reset do driver deve ser activado sempre que o driver arranca ou a seguir a uma ocorrência de erro, de forma a ser possível colocar o IGBT a conduzir por ordem do sinal de comando on/off. Os sinais de comando do µC passam por um buffer que os inverte e lhes fornece potência suficiente para conduzirem o driver. Naturalmente estes buffers estão localizados na placa de controlo. g PRT R PRT E PRT Detecção sobretensão ID C g 1H g 2H g 2H R 1H R 2H R 2H E 1H E 2H E 2H IR IS E VDC IT yC g1H g 1H E 1H g2H g 2H E 2H g3H g 3H E 3H g1L g 1L E 1L g2L g 2L E 2L g3L g 3L E 3L reset_inversor R 1H R2H R3H R 1L R 2L R 3L erro_inversor set OR reset reset_protecção R PRT OR reset_protecção actua_protecção sobretensão g 1L g 2L g 2L erro_inversor R 1L R 2L R 2L erro_protecção E 1L E 2L E 2L g PRT reset E VDC E PRT set sobretensão actua_protecção Figura 4.52 - Esquema do inversor, protecção e envolvente de comando. Para proteger o inversor de sobretensões é colocado um IGBT auxiliar e um díodo para curto-circuitar o barramento DC em caso de sobretensão. A resistência em serie serve para limitar a corrente no caso de actuação da protecção, o díodo para proteger o IGBT contra as tensões negativas que podem surgir no barramento e o supressor serve para “aguentar” a tensão enquanto o IGBT de protecção não entra em condução. 107 Conversão de corrente contínua em alternada O driver do IGBT de protecção é alimentado por uma fonte independente da fonte que alimenta os outros 6 drivers. Isto serve para garantir que no caso da fonte dos 6 IGBTs for abaixo, existe energia para ligar o IGBT de protecção. No caso da fonte do driver do IGBT de protecção for abaixo, um sinal avisa o µC deste facto e o sistema deve ser parado. Obviamente a sequência de operações de paragem neste caso não deve fazer uso do IGBT de protecção. Para accionar a protecção é colocado um dispositivo que detecta sobretensões no barramento. É composto por um comparador que activa o sinal de erro EVDC no caso da tensão subir acima de um certo nível. Para evitar os atrasos inerentes às interrupções do µC, e atendendo a que em caso de sobretensão não se pode perder tempo para não destruir o inversor, o sistema de comando utiliza este sinal para ligar o IGBT de protecção directamente por hardware. Uma das causas que leva a existir sobretensão é a retirada de condução intempestiva de um IGBT pelo respectivo driver. Neste caso em vez de se esperar pela sobretensão que certamente irá surgir (se é que ainda não começou a surgir) o IGBT de protecção também é actuado directamente por hardware assim que um dos drivers retirar o respectivo IGBT de condução. Naturalmente estes dois sinais também são ligados ao µC para se tomarem as medidas necessárias à paragem do sistema. O sinal de erro do driver do IGBT de protecção também está disponível mas não tem grande utilidade para protecção uma vez que este sinal só surge se o driver retirar o IGBT de protecção de condução, e isto só acontece se o IGBT já estiver a proteger o inversor. Como é obvio, nesta situação o inversor provavelmente ficara destruído. Assim, o sinal serve apenas para determinar se a causa de destruição foi a saída de condução intempestiva do IGBT de protecção. O sinal de sobretensão é enviado pelo circuito de detecção para a carta de controlo através de fibra óptica. Os IGBTs e respectivos díodos estão montados em 3 dissipadores com ventilação forçada. Os supressores também estão montados individualmente sobre dissipadores. A velocidade de entrada e saída de condução dos IGBTs é controlada através de resistências colocadas na placa do driver e que ligam o andar de saída do driver à gate do IGBT. 4 Conclusões As regras para um correcto funcionamento do inversor de corrente impossibilitam a adaptação do uso de módulos disponíveis comercialmente para o comando de inversores de tensão. O controlo da conversão de corrente contínua em alternada foi desenvolvido com base no método de PWM. A adopção deste método baseia-se na necessidade de reduzir o conteúdo harmónico para as frequências próximas dos 50Hz da rede, tendo em vista melhorar a sua qualidade bem como controlar a tensão no barramento DC de alimentação do conversor DC/AC. A importância desta funcionalidade será mostrada no capítulo 7 desta dissertação. 108 Conversão de corrente contínua em alternada Tal como os restantes µC que possuem módulos de PWM para inversores, o módulo de PWM do C167 é dedicado ao comando de inversores de tensão, não sendo possível adaptá-lo ao comando do inversor de corrente. Como não é possível obter fórmulas explícitas e de rápida execução, o C167 comanda o inversor de corrente através de valores tabelados. O módulo desenvolvido para o comando além de regular a amplitude das correntes de saída, também permite o controlo da fase entre as correntes e as tensões da rede. 109