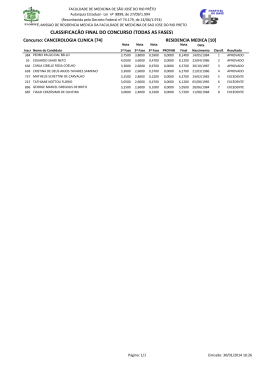

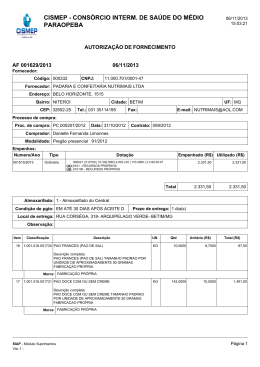

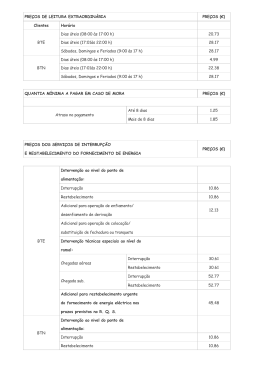

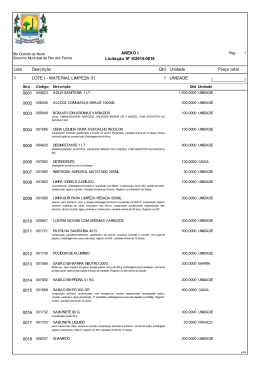

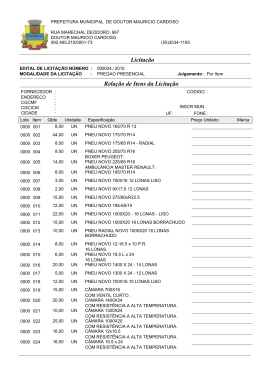

SIMULAÇÃO DE UM COMPUTADOR COM INTERRUPÇÃO Fellipe Venceslau Isensee AGENDA INTRODUÇÃO TEÓRICA APRESENTAÇÃO DO PROJETO UM COMPUTADOR SIMPLIFICADO Códigos de operação Código Operação 00 01 10 11 Parar Somar ao Acumulador Subtrair do Acumulador Copiar do Acumulador Ir para: Cpu do Projeto CONTROLADOR Ir para: Controlador do Projeto INTERRUPÇÃO O controlador para o que está fazendo para atender o dispositivo que pediu a interrupção. Assim que termina esse atendimento, retorna a rotina anterior. UNIDADE DE CONTROLE (COM CAPACIDADE DE ATENDER A INTERRUPÇÃO) AGENDA INTRODUÇÃO TEÓRICA APRESENTAÇÃO DO PROJETO CPU Ir para: Cpu Teórica CONTROLADOR Ir para: Controlador Teórico LINGUAGEM DE MÁQUINA PARA O COMPUTADOR SIMPLIFICADO Local da Memória Op-code (binário) Endereço (binário) HexaDecimal Op-Code Endereço 0 10 111011 BB 02 59(3Bh) 1 01 111100 7C 01 60(3Ch) 2 10 111101 BD 02 61(3Dh) 3 01 111110 7E 01 62(3Eh) 4 01 111111 7F 01 63(3Fh) 5 11 100111 E7 03 (27h) 6 00 111111 3F 00 64(3Ch) 59 0000 09 60 0000 10 61 0000 01 62 0000 20 63 0000 10 -9h +10h -01h +20h +10h Gravar na memória Parar Ir para: Forma de onda CONFIGURAÇÃO DA MEMÓRIA @memory main.mem.m @0 BB 7C BD 7E 7F E7 3F @3b 09 10 01 20 10 SIMULAÇÃO COMPORTAMENTO NORMAL SIMULAÇÃO COMPORTAMENTO COM INTERRUPÇÃO SIMULAÇÃO COMPORTAMENTO COM INTERRUPÇÃO CONFIGURAÇÃO DA MEMÓRIA NO FIM DA EXECUÇÃO @memory main.mem.m @0 BB 7C BD 7E 7F E7 3F @27 36 @3b 09 10 01 20 10 Obrigado! Executado por: Fellipe Venceslau Isensee [email protected]

Download