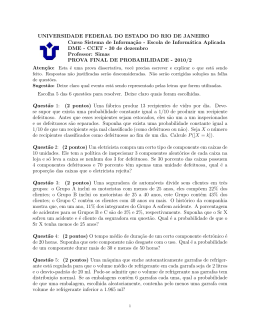

Bacharelado em Ciência da Computação – DINF / UFPR – Prof. Luis Allan Künzle CI 210 – Projetos Digitais e Microprocessadores – 2o Semestre de 2013 – Prova Final – 19/12/2013 Prova sem consulta – Horário de inı́cio: 13:30h – Horário de término: 15:10h Aluno: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1. Projete uma ULA com as seguintes caracterı́sticas: • Entradas da ULA: duas entradas de dados (Y e Z) e uma entrada S de seleção de 3 bits (S2 , S1 e S0 ). • Saı́das da ULA: um resultado G (G2 , G1 e G0 ) e um bit único de carry out C. A tabela a seguir mostra as funções que você deve implementar para este problema. Note que + e − nesta tabela significam operações aritméticas em complemento de dois; as operações lógicas são realizadas bit-a-bit. (a) Preencha a tabela mostrando como devem ser atribuı́das as entradas do somador para cada operação aritmética (para don’t cares use X). (b) Derive as expressões mı́nimas em soma de produtos para Ai , Bi e Cin . (c) Desenhe a Unidade Aritmética usando portas OR (use produtos, p.ex. Y S2 S1 , como entradas). (d) Desenhe a Unidade Lógica usando portas lógicas e um mux 4x1. (e) Desenhe a ULA como um bloco com entradas de ENABLE, dados lógicos (conectados à Unidade Lógica), dados aritméticos (conectados à Unidade Aritmética), seletor e com saı́da de resultado, usando um mux 2x1. S2 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Operação Y NOT(Y ) Y +Z Y NOR Z −Y (compl. de 2) Y NAND Z Y − Z (compl. de 2) Y XOR Z A B Cin 2. O circuito lógico seqüencial da Figura 2 realiza uma operação especı́fica. No circuito, as caixas rotuladas por C e A são registradores de 4 e 8 bits, respectivamente. O valor desses registradores é inicialmente zero. O bit único de saı́da da caixa rotulada “neg” é 1 se e somente se a entrada de 8-bits é um número negativa quando interpretado como um inteiro em complemento de dois. O circuito também contém uma memória de 24 palavras de 8-bits, um incrementador de 4-bits, um somador de 8-bits (com um bit de carry in sempre em 1), um inversor de 8-bits e um multiplexador 2-1 de 8-bits. Em apenas uma frase, que operação este circuito realiza? Ou seja, qual é a relação entre o valor no registrador A após 16 ciclos com os valores armazenados na memória? Você pode montar uma tabela-rascunho para monitorar as operações do circuito. 4 C Memória 4 Clock 1 8 24 por 8 bits + 8 8 +1 8 1 8 A neg 8 8 Figura 1: Circuito lógico seqüencial da Questão 2 2 0 1 8 3. Considere a instrução SWAP e o datapath multiciclo, apresentados, respectivamente, nas Figuras 2 e 3. Complete a tabela abaixo com os sinais necessários, para cada micro-instrução, de forma que a instrução SWAP seja corretamente executada. Sua execução consiste em trocar o conteúdo dos registradores RegBase e RegFonte. Lembre-se que em um datapath multiciclo cada µ-instrução corresponde a um ciclo de relógio e a respectiva transferência de valores aos registradores. OBS: Não é necessário modificar o datapath. 1 2 3 4 5 6 3 LdIR SelExt tsADD tsPC LdPC SelPC SelBasePC tsMDR LdMDR SelMDR R/W EnMem LdMAR LdDPY tsKBD LdSR tsALU ALUCtrl Ações em Register Transfer Language LdReg SelRegBusA SelRegDst µ-instrução µ-instrução 1 2 3 4 5 6 ALUCtrl 00 01 10 11 Operation A+B A−B A B Tabela 1: Sinais de controle da ULA da Questão 3 SWAP 1111 RegFonte RegBase 000000 Figura 2: Instrução SWAP da Questão 3 SelRegDst LdReg RegA 1 0 RegDst 1 3 RegDst 3 RegBusA ValBusA DataOut BusA RegB ValBusB 0 16 tsKBD SelBasePC 0 DPY DataIn LdDPY Load 1 DataIn 1 ValALU 16 Load LdSR N P [5] ValImm5 16 SIGNAL EXT. 5 [4..0] 16 ValImmExt 0 0 En 0 DataIn SelPC 2 ValDataOut 1 SIGNAL EXT. 2 3 SIGNAL EXT. Load [5..0] 2 RegDst SelExt LdPC [8..0] 6 16 2 ValNextPC +1 MDRMUX 1 PCMUX [10..0] 9 16 ValBus ValPC+1 R/W DataOut SIGNAL EXT. 1 ValBase+Imm MEMORIA 11 16 Address 0 Z SelB + SelMDR ValP B ValMAR R/W ValZ ValBasePC DataOut EnMem ValN ValB LdMAR Load MAR BASEPCMUX KBD 16 A LOGIC DataOut RegBusB BusB FILE REGISTER 3 16 16 tsALU 2 DataIn LoadReg SelRegBusA RegA ALUCtrl ALU 0 ALUBMUX RegDst ValBus 16 [11..9] RegA PC [8..6] RegB [2..0] Instruction ValPC tsMDR LdMDR DataIn Load DataOut MDR tsPC LdIR tsAdd ValMDR ValBus Figura 3: Datapath da Questão 3 4 Load IR

Baixar