1 Visão e desafios da Indústria de Semicondutores para teste de Circuitos Integrados Hildebrando de Oliveira Instituto de Tecnologia José Rocha Sergio Cardoso São Paulo, 13 de maio de 2010 Abstract Some issues about semiconductor and testing trends are discussed, as well as historical and financial constraints regarding the test process in their multiple scopes, from the bare wafer cell to the finished assembled component, and its relation to the process of fabrication of very large scale integrated semiconductor circuits. © 2010 Instituto JC. All rights reserved. Keywords: Testes de semicondutores, wafer, projeto para testes DFT, encapsulamento, die, nanotecnologia. [email protected] 1. A importância dos testes em CIs Os testes nos Circuitos integrados são importantes para garantir o seu funcionamento básico, pois um circuito integrado com funcionalidades complexas exige um instrumental extremamente robusto e intrincado para assegurar que o circuito integrado sob teste atinja um grau mínimo de desempenho e funcionalidades aceitáveis. Como em qualquer outro processo produtivo, os testes em circuitos integrados permitem a detecção de problemas de produção e projeto, bem como um fator de ponderação para cálculos de viabilidade e custo do processo fabril em si. Via de regra, os testes são um dos processos mais custosos durante a fabricação dos circuitos integrados [1], e muitas vezes os chips (que possuem tamanho muito pequeno para operacionalizar o processo de teste) são projetados de forma a permitirem que pequenas pontas de prova sejam monitoradas em um ambiente conveniente. Conforme as geometrias dos projetos diminuem em tamanho, novas estratégias iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil precisam ser desenvolvidas, principalmente porque os chips possuem uma escalabilidade muito grande, e a demora na detecção de falhas em quaisquer uns dos processos pode levar a uma verdadeira tragédia financeira para uma empresa que projete ou fabrique tais dispositivos. 2. O papel dos testes em CIs no fluxo de fabricação Os testes nos circuitos integrados possuem uma importância muito alta pois permitem ao fabricante prevenir grandes prejuízos ao longo do processo, e, eventualmente que estes componentes defeituosos cheguem ao mercado. Um aspecto importante é o fato de que dependendo da taxa de rejeição do wafer o processo pode ser interrompido, pois não é mais viável financeiramente a continuidade no processo da peça que apresentou um determinado nível de falha. Conforme [4], a detecção do problema antes do encapsulamento pode significar um ganho de 1 a 5% em erros devido à não compliância com o teste, após o encapsulamento, sendo que até 12% pode 2 ser retido, contando-se que já não existam erros crassos de projeto. Os testes, em ASICs (Application-Specific Integration Circuit) de sinal misto (mixed signal) com tecnologia até 250nm podem representar 33% do tempo e até 37% em homens-hora por peça, se considerado o processo até antes de se efetuar a embalagem dos produtos, logo após o encapsulamento. Quando os circuitos desceram às escalas nanométricas, até o próprio ambiente onde estes são fabricados e testados representam um desafio operacional que só foi totalmente solucionado com a aplicação massiva de dispositivos de posicionamento computadorizado, ou, como são meramente chamados, os robôs. A automação e a robótica deram um grande impulso neste desenvolvimento pois permitiram à fábrica aperfeiçoar os processos nos quais a repetibilidade pode ser mensurada de maneira confiável, praticamente não dependendo do fator humano na fase de execução da montagem, manuseio e teste dos dispositivos. 2. Test on Chip (wafer probe) Quando se trata de testes, sejam em protótipos ou em produtos finais, de microcircuitos integrados, a grande miniaturização dos circuitos permite somente que dispositivos de micrométrica (ou nanométrica) precisão tenham acesso ao “universo” na qual o circuito ou sistema irá operar. As interfaces de ToC (test on chip) são dispositivos de altíssima tecnologia, que podem acessar pontos específicos do circuito e efetuar uma determinada quantidade de testes e simulações, para assegurar a confiabilidade do circuito integrado sendo produzido ou projetado. Na Figura 2.1 abaixo se pode verificar o aspecto de uma destas pontas, testando um determinado circuito integrado, e sendo iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil posicionada por um comando computadorizado ortogonal conveniente. (CNC – comando numérico computadorizado). Figura 2.1 Wafer (www.intellitech.com) probe em ação. O teste no nível do wafer é uma ferramenta poderosa para detectar problemas de projeto [2] e problemas de processo, porém pouco eficiente se for considerada a perda no processo de corte do wafer, que pode representar uma falha na eficiência do processo1 e modificar por definitivo o seu quadro de efetividade. O custo envolvido neste processo acaba sendo então dissolvido na própria economia futura que se podem obter, principalmente quando o processo em questão ainda apresenta algum nível considerável de perda no processo de corte ou encapsulamento. 3. Dificuldades atuais Apesar de ser muito eficiente, a prova do circuito no nível do wafer pode representar, em alguns casos um desafio tecnológico, quanto menor a tecnologia dispositivo ou maior sua velocidade pior pode ser considerado este quadro [3]. 1 isto quer dizer que uma peça já testada e presumidamente boa será segregada se posteriormente durante o processo de corte ela for danificada. 3 Novamente pode ser considerado o dispêndio de tempo no teste um dos fatores decisivos para saber se determinado teste é viável ou não, pois o custo do equipamento não tem total relação com o tipo do teste, e sim a tecnologia do circuito integrado a ser testada, e a velocidade necessária para se atingir a meta produtiva. Uma das alternativas [4] para otimizar este processo consiste em desenvolver os circuitos de forma a apresentarem certas peculiaridades que permitam o acesso a pontos específicos do circuito que, através da pontas de prova seja possível observar uma determinada característica que é importante na performance do circuito integrado. Assim criaram-se métodos para contornar estes obstáculos operacionais. Salas com temperatura extremamente baixa, bombardeamento com íons para eliminação de impurezas e também pontos de testes nos circuito, pois a demanda por alta densidade de espaço acarretou um acréscimo do produto da potência por área que o circuito ocupa, em alguns casos (como chips que operam com radiofreqüência), o teste é limitado pela própria interferência que a ponta de prova oferece ao comportamento natural do circuito “aberto” quando em comparação com o seu comportamento real operação após o encapsulamento. Este oferece um ambiente mais seguro para que o circuito integrado seja testado sem o risco de contaminação por impurezas ou mesmo sobreaquecimento [4]. Mas ainda assim a perda por um teste ineficiente pode significar um desgaste muito grande por parte dos profissionais envolvidos, e significar a inviabilidade de um projeto, se não executado dentro de critério viabilizando um futuro teste. 4. Técnicas existentes (vantagens e problemas) Um dos métodos aplicados para contornar os problemas no teste é conhecido iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil como DFT, ou design for testing, em que, durante a fase de projeto, estudam-se arquiteturas que permitam que na realidade a função do circuito não seja testada da forma real como ela opera (em sua função como produto acabado), e sim em uma condição possível de ser realizada em fábrica (com o produto em seu estágio intermediário) que cujo resultado positivo deste teste signifique que o circuito sob teste atingiu um determinado parâmetro esperado. As cadeias de varredura (scan-chains ) [1] podem ser utilizadas quando se deseja realizar diversos testes em demanda muito grande. Elas consistem em permitir um acesso a determinados pontos que podem ser varridos pelo sistema de teste, mesmo considerando um método do tipo GO/no-go e após a varredura de determinados parâmetros (resposta a impulso, multiplexação de um dado, cruzamento de borda, etc.) um resultado mensurável foi obtido. Outra técnica muito utilizada em memórias [2] é a BISR (Built-In-SelfRepair), muito aplicada em elementos de memórias quando os seus blocos apresentam um certo padrão de repetitividade de blocos funcionais. A simplicidade deste método consiste em se criar blocos “reserva” dentro do circuito que, no caso de uma falha pontual, podem ser substituídos por outros, existentes. Muitas vezes esta substituição é feita por meio de software, durante a operação do circuito (após encapsulamento) Alguns padrões como o IEEE1149.9 surgiram na tentativa de criar uma norma para ser seguida tanto pelos fabricantes de dispositivos semicondutores integrados, como para os provedores de soluções de teste embarcada, de forma que o DFT seja feito de maneira homogênea e viabilize a produção e o projeto (mesmo em escala reduzida ou restrita) de sistemas de teste utilizando pontas de prova padronizadas, de acordo com a tecnologia em pauta. 4 Os testes estruturais (que visam as microestruturas funcionais) tendem [2] a ser formados por pequenos segmentos de paletas de silício, obtidos sob o mesmo processo para evitar incompatibilidades de aplicação. Mas a tendência realmente é a aplicação não estruturada [3] do teste, devido algumas vezes por falta de largura de banda, dissipação térmica ou ambas. Em alguns sistemas um arrefecimento forçado com argônio ou outro gás inerte é usado para manter o ambiente e o corpo de prova (wafer ou segmento) dentro de condições aceitáveis de operação. Fig. 5.1 esquema de testes em wafer com cartão de prova (ou matriz de prova) www.jemnet.co.jp 5. Tecnologias, ferramentas e softwares utilizados. As Gigas de teste utilizadas, tanto para produção em massa quanto para testes em protótipos, diferem nos seguintes aspectos [5]: • • Para wafers-protótipo, são usados equipamentos como na figura 2.1, em que de dois até 6 nós do circuito são testados. Normalmente são testes estáticos para verificar consumo de corrente, polarizações, e outras pequenas funções, quase sempre sem a aplicação de impulsos de curta duração ou medição de resposta. Para produção em massa são usados equipamentos como os das figuras 5.1 e 5.2 abaixo, onde em uma “cavidade” são colocados (com alinhamento a laser ou micro óptico) o wafer e o “cartão de prova”, fabricado com nanotecnologia, e que pode acessar alguns milhares de pontos no circuito integrado mediante um perfeito alinhamento com o wafer em teste, sendo que o cartão de prova é casado com o wafer. Este processo testa todos os chips existentes no wafer. Obviamente em casos extremos ou chips de alta performance (aplicações militares, médicas, aeroespaciais), podem existir vários cartões de prova, executando uma infinidade de outros testes. iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil Figura 5.2 Aparência real de um equipamento de teste de wafer. www.solidustech.com Após o encapsulamento, os testes dos chips passam a ter uma maior elasticidade, tanto em questão da potência que pode ser aplicada quanto da robustez mecânica do sistema pois agora os terminais dos chips estão já disponíveis e a dissipação de potência já pode ser efetuada como deveria (em tese) ser feita na aplicação final. Os testes agora visam mais a performance que obter uma estimativa da confiabilidade do processo, mesmo porque depende dos testes de performance a publicação ou determinação final da classe de operação de um determinado semicondutor. Na figura 5.3 se observa um destes equipamentos para efetuar estes testes, em massa, de fabricação alemã. E na figura 5.4, um soquete para testes em encapsulamento QFP-64, de fabricação japonesa. 5 Fig. 5.3 Linha de testes da empresa Arrow na Inglaterra. www.arrow.co.uk 6. Performance, custos, estatísticas Na prática, o que difere, ao menos em princípio, um wafer de um chip simples como o LM1458 (amplificador operacional de aplicação geral) do LM1558 (aplicação militar), são os testes executados em ambos,sendo que o último custa 20 vezes mais que o primeiro (www.nsc.com). O wafer e o processo produtivo dos dois, até o momento do teste, é o mesmo.O importante na realidade é otimizar o processo produtivo de forma a minimizar as perdas, pois as simulações realizadas durante o projeto, são tão exaustivas Fig. 5.5 Sistema de testes de protótipos de circuitos integrados encapsulados. INFNBolonha, Itália. www.bo.infn.it que dificilmente após a execução de um projeto bem feito é necessária uma nova prototipagem, isso se deve principalmente ao fato que o IEEE normalizou alguns dos modelos de testes, o que propiciou a comunidade desenvolvedora trabalhar em conjunto. De certa forma, isso foi um dos principais fatores que propiciaram ao mercado semicondutor este crescimento exponencial, que somente agora, após quase 40 anos da produção em massa do primeiro circuito integrado semicondutor, ela demonstra uma tendência de crescimento mais linear, que exponencial [3]1 Algumas pesquisas [5] indicam que a tendência da redução de custo nos testes implica mais na concepção do semicondutor e do processo em suas características microscópicas ou moleculares, do que em seus aspectos macroscópicos ou funcionais. Assim é possível incluir em um mesmo wafer muitos dispositivos e obter ainda assim uma relação custo-benefício maior que o approach anterior, e assim sucessivamente. Não deve deixar de se considerar que o teste apresente por si só uma imensa área de pesquisa [6] que apesar de não ser a coqueluche tecnológica representada pela área de projetos em microeletrônica. 1 Fig. 5.4 – soquete para testes de baixa escala e prototipagem em circuito integrado. www.yamaichi.co.jp iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil Nesta consideração, leva-se em conta os casos de semicondutores “monolíticos”, o que exclui os sistemas de processamento paralelo, etc., que criaram um novo vetor de crescimento de performance, diferente da miniaturização em si. 6 É importante lembrar que esta última não teria avançado sem um comprometimento com o avanço da primeira, sendo difícil delimitar a separação entre elas, quanto mais profundo se estuda este campo. O teste nada mais é que uma segurança sobre muitos poucos dos aspectos considerados durante um projeto, pois a própria viabilidade do sistema é comprometida se, durante um teste complexo, algum parâmetro for considerado de maneira incorreta. 7. Tecnologias emergentes Tanto quanto os sistemas semicondutores em si como certamente a área de testes de dispositivos semicondutores integrados em larga escala serão afetados pelo surgimento (e eventual crescimento em escala exponencial) da nanotecnologia e os nanorrobôs. Obviamente sem o escopo dado na ficção científica, esta tecnologia pode representar um divisor de águas no âmbito do teste dos dispositivos, onde, dentro de certas limitações físicas (como por exemplo densidade de corrente, dissipação de potência) podem existir microestruturas programáveis que, em um determinado ponto, atingirão uma escala de automação e individualização tão alta a ponto de representar o início de uma infinidade de aplicações que podem, ao mesmo tempo efetuar auto-teste, como em casos extremos (de difícil predição) de auto solução de problemas. Sem dúvida que o lixo tecnológico gerado nos últimos anos é uma barreira a ser transposta talvez por estes elementos, dotados de algum tipo de inteligência artificial, possam alterar dispositivos obsoletos e lhes conferir novas funções. Isto sem dúvida representa um impacto ambiental imenso e ao mesmo tempo um paradoxo filosófico-tecnológico importante, pois está sendo tratado de tecnologia que evolui de maneira autônoma. Isto fere algumas premissas admitidas como fundamentais para o ser humano, como aquela em que a criação não supera o criador [7]. Deixando a ficção científica de lado, os aspectos mais modernos condizentes ao teste de semicondutores em seu estágio de fabricação estão mais próximos das camadas de software que das camadas de hardware, em uma filosofia tecnológica não-ambígua. Em poucas palavras, isto significa que o ambiente utilizado para o teste deve seguir a mesma linha de pensamento do projeto do dispositivo, partindo do princípio que a aplicação não pode justificar o teste em si, e devem ser consideradas como coisas distintas. iTJRSC – Rua Tambaqui N. 180B – Distrito Industrial – CEP 69095-050 Manaus – Amazonas - Brazil Referências [1] CLARK, CJ RICCHETTI, Mike. Scalable Tester Architecture for Structural Test of Wafers and Packaged ICs. Intellitech Application Note. www.intellitech.com [2] Ray Yarema, William Wester. Wafer level Testing of ASICs for Silicon Strip Detectors. 4th International Meeting on Front End Electronics for Tracking Detectors at Future High Luminosity Colliders – Perugia, May 2000 [3] Laung-Terng Wang, Charles Stoud, Nur Touba, (ed.). System On Chip Test Architectures. Morgan-Kaufmann, Burlington. 2008. [4] Glenn R. Blackwell (ed.). The electronic Packaging Handbook. IEEE Press. 2000. [5] Jungram Lee, D.M.H.Walker, Linda Milor, Yeng Peng, Gene HillI. Performance Prediction for Test Cost Reduction. http://faculty.cs.tamu.edu/walker/pubs/lee99.pdf [6] Magno Fernandes – Trident NXP Semiconductor, conversa particular. Dezembro, 2009. [7] S.K.Prasad. Modern Concepts in Nanotechnology. Discovery Publishing. Nova Delhi, India, 2008.

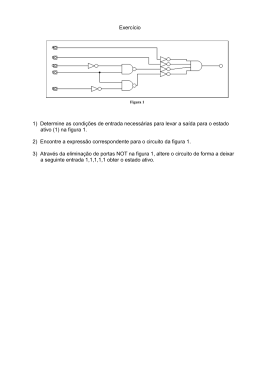

Download