Microeletrônica Germano Maioli Penello http://www.lee.eng.uerj.br/~germano/Microeletronica%20_%202015-1.html Sala 5145 (sala 17 do laboratorio de engenharia elétrica) Aula 17 1 Pauta ÁQUILA ROSA FIGUEIREDO 201110256011 ALLAN DANILO DE LIMA 201110063911 BERNADIN PINQUIERE 201110020415 DAVID XIMENES FURTADO 200810343411 HUGO LEONARDO RIOS DE ALMEIDA 201210076411 ISADORA MOTTA SALGADO 200920379411 JEFERSON DA SILVA PESSOA 201010067611 LAIS DA PAIXAO PINTO 200710030011 LEONARDO SOARES FARIA 200820515511 PEDRO DA COSTA DI MARCO 201020582111 THIAGO DO NASCIMENTO OLIVEIRA 201110308311 VINICIUS DE OLIVEIRA ALVES DA SILVA 201110066811 2 MOSFET Capacitância parasítica de depleção de fonte e dreno Modelo SPICE: Não confundir capacitância de depleção (polarização reversa) com capacitância de difusão (polarização direta)! 3 MOSFET Resistência parasítica de fonte e dreno O comprimento da região ativa aumenta a resistência parasítica em série com o MOSFET, determinada pelo número de quadrados na fonte (NRS) e dreno (NSD) NRS = comprimento da fonte / largura da fonte Resistência de folha incluída no modelo SPICE como srh (confira o valor no processo C5) 4 MOSFET Capacitância parasítica As capacitância parasíticas dependem da área da regíão ativa. Num desenho com números pares de capacitores, a região ativa de um terminal é maior que a do outro. Neste desenho, a área do S é maior que a do D. 5 MOSFET Capacitância parasítica Para obter boa resposta a altas frequências, é desejado que a capacitância maior seja aterrada (para NMOS) ou conectada ao VDD (PMOS) Menor capacitância Maior capacitância A menor capacitância descarrega pelos dois capacitores (maior resistência no caminho de descarga) enquanto a maior capacitância não carrega nem descarrega. 6 MOSFET Capacitância parasítica Dispositivo operando na região de inversão forte (strong inversion region) Canal formado entre o dreno e a fonte Capacitância não depende da extensão da difusão lateral 7 MOSFET Capacitância parasítica Dispositivo operando na região de depleção. Não há canal entre o dreno e fonte. Capacitância depende da extensão da difusão lateral Os parâmetros CGDO (gate-drain overlap capacitance) e CGSO são estipulados no modelo SPICE. Confira os valores no modelo do processo C5. 8 MOSFET Capacitância parasítica Os modelos do MOSFET devem incluir capacitâncias entre seus terminais e que essas capacitâncias dependem da região de operação do MOSFET. Quantos transistores temos nesta imagem? Imagem SEM 9 Modelos para projetos digitais Após ver alguns detalhes da fabricação dos MOSFETs, agora veremos modelos que utilizaremos em designs digitais De uma forma simples, o MOSFET é analisado em projetos digitais como uma chave logicamente controlada. 10 Modelos para projetos digitais Um dos pontos importantes em um circuito digital é o tempo de resposta do MOSFET. Para determinar o tempo de resposta, temos que associar ao MOSFET uma capacitância e uma resistência. Efeito Miller Considere o seguinte circuito: Inicialmente: Vin = VDD e Vout = 0 Se as tensões mudarem: Vin = 0 e Vout = VDD 11 Modelos para projetos digitais Efeito Miller Considere o seguinte circuito: Inicialmente: Vin = VDD e Vout = 0 Se as tensões mudarem: Vin = 0 e Vout = VDD A carga final fornecida é 12 Modelos para projetos digitais Efeito Miller Neste exemplo, a capacitância vista pela fonte de entrada e de saída é o dobro da capacitância conectada entre a entrada e a saída Usaremos este resultado para construir um modelo de MOSFET para análise digital. 13 Modelo de MOSFET digital Resistência de chaveamento efetiva Inicialmente o MOSFET está desligado (VGS = 0) e o dreno está em VDD. Aplicando instantaneamente uma tensão VDD na porta a corrente ID que flui inicialmente é: 14 Modelo de MOSFET digital Resistência de chaveamento efetiva Como estimar uma resistência para este resultado? 15 Modelo de MOSFET digital Resistência de chaveamento efetiva Como estimar uma resistência para este resultado? Inverso da inclinação da reta 16 Modelo de MOSFET digital Resistência de chaveamento efetiva Modelo inicial para um MOSFET chaveando Limitação desse modelo: Consideração feita que o tempo de subida e de descida é zero. O ponto que define a chave aberta e fechada é bem definido. Usado para cálculo a mão, apresentam resultados dentro de um fator de dois do resultado obtido por simulação ou pela experiência. 17 Modelo de MOSFET digital Resistência de chaveamento efetiva O modelo feito aqui não inclui a redução da mobilidade observada em dispositivos submicron. Um melhor resultado é obtido através de valores medidos ou simulados: NMOS de canal longo (fator de escala de 1 mm e VDD = 5V) PMOS de canal longo (fator de escala de 1 mm e VDD = 5V) mobilidade do elétron é maior que a do buraco 18 Modelo de MOSFET digital Resistência de chaveamento efetiva MOSFETs de canal curto não seguem a lei quadrática para a corrente! Usamos a corrente Ion para estimar a resistência NMOS de canal curto PMOS de canal longo 19 Modelo de MOSFET digital Resistência de chaveamento efetiva MOSFETs de canal curto não seguem a lei quadrática para a corrente! Usamos a corrente Ion para estimar a resistência NMOS de canal curto (fator de escala de 50 nm e VDD =1V) PMOS de canal longo (fator de escala de 1 mm) Equações reescritas para incluir L 20 Modelo de MOSFET digital Efeitos Capacitivos Adicionando efeitos das capacitâncias no modelo Cox é a capacitância na região de triodo (superestimado para facilitar as contas à mão – cálculo melhor é feito com simulações) Capacitância é vista como 2(Cox/2) = Cox 21 Modelo de MOSFET digital Efeitos Capacitivos Adicionando efeitos das capacitâncias no modelo Modelo melhorado 22 Modelo de MOSFET digital Constante de tempo Qual é a velocidade de chaveamento do MOSFET? Constante de tempo tn = RnCox Canal longo: Mais rápido quadraticamente com L Independente de W Mais rápido para VDD maior Canal curto: Mais rápido linearmente com L Independente de W Mais rápido para VDD maior 23 Modelo de MOSFET digital Resumo 24 Tempo de transição e de atraso Relembrando 25 Tempo de transição e de atraso Tempo de subida - tr Tempo de subida da saída- tLH Tempo de descida- tf Tempo de descida da saída- tHL Tempo de atraso low to high - tPLH Tempo de atraso high to low - tPHL 26 Tempo de transição e de atraso No nosso modelo digital: Ctot = capacitância total entre o dreno e o terra. Modelo simplificado para ser usado no cálculo a mão apenas! 27 Exemplo Descarga Carga 28 Exemplo Descarga Carga Canal longo Canal curto 29 Exemplo Descarga Carga 30 Exemplo Simulação 31 Projeto digital Por que NMOS e PMOS têm tamanhos diferentes? 32 Projeto digital Por que NMOS e PMOS têm tamanhos diferentes? Casamento da resistência de chaveamento efetiva 33

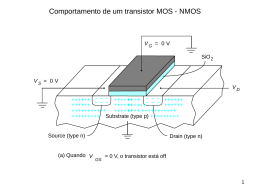

Baixar