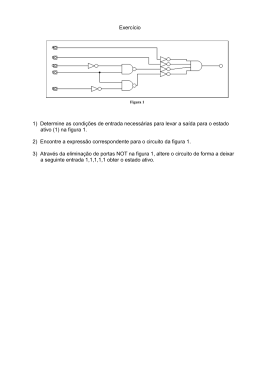

Ministério da Educação - MEC Secretaria de Educação Profissional e Tecnológica (SETEC) Instituto Federal de Educação, Ciência e Tecnologia do Ceará TÉCNICO EM ELETROTÉCNICA DISCIPLINA: ELETRÔNICA DIGITAL PROF: FCO MAURO P. DE ALBUQUERQUE Ministério da Educação - MEC Secretaria de Educação Profissional e Tecnológica (SETEC) Instituto Federal de Educação, Ciência e Tecnologia do Ceará ELETRÔNICA DIGITAL PROF: FCO MAURO P. DE ALBUQUERQUE TÉCNICO EM ELETROTÉCNICA CRÉDITOS Presidente Dilma Vana Rousseff Coordenador Adjunto - Reitoria Armênia Chaves Fernandes Vieira Ministro da Educação Aloizio Mercadante Oliva Supervisão - Reitoria André Monteiro de Castro Daniel Ferreira de Castro Secretaria de Educação Profissional e Tecnológica Marco Antonio de Oliveira Reitor do IFCE Virgilio Augusto Sales Araripe Pró-Reitor de Extensão Zandra Maria Ribeiro Mendes Dumaresq Pró-Reitor de Ensino Reuber Saraiva de Santiago Pró-Reitor de Administração Tássio Francisco Lofti Matos Pró-Reitor de Pesquisa, Pós Graduação e Inovação Auzuir Ripardo de Alenxandria Diretor Geral Campus Fortaleza Antonio Moises Filho de Oliveira Mota Diretor de Ensino Campus Fortaleza José Eduardo Souza Bastos Coordenador Geral – Reitoria Jose Wally Mendonça Menezes Coordenador Adjunto - Campus Fortaleza Fabio Alencar Mendonça Supervisores Daniel Gurgel Pinheiro Francisca Margareth Gomes de Araújo Francisco Alexandre de Souza George Cajazeiras Silveira José Roberto Bezerra Nildo Dias dos Santos Orientadores Deborah Almeida Sampaio Antônio Indalécio Feitosa APRESENTAÇÃO DA DISCIPLINA Este material foi desenvolvido para orientar os alunos do curso Técnico em Eletrotécnica TEC/PRONATEC para o aprendizado de Eletrônica Digital. Serão abordados os fundamentos básicos da Eletrônica Digital combinacional. O estudo será iniciado com circuitos que realizam funções lógicas baseados em componentes discretos, como diodos, resistores e transistores. Posteriormente serão utilizados circuitos integrados para realização do estudo restante da disciplina. ENSAIOS DE ELETRÔNICA DIGITAL TEORIA E PRÁTICA Prof. Luiz Francisco Coêlho Coutinho TODOS OS DIREITOS RESERVADOS - é proibida a reprodução total ou parcial desta apostila, por qualquer meio ou processo, especialmente por sistemas reprográficos, microfílmicos, fotográficos e gráficos, salvo com autorização, por escrito, do Autor. A violação dos direitos autorais é punível como crime (artigo 184 e parágrafos, do Código Penal, Lei n 6.895, de 17/12/80) com pena de prisão e multa, conjuntamente com busca e apreensão e indenizações diversas (artigos 122, 123, 124 e 126, da Lei n 5.988, de 14/12/73, dos Direitos Autorais). DATA DA ULTIMA REVISÃO: Fortaleza, Ano 2000/2 ENDEREÇO PARA CORRESPONDÊNCIAS: LUIZ FRANCISCO COELHO COUTINHO. Rua Mal. Deodoro, 421 Bloco A Apto 501 Benfica Fortaleza - Ceará CEP: 60.020-060 email: [email protected] PREFÁCIO Esta apostila foi elaborada com base nas diversas disciplinas de Sistemas Digitais que lecionei no Curso de Eletrotécnica do Centro Federal de Educação Tecnológica do Ceará, desde o ano de 1983. Todos os ensaios aqui apresentados foram exaustivamente testados por mim, bem como, por outros colegas que lecionam disciplinas semelhantes em outros Cursos do CEFET-CE. Cada ensaio apresenta inicialmente seus objetivos gerais, que direcionam o roteiro prático. Em seguida, uma pequena informação teórica é desenvolvida de forma a propiciar ao aluno, uma rápida revisão dos conceitos envolvidos em cada ensaio, objetivando um perfeito desenvolvimento dos procedimentos experimentais; entretanto, é interessante que o embasamento teórico se dê de forma plena em sala de aula, antes mesmo da realização de cada ensaio no laboratório. Todo o material a ser utilizado listado para o desenvolvimento dos ensaios é de fácil aquisição no mercado nacional, necessitando-se apenas como complemento de um kit apropriado para práticas de Eletrônica Digital ou mesmo de uma matriz de pontos (“Protoboard”) com uma Fonte de Tensão de +5 Volts, compatível com circuitos TTL e de um Gerador de Funções. Por último, alguns exercícios propostos foram colocados a titulo de revisão e fixação dos conteúdos estudados nas experiências, bem como alguns projetos que ficam a titulo de desafio para o aluno. Prof. Luiz FC Coutinho. AGRADECIMENTOS Gostaria de agradecer: À minha esposa Liduina e aos meus filhos Luís Rodolfo e Ana Lídia, pelo apoio e principalmente pela compreensão nas horas empenhadas nesse trabalho e irrecuperáveis no convívio pessoal do nosso dia a dia. Ao professor Pedro Urbano Braga de Albuquerque pelas relevantes contribuições no desenvolvimento de alguns ensaios e circuitos utilizados. Ao professor Antônio Moisés Filho de Oliveira Mota pelas sugestões fornecidas. À todos os meus colegas e alunos que direta ou indiretamente ajudaram-me a concluir esta apostila. Prof. Luiz FC Coutinho SUMÁRIO PREFÁCIO 03 AGRADECIMENTOS 05 SUMÁRIO 07 ENSAIO 1: Introdução a Eletrônica Digital 11 ENSAIO 2: Circuitos Lógicos Básicos Utilizando CI’s 19 ENSAIO 3: Portas TTL Tri-State 29 ENSAIO 4: Álgebra Booleana 35 ENSAIO 5: Projetos Práticos 43 ENSAIO 6: Circuitos Decodificadores 49 ENSAIO 7: Multiplexador de 4 Entradas 57 ENSAIO 8: Circuitos Somadores e Subtratores e Unidade de Lógica e Aritmética de 4 Bits 63 ENSAIO 9: Memória de Apenas Leitura - ROM 73 PROJETOS PRÁTICOS 147 APÊNDICE A: Gerador de base de Tempo CMOS 151 APÊNDICE B: TIMER 555 157 APÊNDICE C: FAMÍLIA TTL 165 APÊNDICE D: FAMÍLIA CMOS 177 BIBLIOGRAFIA 185 CIRCUITOS COMBINACIONAIS ENSAIO 1: INTRODUÇÃO À ELETRÔNICA DIGITAL OBJETIVOS: Montar Portas Lógicas a partir de componentes discretos; Construir Tabelas Verdades de Portas Lógicas Básicas. INFORMAÇÃO TEÓRICA: Embora a eletrônica digital moderna seja totalmente constituída de componentes integrados, utilizaremos neste primeiro contato, diodos, resistores e transistores sob a forma discreta para implementação das funções lógicas básicas. Toda a eletrônica digital está montada na combinação de Portas lógicas básicas, que serão vistas neste ensaio, e em unidades de memória, denominadas de flip-flops, que serão estudas posteriormente. A eletrônica digital, diferentemente da eletrônica linear, caracteriza-se pela utilização de dois estados lógicos bem definidos, aos quais podemos associar: ESTADO 0 0 NÃO CORTADO LOW 0V BLOQUEIA ESTADO 1 1 SIM SATURADO HIGH +5V CONDUZ Tabela 1 Estes dois estados mostrados na tabela 1, são geralmente citados como níveis lógicos, ou seja, uma tensão de +5 Vcc representaria um nível lógico 1 ou 1 lógico, enquanto que 0 Volt representaria um nível lógico 0 ou 0 lógico. Com o advento dos computadores, o sistema binário, se integra cada vez mais em nossa vida, sendo imprescindível ao engenheiro e ao técnico em eletrônica o conhecimento das particularidades associadas a tal sistema. No sistema binário a base é 2 e os símbolos comumente utilizados são o “0” e o “1”. A tabela 2 mostrada abaixo, faz uma relação entre o sistema decimal e o sistema binário. SISTEMA DECIMAL SISTEMA BINÁRIO 0 0 1 1 2 10 3 11 4 100 5 101 6 110 7 111 8 1000 9 1001 Tabela 2 PORTA LÓGICA: Uma Porta lógica consiste num bloco que possui duas ou mais entradas que assumem um dos dois estados lógicos, mostrados na tabela 1, denominados BIT (Binary Digit). A Porta fornece na saída um nível de acordo com o seu comportamento lógico característico, denominado de Tabela da Verdade. Um sinal lógico aparecerá na saída de uma determinada Porta somente para uma certa combinação de sinais aplicados nas suas entradas, o que caracteriza uma função lógica. Cada Porta lógica básica desenvolverá então uma função lógica básica e a partir delas outras funções poderão ser desenvolvidas com seus respectivos circuitos. As operações lógicas mais elementares são a “E”, a “OU” e a “NÃO” que serão apresentadas a seguir. Chamamos então de circuito lógico, aquele que realiza eletricamente o comportamento matemático das funções lógicas, onde as variáveis independentes, correspondem aos terminais de entrada e as dependentes ou as funções lógicas aos terminais de saída dos circuitos lógicos, figura 1. Figura 1 Os símbolos mais utilizados para as Portas lógicas são mostrados na figura 2 e correspondem à norma norteamericana. INVERSOR PORTA E PORTA OU PORTA NE PORTA NOU PORTA OUX Figura 2 Os símbolos lógicos utilizados nesse livro seguem o padrão americano, por ser mais difundido entre nós. Entretanto convém frisar que a IEC (“International Electrotechnical Comission”) desenvolveu uma linguagem simbólica muito poderosa e que está sendo adotada em diversos países, inclusive aqui no Brasil. A tabela 2 mostrada abaixo apresenta alguns símbolos usuais das 3 Normas mais conhecidas: NORMA CIRCUITO AMERICANA NORMA NORMA DIN IEC 40700 INVERSOR FUNÇÃO Y = A’ E Y = A.B OU Y=A+B NE Y = (A.B)’ NOU Y=(A + B)’ OUX Y=AB OUX’ Y=AB COMPARADOR Tabela 2 NE COM ENTRADAS INVERTIDAS Y=(A’.B)’ NOU COM ENTRADAS INVERTIDAS Y=(A’+B)’ FLIP FLOP Tabela 2 - continuação MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 2 transistores NPN 2 diodos de uso geral 3 resistores de 1K Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: Monte os circuitos mostrados nos quadros a seguir, observando com muita atenção as polaridades dos diodos e transistores. Ligue a saída Y em um indicador lógico e as entradas A e B a duas chaves de dados. Observe os indicadores lógicos correspondentes as entradas e a saída, complete a tabela verdade e responda que tipo de função cada circuito representa. CIRCUITO 1 TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y FUNÇÃO LÓGICA: CIRCUITO 2 TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y FUNÇÃO LÓGICA: CIRCUITO 3 TABELA VERDADE A 0 1 FUNÇÃO LÓGICA: Y CIRCUITO 4 TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y FUNÇÃO LÓGICA: CIRCUITO 5 FUNÇÃO LÓGICA: TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y EXERCÍCIOS PROPOSTOS: 1. Implemente um Inversor a partir de uma Porta: NE NOU OUX 2. Faça a tabela verdade do circuito mostrado abaixo. Que tipo de função lógica é equivalente a este circuito? 3. Construa outro circuito cuja tabela verdade seja a mesma da questão 3. 4. Converta cada número binário em decimal: 10111 2 = ____________10 10001112 = ___________10 11100002 = ___________10 5. Converta os seguintes números decimais em binário e em hexadecimal: 33 10 = ____________16 25510 = ____________16 102410 = ___________16 6. Qual é o maior valor decimal que pode ser representado por um número binário de: 4 bits 8 bits 16 bits 7. Relacione os números hexadecimais na seqüência entre 290H e 2BFH. 8. Desenhe o circuito lógico para Y = A . B’ . C + A’ . D + B’ . C 9. Simplifique a expressão Y da questão anterior e faça a sua tabela verdade. 10. Faça uma pesquisa sobre: FAN IN e FAN OUT CÓDIGO ASCII TTT x CMOS - características e interfaces RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 2: CIRCUITOS LÓGICOS BÁSICOS UTILIZANDO CI’S OBJETIVOS: Identificar a pinagem dos circuitos lógicos básicos; Verificar o funcionamento de portas lógicas; Construir circuitos digitais básicos utilizando circuitos integrados. Verificar as propriedades lógicas da função OUX; Implementar funções lógicas por meio de portas OUX; INFORMAÇÃO TEÓRICA: Os CI’s são pequenos blocos (chips) contendo componentes que formam os diversos circuitos eletrônicos, encapsulados em forma metálica, cerâmica ou plástica, com terminais de acesso às entradas e saídas dos circuitos. Um chip pode conter mais de 5.000.000 de componentes, variando, portanto o seu tamanho e o número de pinos. Existem CI’s comerciais com 6, 8, 10, 14, 16, 18, 24, 28 e 40 pinos, cuja numeração é feita em sentido antihorário, sendo o CI visto de cima, e tendo como referência uma marca ou furo característico, indicando sempre o pino 1, conforme mostrada a figura 1 e cujas dimensões são vistas na tabela 1. Figura 1: Circuitos Integrados Plásticos (Dual-In-Line). DIMENSÕES N DE PINOS mm 6 8 14 16 18 20 A max 7.88 7.88 7.88 7.88 7.88 7.88 B max 8.89 10.41 19.60 19.60 23.37 27.18 C max 6.61 6.61 6.61 6.61 6.86 6.86 Tabela 1 Existem tabelas e catálogos contendo a relação de cada CI com sua respectiva identificação interna e mostrando também todas as suas funções. Veja as Parte IV e V referentes aos CI’s TTL e CMOS utilizados nesse livro. EXPRESSÕES BOOLEANAS: O projeto de um circuito lógico combinacional inicia-se por construir uma tabela verdade que traduza em forma de 0’s e 1’s o questionamento do problema. A tabela verdade detalha a operação exata do circuito digital. Considere a tabela 2 mostrada a seguir. Observe que contém 3 variáveis independentes de entrada (A, B e C) e uma saída Y dependente de A, B e C. A saída Y somente é igual a 1 em duas situações: ABC = 010 e ABC = 111. A B C Y 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 PRODUTO FUNDAMENTAL Y = A’.B.C’ Y = A.B.C Tabela 2 Para que Y seja igual a 1 em cada situação sombreada da tabela 2 é necessário que A = C = 0 e B = 1 para o primeiro caso e A = B = C = 1 para o segundo caso. A expressão Booleana completa será então o somatório de todos os produtos fundamentais que levam a saída Y a 1 lógico. Então Y = A’.B.C’ + A.B.C. Esta expressão é às vezes chamada de forma de soma-de-produtos de uma expressão Booleana, e é mostrada novamente em destaque na figura 2. Figura 2 Note que esta expressão pode ser traduzida num padrão comum com a lógica E-OU de Portas lógicas. O diagrama lógico para este circuito é mostrado na figura 3, que executa a lógica descrita pela expressão booleana de soma-de-produtos. Figura 3 A FUNÇÃO OU EXCLUSIVA: A função OUX é uma operação lógica muito utilizada no dia a dia de quem trabalha com sistemas digitais. Sua função apresenta saída igual a 1 toda vez que as entradas forem diferentes, conforme mostra a tabela verdade da função indicada na Tabela 3. A B Y 0 0 0 0 1 1 1 0 1 1 1 0 Tabela 3 FUNÇÃO LÓGICA E SÍMBOLO: A função lógica para a porta OUX é dada por Y = A B cuja tabela verdade está mostrada na Tabela 3 e símbolo mostrado na figura 4. A forma mais rápida de implementar a função OUX é como indicada na figura 5. A saída Y é igual a 1 toda vez que as entradas forem diferentes entre si, conforme indicado na tabela da função mostrada na Tabela 3. Figura 4 Figura 5 PRECAUÇÕES A SEREM TOMADAS: Deve-se tomar bastante cuidado ao se lidar com os CI’s visto que seus terminais são bastante delicados; Evite, o máximo possível, o contato direto dos dedos com os terminais dos CI’s tipo CMOS, devido a possíveis descargas eletrostáticas, que poderão danificar irreversivelmente o CI; Nunca se deve ligar um CI de maneira errada, ou seja, alimentar a entrada positiva com uma tensão negativa e vice-versa; Observe sempre a seguinte polarização: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL : 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 4011 1 74LS04 1 74LS08 1 74LS32 1 74LS86 1 capacitor de 0,47F x 100V 1 capacitor de 0,68F x 100V 1 resistor de 1M @ ¼ W 1 resistor de 2,2M @ ¼ W Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: 1. Coloque o CI 4011 na base de montagem. Aplique 5 Volts ao terminal 14 do CI e 0 Volt no pino 7. Identifique as entradas e saídas do CI pelo diagrama lógico interno mostrado na figura 6. Figura 6 2. Monte o CIRCUITO 1 mostrado no quadro a seguir, observando com muita atenção as identificações de entradas e saídas das portas lógicas. Ligue a saída Y em um indicador lógico e as entradas A e B a duas chaves de dados. Observe os indicadores lógicos correspondentes as entradas e a saída, complete a tabela verdade e responda que tipo de função lógica o circuito representa. CIRCUITO 1 TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y FUNÇÃO LÓGICA: 3. Monte agora o CIRCUITO 2, conforme indicado a seguir. Ligue a saída Y em um indicador lógico e as entradas A e B a duas chaves de dados. Observe os indicadores lógicos correspondentes as entradas e a saída, complete a tabela verdade e responda que tipo de função o circuito representa. CIRCUITO 1 TABELA VERDADE A B 0 0 0 1 1 0 1 1 Y FUNÇÃO LÓGICA: 4. Monte agora o circuito mostrado na figura 7. Ligue a saída a um indicador lógico e responda a as questões abaixo: • Como se comporta o circuito? ___________________________________________________________________________________________ • Troque o capacitor por um de 0,68F. O que acontece com a freqüência de oscilação ? ___________________________________________________________________________________________ Figura 7: Astável com portas lógicas NE. 5. Através da tabela 4 mostrada a seguir, comprove que o tempo de oscilação (período) do circuito astável do procedimento 4 pode ser dado aproximadamente por: T = 1,4.R.C (segundos) onde R é o valor do resistor em Ohms e C o valor da capacitância em Faradays. R C 1M 0,47F 1M 0,68F 2,2M 0,47F 2,2M 0,68F T calculado T medido Tabela 4 6. Monte o circuito mostrado na figura 5 e verifique se o circuito opera segundo a função OUX, completando a tabela 2 que se segue. ENTRADAS SAÍDA A B 0 0 0 1 1 0 1 1 Y Tabela 5 FUNÇÃO LÓGICA: Y = _________________________ 7. Utilizando ainda o circuito do procedimento 1, complete os quadros mostrados abaixo para cada valor da variável B e verifique o funcionamento do INVERSOR CONTROLADO. B A 0 0 Y B A 0 1 0 1 1 1 Y 8. Monte agora o circuito mostrado na figura 8. Complete a Tabela 6 que segue e verifique o funcionamento do decodificador BINÁRIO para GRAY. Figura 8 D C B A 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 G4 Tabela 6 G3 G2 G1 EXERCÍCIOS PROPOSTOS: 1. Construa uma porta lógica OUX a partir de portas lógicas discretas. 2. Converta uma porta lógica OU em um porta lógica NE. 3. Explique o funcionamento do circuito lógico mostrado na figura 9. Figura 9: Biestável com portas lógicas NE 4. Desenhe o diagrama lógico para Y utilizando apenas o 4011. Y = A.B’ + B.C’ + A’.B.C 5. Simplifique e desenhe o circuito simplificado do exercício 4. 6. Desenhe um circuito p/a função OUX utilizando apenas a função NE. 7. Desenhe o circuito de um gerador/verificador de paridade ? 8. Qual a paridade do número 11001111 ? 9. Projete um decodificador GRAY para Binário. 10. Projete um decodificador BCD para 7 segmentos 11. Projete um decodificador capaz de acionar em um display de 7 sete segmentos as seguintes letras de uma forma seqüencial: C O C A C O E S C O L A L A 12. Projete um decodificador para teclado digital cuja saída corresponda ao código binário da tecla apertada. 13. Descreva detalhadamente o funcionamento do Inversor Controlado desenvolvido no Procedimento 7. RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 3: PORTAS TTL TRI-STATE OBJETIVOS: Verificar o funcionamento de uma Porta Tri-State; Verificar o funcionamento de circuitos com barramentos. INFORMAÇÃO TEÓRICA: As portas TTL podem ser diferenciadas quanto ao estágio de saída das mesmas. As três configurações de saída mais comuns são: Totem-Pole; Coletor Aberto; Tri-State. A porta TTL de saída Totem-Pole mostrada na figura 1a é comum na série normal e é usada a fim de aumentar a capacidade da porta de alimentar cargas capacitivas, sem diminuição da velocidade de chaveamento. A porta TTL de coletor aberto nada mais é do que o coletor do transistor de saída - figura 1b - não ligado a nenhum ponto, dai o nome, coletor aberto. Para que o mesmo funcione é então necessário se ligar um resistor externo entre a saída e o Vcc, como é mostrado na figura 2. Este resistor é chamado de “Pull-Up. O interesse em se usar coletor aberto é a possibilidade de se realizar a chamada lógica de ponto ou fiação. Para tanto, interconecta-se as saídas com coletor aberto desejadas, ligando-se as mesmas a um único resistor de Pull-Up, como mostra a figura 3. Figura 1 Figura 2 Figura 3 Suponha que N saídas em coletor aberto estejam ligadas entre si. Sejam YA, YB, .... YN tais saídas antes da conexão e Y a saída comum após a mesma. Note então que, se um dos transistores saturar, a saída correspondente será nível lógico “0”. Dessa forma, se um ou mais transistores saturarem, a saída comum Y será baixa. A saída Y só será alta quando todos os transistores estiverem abertos. Dessa forma Y = YA.YB. ... YN e teremos uma função E de fiação. As portas TTL com saída em três estados possuem, além das entradas normais, uma entrada de controle que determina se a saída é normal - baixa ou alta - ou se é o 3 estado - Z. Este 3 estado é caracterizado por apresentar uma alta impedância e, para efeito prático, pode-se considerar que a saída está aberta, isto é, desconectada do ponto em que tal saída está ligada. A figura 4 ilustra dois tipos de portas 3-State cuja tabela verdade pode ser vista na tabela 1 mostrada a seguir. Figura 4 C A Y1 C A Y2 0 0 1 0 0 Z 0 1 0 0 1 Z 1 0 Z 1 0 0 1 1 Z 1 1 1 Tabela 1 Uma das principais aplicações das portas 3-States consiste na implementação de barramentos para comunicação de dados, onde mais de um periférico pode ocupar o barramento sem que haja um conflito lógico. Naturalmen- te, além de seguidores e inversores, existem também os blocos funcionais com saída de 3 estados. Como por exemplo, podemos citar as memórias PROM, Portas de I/O, multiplexadores de dados, etc. Devido à existência do 3 estado Z é possível conectar entre si as saídas de portas com três estados, controlando-se as mesmas de tal forma que apenas uma saída esteja ativada de cada vez, sendo que as demais devem estar no estado Z. Este fato é que facilita a utilização de CI’s comerciais com 3 estados na execução de barramentos necessários na implementação de computadores. PRECAUÇÕES A SEREM TOMADAS: Observe sempre a seguinte polarização para os circuitos integrados: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL: 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 74LS04 1 74LS126 Fios para conecções 74LS126 PROCEDIMENTOS EXPERIMENTAIS: 1. Complete a T.V da porta 3-State mostrada na Figura 5. C A 0 0 0 1 1 0 1 1 Y Figura 5 2. Monte agora o circuito mostrado na Figura 6. Utilize para tanto um 74LS126 e um 74LS04. 3. Verifique o funcionamento do circuito transferindo a informação A para o barramento à DIREITA e a informação B para o barramento à ESQUERDA Figura 6 EXERCÍCIOS PROPOSTOS: 1. O que é uma porta de três estados ? Dê exemplos. 2. O que é porta de coletor aberto ? Dê exemplos. 3. O que é barramento ? 4. Mostre como ligar duas memórias ROM de 1K x 8 BITs em barramentos comuns. 5. Explique detalhadamente o funcionamento do circuito mostrado na figura 6. 6. O que é um circuito Flip Flop ? 7. Desenhe o diagrama interno do 74LS126. 8. Idem para o 74LS125. RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 4: ÁLGEBRA BOOLEANA OBJETIVOS: Montar circuitos combinacionais e obter suas Tabelas Verdades; Verificar o funcionamento de portas lógicas; Comprovar diversas operações e teoremas da Álgebra Booleana. INFORMAÇÃO TEÓRICA: Em meados do século XIX, George Boole (1815 - 1864) desenvolveu um sistema matemático de análise lógica que hoje é conhecido como Álgebra de Boole ou Álgebra Booleana. Suas propriedades, postulados e teoremas permitem a síntese e a otimização de circuitos digitais. A Álgebra Booleana foi inicialmente desenvolvida para tratar de problemas de lógica e raciocínio básico como questionamentos do tipo Verdadeiro-Falso, e assim permaneceu como uma parte da matemática pura até sua real aplicação prática em circuitos de chaveamento, desenvolvido por Claude Shannon em 1938 ! Através do domínio da Álgebra Booleana, podemos obter uma maior visão para a solução de determinados circuitos, bem como, obtermos margens para improvisações, às vezes bastantes lucrativas. Mas o verdadeiro valor da Álgebra Booleana está na simplificação de equações lógicas. Um circuito pode ser otimizado, o que implica numa economia de material, trabalho de montagem e de testes. Conhecer bem os fundamentos da Álgebra Booleana é essencial para um domínio perfeito da Eletrônica Digital. OPERAÇÕES FUNDAMENTAIS: A Álgebra Booleana possui três operações fundamentais: COMPLEMENTAÇÃO ou INVERSÃO, ADIÇÃO e MULTIPLICAÇÃO, que estão mostradas no quadro abaixo de uma forma resumida. COMPLEMENTAÇÃO ADIÇÃO MULTIPLICAÇÃO 0+0=0 0.0=0 0’ = 1 0+1=1 0.1=0 1’ = 0 1+0=1 1.0=0 1+1=1 1.1=1 LEIS FUNDAMENTAIS: A Álgebra Booleana possui três Leis Fundamentais que são: ASSOCIATIVA ADIÇÃO A+B+C = (A+B)+C = A+(B+C) MULTIPLICAÇÃO A.B.C = (A.B).C = A.(B.C) COMUTATIVA ADIÇÃO A+B=B+A MULTIPLICAÇÃO A.B = B.A DISTRIBUTIVA A.(B + C) = A.B + A.C Note que uma operação aparentemente simples como a associativa representa de fato uma grande mudança quanto a operacionalidade do circuito; observe: A + B + C nos dá a idéia que deveremos montar o circuito conforme mostrado na figura 1a e (A + B) + C, o circuito mostrado na figura 1b. É lógico que Y1 = Y2. Figura 1 TEOREMAS E OUTRAS IDENTIDADES: TEOREMAS de DE MORGAN: (A . B)’ = A’ + B’ O complemento do Produto é igual a Soma dos Complementos (A + B)’ = A’ . B’ O complemento da Soma é igual ao Produto dos Complementos IDENTIDADES: A + A.B = A A = A’.B = A + B (A + B). (A + C) = A + B.C A.(A + B) = A A.(B + C) = A.B + A.C A.B = A.(A’ + B) (A + B).(A’ + C) = A.C + A’.B (A + C).(A’ + B) = A.B + A’.C A’’ = A SIMPLIFICAÇÃO DE EXPRESSÕES: Aplicando estes conceitos da Álgebra Booleana poderemos facilmente simplificar expressões lógica, onde cada circuito corresponde a uma expressão lógica e se tão mais simples for a expressão lógica mais simples será o circuito. Veja como exemplo a expressão Y = A.B.C + A.C’ + A.B’. Realizando as devidas simplificações, teremos: EXPRESSÃO LEI/TEOREMA Y = A.(B.C + B’+ C’) Associativa/Comutativa Y = A. (B.C + (B+C)’) De Morgan Y = A.1 X + X’ = 1 Y=A X.1=X Resultado: a expressão simplificada agora é Y = A. PRECAUÇÕES A SEREM TOMADAS: Deve-se tomar bastante cuidado ao se lidar com os CI’s visto que seus terminais são bastante delicados; Evite, o máximo possível, o contato direto dos dedos com os terminais dos CI’s tipo CMOS, devido a possíveis descargas eletrostáticas, que poderão danificar irreversivelmente o CI; Nunca se deve ligar um CI de maneira errada, ou seja, alimentar a entrada positiva com uma tensão negativo e vice-versa; Observe sempre a seguinte polarização: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL : 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 74LS00 1 74LS04 1 74LS11 1 74LS32 Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: Para cada um dos seguintes procedimentos, montar o circuito e levantar sua tabela verdade. 1. OPERAÇÕES COM 1: PORTA E A Y1 PORTA OU A 0 0 1 1 Y2 2. OPERAÇÕES COM 0: PORTA E A Y1 PORTA OU A 0 0 1 1 Y2 3. OPERAÇÕES COM A MESMA VARIÁVEL: A Y1 Y2 Y3 Y4 Y1 = A.A Y2 = A + A Y3 = A.A’ Y4 = A + A’ 0 1 4. IDENTIDADE: A.(B + C) = A.B + A.C CIRCUITOS TABELA VERDADE A B C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Y1 Y2 5. TEOREMAS DE DE MORGAN: Y1 = (A.B)’ = Y2 = A’ + B’ Y3 = (A + B)’ = Y4 = A’. B’ A B 0 0 0 1 1 0 1 1 Y1 Y2 Y3 Y4 DESENHE AQUI OS CIRCUITOS PARA Y1, Y2, Y3 E Y4. EXERCÍCIOS PROPOSTOS: 1. Derive os teoremas: A + B = A + A’.B; A.B = A.(A’+ B); A A.B = A. B’; A (AB) = B. 2. Defina: Os teoremas de De Morgan; Saturação fraca e saturação forte; Equação de soma de produtos; Tabela Verdade. 3. Desenhe o circuito lógico descrito por Y = (A.B.C)’ . D’. Use o 74LS04, o 74LS08 e o 74LS11 com os números dos pinos. 4. Desenhe o circuito NE-NE para a expressão Y da questão anterior. Use o 74LS20 com os números dos pinos. 5. Prove que A(BC) = A(BC) 6. Desenhe o circuito que executa a tabela abaixo: A B C Y1 Y2 0 0 0 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 0 1 1 1 1 0 7. Simplifique o circuito da questão 6 e desenhe depois o circuito simplificado. 8. Desenhe uma porta OUX utilizando apenas portas NE. RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 5: PROJETOS PRÁTICOS PROJETO PRÁTICO I OBJETIVOS: Comprovar experimentalmente o desenvolvimento de um projeto combinacional simples; Construir um sensor de presença de água. PROJETO: Utilizando um motor-bomba, manter uma caixa d’água, na medida do possível, sempre cheia, a partir de uma cisterna. DESENVOLVIMENTO TEÓRICO: A figura 1 mostra uma esquema básico de como seria o projeto com suas respectivas variáveis de entradas e saída. SIMBOLOGIA: A = Caixa d’água C = Cisterna M = Motor-Bomba SA = Sensor de Presença de água na caixa d’água SC = Sensor de Presença de água na cisterna Figura 1 A tabela 1 abaixo mostra todas as posições possíveis para as diversas situações do sistema: SC SA M 0 0 0 0 1 0 1 0 1 1 1 0 Tabela 1 SIMBOLOGIA: SC 0 Não há água na cisterna CS 1 Há água na cisterna SA 0 Não há água na caixa d’água SA 1 Há água na caixa d’água M 0 Motor Parado M 1 Motor Ligado Através do processo do somatório dos produtos fundamentais, podemos concluir que M = SC.SA’ cujo diagrama lógico é mostrado na figura 2. Figura 2 SENSORES UTILIZADOS: De acordo com a tabela verdade do sistema o sensor deve indicar nível lógico 0 quando não houver água e nível lógico 1 quando houver água. Esta forma, uma opção é o circuito mostrado na figura 3, cuja tabela verdade é mostrada ao lado, que compara a resistência da água com uma resistência muito alta (4.7M) formando assim um divisor de tensão, que é detectada pela porta NÃO. Figura 3 Figura 4 Numa situação de presença d’água, conforme indica a tabela 2, teremos um divisor de tensão entre 4.7 M e a resistência elétrica da água, que na pior das hipóteses é algo em torno de algumas dezenas de K, com representa um nível lógico baixo no ponto X - Figura 4. MATERIAL A SER UTILIZADO: Placa de Montagem Experimental - Protoboard 1 4069 1 4081 1 BC 337 1 1N4004 Relé de Bobina 12 Volts com 1 contato reversível 2 resistor de 1K 2 resistores de 4.7M 1 LED Vermelho Fonte DC de 12 Volts Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: 1. Monte o circuito completo do sistema conforme mostrado na figura 5 e verifique se o circuito opera segundo o desenvolvimento do projeto, simulando a presença d’água nos sensores. Figura 5 2. Incorpore ao circuito mostrado na figura 5, um indicador capaz de sinalizar que a cisterna está sem água. PROJETO PRÁTICO II OBJETIVO: Construir uma Ponta Lógica Digital. PROJETO: Construir uma ponta lógica capaz de determinar o nível lógico de um ponto de um circuito digital. DESENVOLVIMENTO TEÓRICO: A figura 1 mostra um esquema básico de como seria o projeto, composto de 2 LEDs, sendo um vermelho para indicar o nível lógico alto e um verde para indicar o nível lógico baixo e de um oscilador de relaxação para permitir injetar sinais no circuito de teste quando necessário for. Figura 1 A tabela 1 a seguir mostra todas as posições possíveis para as diversas situações do projeto: A LED VM LED VD 0 apagado aceso 1 aceso apagado ABERTA piscando piscando Tabela 1 SIMBOLOGIA: LED VM 0 LED Vermelho apagado - Nível Baixo em A LED VM 1 LED Vermelho aceso - Nível Alto em A LED VD 0 LED Verde apagado - Nível Alto em A LED VD 1 LED Verde aceso - Nível Baixo em A MATERIAL A SER UTILIZADO: Placa de Montagem Experimental - Protoboard 1 4049 1 LED Vermelho de 5 mm 1 LED Verde de 5 mm 1 resistor de 330 K 2 resistores de 470 1 resistor de 1M 1 capacitor de 0,47 F Fonte DC de 12 Volts Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: 1. Monte o circuito completo do indicador de nível lógico digital conforme mostrado na figura 1 e verifique se o circuito opera segundo o desenvolvimento do projeto, simulando a presença dos dois níveis lógicos na entrada A. 2. Projete uma placa de circuito impresso para acondicionar o projeto dentro de uma caneta do tipo pincel atômico. ANOTE SUAS OBSERVAÇÕES E CONCLUSÕES ENSAIO 6: CIRCUITOS DECODIFICADORES OBJETIVOS: Verificar o funcionamento de um decodificador BCD 8421 para 7 segmentos; Conhecer um display de 7 segmentos. Verificar a operação de um decodificador 1 de 4; Usar um decodificador 1 de 4 como demultiplexador; Determinar o efeito de uma entrada aberta. DECODIFICADOR BCD 8421 PARA 7 SEGMENTOS INFORMAÇÃO TEÓRICA: Um decodificador nada mais é do que um tradutor que, nesse caso, traduzirá do código BCD (Binary Coded Decimal) para o código de 7 segmentos que formam um display com LEDs e nos possibilita escrever números de 0 a 9 e alguns outros símbolos especiais que poderemos formar. Figura 1 O decodificador BCD 8421 como também os displays com LEDs estão entre os circuitos digitais mais utilizados pela industria. O LED é um diodo semicondutor especial que emite luz quando diretamente polarizado. A maior parte dos displays com LEDs emitem luz vermelha e têm dos diodos distribuídos conforme mostra a figura 1, montados em cátodo ou ânodo comum. Para a formação de cada número, deveremos ter uma combinação de certos LEDs acessos. Por exemplo, para o número 2, deveremos ter os LEDs a = b = d = e = g = 1 e c = f = 0 se o display for de cátodo comum. O decodificador BCD 8421 para 7 segmentos se encarregará de fazer estas combinações, conforme a tabela a seguir. DECIMAL 0 1 2 3 4 5 6 7 8 9 D 0 0 0 0 0 0 0 0 1 1 C 0 0 0 0 1 1 1 1 0 0 B 0 0 1 1 0 0 1 1 0 0 A 0 1 0 1 0 1 0 1 0 1 a 1 0 1 1 0 1 1 1 1 1 b 1 1 1 1 1 0 0 1 1 1 c 1 1 0 1 1 1 1 1 1 1 d 1 0 1 0 0 1 1 0 1 1 e 1 0 1 0 0 0 1 0 1 0 f 1 0 0 0 1 1 1 0 1 1 g 0 0 1 1 1 1 1 0 1 1 PRECAUÇÕES A SEREM TOMADAS: Deve-se tomar bastante cuidado ao se lidar com os CI’s visto que seus terminais são bastante delicados; Evite, o máximo possível, o contato direto dos dedos com os terminais dos CI’s tipo CMOS, devido a possíveis descargas eletrostáticas, que poderão danificar irreversivelmente o CI; Nunca se deve ligar um CI de maneira errada, ou seja, alimentar a entrada positiva com uma tensão negativo e vice-versa; Observe sempre a seguinte polarização: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL : 5V 5% CMOS: 5V a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 4511 1 74LS139 PD 560 (ou display de cátodo comum equivalente) 7 resistores de 330 @ ¼ W Fios para conecções Figura 2 PROCEDIMENTOS EXPERIMENTAIS: 1. Identifique através da figura 2 as ligações do decodificador 4511 ao display PD 560, conforme indica a figura 3, deixando desabilitadas as funções especiais do decodificador - pinos 3, 4 e 5; complete o quadro abaixo e verifique o funcionamento do decodificador BCD para 7 segmentos. Figura 3 D 0 0 0 0 0 0 0 0 1 1 C 0 0 0 0 1 1 1 1 0 0 B 0 0 1 1 0 0 1 1 0 0 A 0 1 0 1 0 1 0 1 0 1 DISPLAY 2. Habilite cada uma das funções especiais do decodificador 4511 individualmente e verifique a sua função. PINO FUNÇÃO 3 = LT’ 4 = BI’ 5 = LE DECODIFICADOR 1 DE 4 Um decodificador lógico é um dispositivo MSI de entradas múltiplas com capacidade de selecionar uma única saída com base nos níveis de entrada. Um decodificador 1 de 4 significa que 1 entre 4 saídas pode ser selecionada de cada vez. Neste ensaio veremos primeiro a operação de decodificação de um decodificador 1 de 4, que depois será utilizado como um demultiplexador. O CI 74LS139 é um decodificador 1 de 4 duplo, isto é, existem dois decodificadores 1 de 4 em cada CI. O 74LS139 possui o diagrama lógico mostrado na figura 4. Os dois decodificadores são designados como decodificador 1 e decodificador 2. Cada decodificador tem três entradas, G’, A e B, e quatro saídas, Y0, Y1, Y2 e Y3. Figura 4 HABILITAÇÃO E ENDEREÇOS: A entrada G’ é o pino que habilita o funcionamento normal do CI. Quando G’ é mantido em nível alto, o CI não está habilitado e as saídas estão todas em nível alto, independentemente dos níveis presentes nas entradas A e B. Quando G’ é mantido em nível baixo, o CI está habilitado e apenas uma das saídas será ativada de acordo com o valor das entradas de endereçamentos A e B, assim como mostra a tabela a seguir. ENTRADAS SAÍDAS B A 1Y0 1Y1 1Y2 1Y3 0 0 0 1 1 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 As entradas A e B são de endereçamento. Quando o CI está habilitado, apenas uma saída está em nível baixo. Essa saída é selecionada de acordo com as entradas A e B como indica a tabela acima. As duas entradas A e B determinam a seleção de 1 a 4 saídas, portanto isto justifica o título de decodificador 1 de 4. DECODIFICADOR A SER UTILIZADO: 74LS139 Figura 5 PROCEDIMENTOS EXPERIMENTAIS: continuação 3. Identifique através da figura 5 as ligações do decodificador 74LS139, deixando habilitado o decodificador, ou seja, G’= 0; complete o quadro abaixo e verifique o funcionamento do decodificador 1 de 4. ENTRADAS SAÍDAS B A 0 0 0 1 1 0 1 1 1Y0 1Y1 1Y2 1Y3 2. Deixe a entrada B aberta e volte a repetir o procedimento 3. Complete o quadro a seguir. ENTRADAS B A Aberta 0 Aberta 1 SAÍDAS 1Y1 1Y2 1Y3 1Y4 3. O 74LS139 pode ser utilizado ainda como um demultiplexador. Isto é, um dado aplicado ao pino G’ pode ser enviado para uma das saídas conforme o endereço codificado pelas entradas A e B. Aplique agora um sinal de 10 Hz na entrada do pino G’. Selecione A e B e complete o quadro abaixo. B A 0 0 0 1 1 0 1 1 SAÍDA NA QUAL O DADO APARECE DESENHE AQUI O CIRCUITO DO PROCEDIMENTO 3. EXERCÍCIOS PROPOSTOS: 1. Qual a função dos resistores no circuito da figura 3? 2. Que valor de resistência será necessário para limitar a corrente de cada segmento do PD 560 em 10 mA se a alimentação do decodificador for de 12 Volts? 3. Em que condição o 4511 exigirá mais corrente da fonte ? 4. Dê aplicações práticas para cada função especial do 4511. 5. Quais as letras distintas que podem ser também mostradas pelo display PD 560 ? 6. Por que as letras B, D, G, I e S não são distintas ? 7. Se aplicarmos 1010 nas entradas do decodificador, o que aparecerá no displays ? 8. Qual é a entrada mais significativa do decodificador ? 9. É possível ligar um display de ânodo comum ao 4511 ? 10. Explique porque não utilizar um único resistor em série com o comum do display no circuito da figura 3. Mostre outra possível solução. 11. Defina: Multiplexador Demultiplexador Gerador de Paridade Verificador de Paridade 12. Faça um estudo detalhado sobre o CI 74LS138. 13. Mostre como ligar um 74LS138 como Demultiplexador. 14. Projete um decodificador do código BCD para o código GRAY. 15. Qual a diferença do 74LS139 para o 54LS139 ? 16. Utilizando somente portas NOU projete um circuito de um decodificador de duas entradas e quatro saídas. 17. Projete um decodificador BCD para HEXA. 18. Mediante o uso do decodificador 74LS154, mostre como implementar as seguintes funções lógicas: Y1 = A’BCD’ + A’BC’D + AB’C’D + ABCD Y2 = ABCD + A’B’C’D’ 19. Mediante o uso de um decodificador e de portas lógicas suplementares projete um gerador de paridade par e um gerador de paridade impar. 20. Mediante o uso de um DEMUX de quatro entradas, projete um circuito que gere a seguinte função lógica: Y = A + B.C’ RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 7: MULTIPLEXADOR DE 4 ENTRADAS OBJETIVOS: Verificar o funcionamento de um circuito multiplexador; Implementar um gerador de funções lógicas a partir de um multiplexador. INFORMAÇÃO TEÓRICA: Um multiplexador é um circuito capaz de selecionar uma única entrada de um grupo de entradas e enviá-la como única saída. A entrada selecionada é determinada por uma das linhas de endereços da entrada, como por exemplo, o multiplexador 74LS153 que possui 2 linhas de endereços, é capaz de selecionar apenas uma das 4 possíveis entradas . Figura 1 O 74LS153 COMO MULTIPLEXADOR E GERADOR DE FUNÇÕES. O diagrama lógico para o 74LS153 é mostrado na figura 1. Existem dois multiplexadores em cada CI, designados por multiplexador 1 e multiplexador 2. Os multiplexadores 1 e 2 são habilitados através das entradas 1G’ e 2G’ respectivamente e as linhas de endereços A e B são comum a ambos os multiplexadores. A tabela verdade 1 mostrada abaixo representa a função completa do multiplexador 74LS154 e a tabela verdade 2 mostrada a seguir, a sua função simplificada . SELET INPUTS DATA INPUTS STROBE OUTPUT B A C0 C1 C2 C3 G Y X X X X X X 1 0 0 0 0 X X X 0 0 0 0 1 X X X 0 1 0 1 X 0 X X 0 0 0 1 X 1 X X 0 1 1 0 X X 0 X 0 0 1 0 X X 1 X 0 1 1 1 X X X 0 0 0 1 1 X X X 1 0 1 Tabela 1 ENDEREÇOS SAÍDA B A Y 0 0 C0 0 1 C1 1 0 C2 1 1 C3 Tabela 2 Com duas variáveis quaisquer, A e B, por exemplo, há quatro funções possíveis (AB = 00, 01, 10 e 11). Um multiplexador de 4 X 2 pode ser usado para gerar essas funções, como é mostrado na tabela 1, bastando para isso, definirmos as diversas saídas de acordo com a função lógica que desejamos implementar. Como por exemplo, para implementarmos a função OUX com o 74LS153 é suficiente fazer 1C0 = 1C3 = 0 e 1C1 = 1C2 = 1 e obtermos a saída em 1Y. PRECAUÇÕES A SEREM TOMADAS: Deve-se tomar bastante cuidado ao se lidar com os CI’s visto que seus terminais são bastante delicados; Nunca se deve ligar um CI de maneira errada, ou seja, alimentar a entrada positiva com uma tensão negativa e vice-versa; Observe sempre a seguinte polarização: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL: 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 74LS153 Fios para conecções 74LS153 PROCEDIMENTOS EXPERIMENTAIS: 1. Monte o circuito mostrado na figura 2. 2. Aplique um sinal de 10 Hz em cada uma das entradas do MUX individualmente e complete a tabela verdade 3 mostrada abaixo. Verifique se o circuito opera segundo um multiplexador 4 x 1. ENDEREÇOS SAÍDA B A 0 0 0 1 1 0 1 1 Y Tabela 3 Figura 2 3. Monte agora o circuito mostrado na figura 3 completando a tabela que se segue. Verifique o funcionamento do multiplexador como gerador de função lógica. Responda: Que função o circuito da figura 3 gera ? Explique. Figura 3 ENDEREÇOS B A 0 0 0 1 1 0 1 1 FUNÇÃO LÓGICA: Y = _________________________ SAÍDA Y EXERCÍCIOS PROPOSTOS: 1. O que é gerador de Produtos Canônicos ? 2. Quantas variáveis de controle necessitamos para multiplexar 16 informações ? Generalize. 3. O que é Matriz de simples e duplo encadeamento ? 4. Quantos multiplexadores existem em um 74LS153 ? Idem 74LS154 ? 5. Mostre como obter um MUX 8 x 3 a partir de MUXs 4 x 2. 6. Mostre como gerar uma função lógica através de um MUX ? 7. Mostre como gerar a função Y = A.B.C + A.C + B.C’ com o 74LS153. 8. Projete um Meio Somador utilizando um 74LS153. RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 8: CIRCUITOS DE ARITMÉTICA E LÓGICA OBJETIVOS: Verificar as propriedades lógicas de um circuito ½ somador; Construir um somador completo; Implementar um somador/subtrator completo de 4 BITs. Verificar o funcionamento de uma Unidade de Lógica e Aritmética; Usar uma ULA para executar operações lógicas; Usar uma ULA para executar operações aritméticas. CIRCUITOS SOMADORES E SUBTRATORES Uma das grandes aplicações dos circuitos lógicos está nas Unidades Aritméticas dos sistemas digitais, onde são realizadas as operações em código binário. O circuito básico é o somador binário. Sua importância reside no fato de que em muitas unidades aritméticas, pode-se realizar qualquer operação matemática. A subtração, por exemplo, é obtida por um processo de soma de complementos, a multiplicação por somas e deslocamentos sucessivos. Dois circuitos digitais básicos são usados para executar estas funções aritméticas: o ½ somador e o somador completo. Chamamos de ½ somador ao circuito onde se pode somar apenas 2 BITs, dando como resultado uma soma S e o transporte T, figura 1. Figura 1 Um somador completo é um circuito lógico com três entradas de duas saídas que funciona segundo a tabela 1 a seguir. O somador pode operar três dígitos binários de cada vez e pode, portanto, ser usado para somar números binários em geral. A maneira mais simples de se construir um circuito somador completo é através de associações de ½ somadores, conforme mostra a figura 2. O somador completo é um circuito lógico fundamental em operações aritméticas, e está incorporado nos computadores digitais para executar funções aritméticas na unidade de lógica e aritmética - ULA. A B TE S TS 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Tabela 1 Figura 2 PRECAUÇÕES A SEREM TOMADAS: Observe sempre a seguinte polarização para os circuitos integrados: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL: 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 74LS04 1 74LS08 1 74LS32 1 74LS86 1 74LS181 1 74LS283 ou 74LS83 Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: 1. Monte o circuito mostrado na figura 2 e verifique se o circuito opera segundo um somador completo, completando a tabela 2 que se segue, onde TE é o transporte de entrada , TS é o transporte de saída e S é o resultado da soma. A B TE 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 TS S Tabela 2 2. Monte agora o circuito mostrado na figura 3 completando a tabela 3 que se segue. Verifique o funcionamento do circuito somador/subtrator completo de 4 BITs. Nas colunas indicadas por A e B entre com valores binários para os 2 números de 4 BITs: A = A4A3A2A1 e B = B4B3B2B1. Figura 3 A A4 A3 B A2 A1 B4 B3 SUB B2 B1 - SOMA/SUBTRAÇÃO TS S4 S3 S2 S1 0 0 0 0 0 1 1 1 1 1 Tabela 3 UNIDADE DE LÓGICA E ARITMÉTICA DE 4 BITS. Uma Unidade de Lógica e Aritmética (ULA) é uma circuito integrado (MSI) capaz de executar todas as possíveis operações lógicas com duas variáveis, assim como um número de operações aritméticas. OPERAÇÕES LÓGICAS: Considere duas variáveis lógicas A e B como entradas de um circuito lógico que tem apenas uma única saída F, como mostra a figura 4. Usando apenas as três funções lógicas básicas poderemos executar até 16 operações lógicas disponíveis para a saída - Tabela 1. Figura 4 Aparentemente existem mais possibilidades do que as 16 operações listadas na tabela 4. Por exemplo, a função A’. B’ não aparece na relação. Mas uma aplicação do teorema de De Morgan mostra que: A’. B’ = (A + B)’ e a função lógica NOU esta listada na tabela 1. Da mesma forma a função A’ + B’ não aparece na tabela 1, mas é equivalente à função NE - (A.B)’. N FUNÇÃO 1 A 2 A’ 3 B 4 B’ 5 A.A’ 6 A + A’ 7 A.B 8 (A.B)’ 9 A+B 10 (A + B)’ 11 A’. B 12 A. B’ 13 A’+ B 14 A + B’ 15 AB 16 (AB)’ Tabela 4 UNIDADE DE LÓGICA E ARITMÉTICA - 74LS181: O 74LS181 é mostrado na figura 5. As variáveis de entrada A e B são palavras de 4 BITs. A saída F também é de 4 BITs. As entradas de seleção de função (S0S1S2S3) determinam que função lógica deve ser executada, conforme mostra a tabela 5. Para operações lógicas, a entrada M (Modo de Seleção) deve estar em nível lógico alto e para operações aritméticas, a entrada M deve estar em nível lógico baixo. Podemos conectar mais de uma ULA para executar operações aritméticas com palavras de mais de 4 BITs. Cn é o pino de entrada de vai um, e C n + 4 é o pino de saída de vai um para ligações de outras ULAs. C n + 4 assume nível baixo quando ocorre o vai um. Os pinos P e G são pinos geradores de sinais. Os pinos P, propagador de vai um, e G, gerador de vai um, são usados onde altas velocidades de operações são exigidas, necessitando-se de sinais de vai um entre duas ULAs. Figura 5 S3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 ENTRADA DE SELEÇÃO DE MODO S2 S1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 LÓGICA M=1 F A’ (A + B)’ A’.B 0 lógico (A.B)’ B’ AB A.B’ A’ + B (AB)’ B A.B 1 lógico A + B’ A+B A Tabela 5 ARITMÉTICA M=0 F A A+B A + B’ Menos 1 A mais A.B’ (A + B) mais A.B’ A menos B menos 1 A.B’ menos 1 A mais A.B A mais B (A + B’) mais A.B A.B menos 1 A mais A (A + B) mais A (A + B’) mais A A menos 1 Neste ponto cabem as seguintes observações: Na tabela 2 diferenciamos: “+” representa OU lógico e “mais” representa soma aritmética, assim como ““ representa OUX lógico e “menos” representa subtração aritmética. A.B significa produto lógico ( Função E) de A com B, e assim por diante. As operações lógicas são realizadas BIT a BIT. A aritmética usada é a de complemento de 2. A saída [A + B] tem a configuração de coletor aberto. PROCEDIMENTOS EXPERIMENTAIS: continuação 3. Monte o circuito mostrado na figura 6. Escolha um valor para A e outro para B (ligue-os a +Vcc ou 0V conforme seja o caso) e complete a tabela 6 mostrada a seguir. Figura 6 A= B= ENTRADA DE SELEÇÃO DE MODO S3 S2 S1 S0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 Cn+4 F3 LÓGICA ARITMÉTICA M=1 M=0 F2 F1 F0 Cn+4 F3 F2 F1 F0 Tabela 6 2. Aplique nível lógico baixo no pino M para obter operações aritméticas de soma com pelo menos quatro valores diferentes de A e B e S3S2S1S0 = 1001. Ligue também Cn a nível alto. Lembre-se que será gerado um sinal de vai um na saída denominada Cn +4 toda vez que houver um estouro na capacidade dos 4 BITs, ou seja, a soma, for maior do que 11112. A= B= F= 3. Verifique também a operação de subtração com pelo menos dois valores diferentes de A e B. S3S2S1S0 = 0110, M = 0 e Cn = 0. Escolha um caso em que A > B e outro em que A < B. A= B= 4. Faça A = B e anote as saídas F com S3S2S1S0 = 0110, Cn = 1 e M = 0. F= A= B= F= [A = B] = NOTA: Como A = b e a saída é do tipo coletor aberto, é necessário ligar inversores na saída para se obter as respostas corretas. 5. Mude o valor de A ou de B e repita o procedimento 4. A= B= F= [A = B] = EXERCÍCIOS PROPOSTOS: 1. Mostre como transformar um somador completo em um ½ somador. 2. Mostre com transformar um ½ somador em um somador completo. 3. Por que o circuito somador é um circuito combinacional ? 4. Projete um ½ subtrator. 5. Projete um subtrator completo. 6. Projete o circuito do 74LS183. 7. Qual a função dos pinos 7 e 9 do 74LS183 ? 8. Mostre como obter um somador completo de 8 BITs com o 74LS183. 9. Mostre como obter um somador/subtrator completo de 8 BITs com o 74LS183. 10. Repita os exercícios 8 e 9 utilizando agora o 74LS83. 11. Explique detalhadamente o funcionamento do circuito mostrado abaixo. RESPOSTAS DOS EXERCÍCIOS PROPOSTOS: ENSAIO 9: MEMÓRIA ROM OBJETIVOS: Projetar uma ROM a diodos; Verificar o funcionamento de circuitos com ROM’s. INFORMAÇÃO TEÓRICA: Em um computador digital, a função da memória é armazenar informações na forma de palavras digitais. Tais palavras podem ser números de operandos, instruções de máquina, códigos de entrada e saída ou então são apenas dados. Numa primeira diferenciação, podemos classificar as Memórias em dois grandes tipos: ROM e RAM. Estudaremos nesse ensaio apenas as memórias ROM. As memórias ROM diferem das RAM pelo fato de não permitirem escrita quando em funcionamento em tempo real, isto é, no circuito a que foi destinada, daí o nome: ROM - memória de apenas leitura. O conteúdo da memória ROM é pré-programado pelo fabricante, muitas vezes, de acordo com o pedido específico do usuário e geralmente não pode ser modificado pelo mesmo. As principais características das memórias ROM’s são: Para cada endereço, existe apenas um dado ou palavra; Uma vez programada a memória, o dado é imutável e pode apenas ser lido; O conteúdo ou dado não é volátil, isto é, ele não será perdido quando se faz a leitura ou mesmo quando a fonte de alimentação é desligada. Um tipo muito usado de ROM é a PROM (Programmable Read_Only Memory) em que o conteúdo da memória ROM é programado pelo usuário. Essa programação comumente denominada de queima da PROM pode ser bastante trabalhosa, pelo fato de exigir um circuito especial para rompimento dos fusíveis (diodos) a fim de gravar o conteúdo desejado. Outro tipo de ROM é a EPROM (Erasable Programmable Read_Only Memory) que permite a reprogramação pelo usuário. Para cada nova programação, o usuário deve apagar totalmente o conteúdo anterior deixando a EPROM em condições de receber novos dados. As EPROM’s podem ainda ser classificadas quanto à sua maneira de ser apagada em: UVEPROM - Ultraviolet EPROM E2PROM - Electrically EPROM No caso da UVEPROM a programação do conteúdo é feita eletricamente, enquanto que o apagamento é realizado pela exposição à luz ultravioleta e para a E2PROM tanto a programação quanto o apagamento do conteúdo são feitas eletricamente, o que torna esta memória mais versátil. A ROM é um circuito combinacional, ou seja é um codificador. No entanto, o circuito comercial que contém a ROM já traz junto um decodificador como mostra a figura 1. Figura 1 O decodificador possui N entradas e M = 2 N saídas. Para cada condição de entrada, apenas uma saída é baixa, sendo as demais altas. É claro que poderia ser o contrário. A tabela 1 mostra um exemplo para N = 2 e M = 2 N = 4. A1 A0 S3 S2 S1 S0 0 0 1 1 1 0 0 1 1 1 0 1 1 0 1 0 1 1 1 1 0 1 1 1 Tabela 1 O codificador possui então M entradas e K saídas. Não há uma relação obrigatória entre M e K, ou seja, K pode ser qualquer valor inteiro. As saídas D’s são funções das palavras que se desejam armazenar. As entradas A 0, A1, ...,AN do decodificador são chamadas de bits de endereços. A cada endereço corresponde uma palavra de saída da ROM - D0, D1, .... ,DK-1 - que é a palavra que foi armazenada. Por exemplo, seja N = 2 e suponha que as palavras sejam de 4 BITs, isto é, Di = D3D2D1D0 e que sejam: D0 = 1001, D1 = 1010, D2 = 0001 e D3 = 0101 conforme mostra a tabela 2. A1 A2 S3 S2 S1 S0 Di D3 D2 D1 D0 0 0 1 1 1 0 D0 1 0 0 1 0 1 1 1 0 1 D1 1 0 1 0 1 0 1 0 1 1 D2 0 0 0 1 1 1 0 1 1 1 D3 0 1 0 1 Tabela 2 Observe que cada saída Di (i = 0, 1, 2 e 3) poderia ser obtida diretamente da tabela verdade. Entretanto o propósito é usar uma ROM. Uma maneira simples de se realizar a ROM é com diodos. Suponha a ROM do exemplo anterior. A figura 2 mostra o circuito de como seria essa ROM com o decodificador mostrado na tabela 2. Observe que os resistores R estão ligados ao +Vcc e na saída há inversores. Além disso, observe que os diodos conduzem quando a linha S a qual estão ligados está em nível lógico baixo. Se o nível lógico for alto, não conduzem. Por fim, quando um diodo ligado a uma linha DK conduz, estabelece nessa linha um nível lógico baixo, sendo que na saída do inversor teremos nível lógico alto. Figura 2 Em resumo, no circuito mostrado na figura 2, aonde houver um diodo, corresponderá a um nível lógico alto na saída e vice-versa. PRECAUÇÕES A SEREM TOMADAS: Observe sempre a seguinte polarização para os circuitos integrados: Vss, Vee ou GND - ligar ao negativo da fonte; Vcc ou Vdd - ligar ao positivo da fonte. Alimentação padrão dos CI’s: TTL: 5V 5% CMOS: 5 a 15 Volts. MATERIAL A SER UTILIZADO: KIT para práticas de Eletrônica Digital 1 74LS04 1 74LS139 7 Diodos 1N4148 4 Resistores de 10 K Fios para conecções PROCEDIMENTOS EXPERIMENTAIS: 1. Monte agora o circuito mostrado na Figura 3. Utilize para tanto um 74LS139 e um 74LS04. Figura 3 2. Verifique o funcionamento do circuito observando se os dados obtidos nas saídas D3, D2, D1 e D0 estão de acordo com os dados programados pelos diodos segundo a tabela 2. EXERCÍCIOS PROPOSTOS: 1. Implemente uma ROM a diodos capaz de gerar os seguintes dados utilizando o 74LS138 como decodificador: D7 D6 D5 D4 D3 D2 D1 D0 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 1 0 1 0 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 2. Faça uma pesquisa sobre a EPROM 2732 e a RAM 6116. 3. Implemente um banco de memória ROM de 2K x 8 a partir de memórias ROM de 512 x 8. 4. Idem exercício anterior, a partir de memórias ROM de 1K x 4. 5. Esquematize uma ROM com o seguinte conteúdo: 00H, ACH, F0H, 15H, 36H, F5H, FFH, FFH, FAH, 00H, FFH, FFH, 0CH, 11H, FFH, FFH, 36H, 83H, 76H, 90H, 00H, 00H, 00H, EEH, A8, E2, FFH, FFH, FFH. 6. Determine as palavras de endereço inicial e final para as memórias: 1K x 1 1K x 8 8K x 8 64K x 8 8. O que é uma PAL ? 9. Explique como gravar uma EPROM. 10. O que é um gravador de EPROM ? PROJETOS PRÁTICOS OBJETIVOS: Idealizar um sistema digital simples; Montar o sistema digital idealizado; Verificar o funcionamento do sistema idealizado. PREPARAÇÃO: Esta experiência oferece a oportunidade de desenvolver sua capacidade em Eletrônica Digital na sua área de atuação. Você deverá escolher um dos projetos listados a seguir, que seja de seu interesse particular, estudar suas características e limitações, familiarizar-se com seus detalhes de funcionamento e depois montar e verificar seu funcionamento na prática. Este projeto pode necessitar de trabalho de pesquisa e consultoria. Para ter uma certeza de que seu projeto é viável, é necessário antes uma discussão preliminar com seu professor orientador. Ao escolher seu projeto, faça um diagrama do circuito e de todos os detalhes construtivos que sejam relevantes para a elaboração e montagem do projeto. Existe uma grande variedade de diferentes circuitos digitais que são apropriados para o projeto. A seguir é dada uma lista que você pode utilizar como auxílio na escolha de seu projeto. PROJETO 1: Projete um circuito lógico capaz de acionar um motor-bomba, com a finalidade de manter o nível de uma caixa d’água sempre cheia, na medida do possível. Veja o Ensaio PROJETO PRÁTICO I. PROJETO 2: Projete um Provador Lógico. O nível 0 acenderá um LED verde enquanto o nível 1 acenderá um LED vermelho. Deve haver um teste de função para testar a operação correta do provador. Veja o Ensaio PROJETO PRÁTICO II. PROJETO 3: Projete um circuito que indique por LEDs o estado lógico de cada pino de um CI de 14 pinos. PROJETO 4: Projete um circuito que funcione como um PROM programável. PROJETO 5: Projete um contador de freqüência. PROJETO 6: Projete um instrumento para medir período de tempo. PROJETO 7: Projete um decodificador de teclado que acione uma trava elétrica. PROJETO 8: Projete um conversor analógico-digital de 8 bits. PROJETO 9: Projete um Voltímetro Digital 3 ½ Dígitos. PROJETO 10: Projete um Relógio Digital com HH:MM:SS. PROJETO 11: Projete um Termômetro Digital 0 a 100C. PROJETO 12: Projete um Gerador de Funções. PROJETO 13: Projete um Multialarme Residencial. PROJETO 14: Projete Cronômetro Digital com sensores acionados pela luz. PROJETO 15: Projete um Jogo de luz seqüencial com 20 canais. PROJETO 16: Projete um Velocímetro Digital para Bicicletas. PROJETO 17: Projete um Tacômetro Digital com 3 dígitos PROJETO 18: Projete uma Fechadura Digital com teclado. PROJETO 19: Projete uma Fechadura Ótica a infravermelho PROJETO 20: Projete um Carregador Automático de Baterias PWM (Pulse Width Modulation). PROJETO 21: Projete uma Luz de Emergência. PROJETO 22: Projete um “Caça Níqueis”. PROJETO 23: Projete um Teste de Tensão para Autos. PROJETO 24: Projete um Inversor para Lâmpadas Fluorescente. PROJETO 25: Projete um Sensor/Indicador de Nível. PROCEDIMENTOS: Seu projeto deve ser elaborado de forma ordenada e com critérios. Os procedimentos a seguir irão ajudá-lo a se organizar. 1. Após decidir qual será seu projeto, discuta com seu professor para que se estabeleçam detalhes referentes a(o): PROJETO DESCRIÇÃO GERAL DETALHES PARCIAIS PROFESSOR ORIENTADOR DATA DE CONCLUSÃO DOCUMENTAÇÃO 2. Todo sistema deve ter especificações detalhadas. Faça uma lista das especificações descrevendo os detalhes de operação. Inclua as necessidades de fonte de alimentação, fonte de sinal, as condições ambientais às quais será submetido o circuito, limitações, condições dos sinais de entrada e saída e outras especificações que julgar necessárias. 3. Desenhe o diagrama completo do circuito. Identifique todos os componentes usados e faça uma lista dos mesmos. 4. Desenhe um layout mostrando as locações de cada parte do circuito com o objetivo de facilitar sua montagem. 5. Monte o circuito. Faça as medições e anotações que julgar necessárias e verifique se o circuito funciona de acordo com o projeto. Seu professor orientador deve fazer um comentário sobre o sistema e avaliar essa etapa do projeto. PROFESSOR ORIENTADOR COMENTÁRIOS DATA DA AVALIAÇÃO 6. Anote todas as observações importantes, conclusões e/ou precauções a respeito de seu projeto. Compare as especificações desejadas e as especificações e medições finais obtidas no projeto. Você tem alguma sugestão para melhorar ou expandir ainda mais seu projeto? 7. Faça a Documentação do Projeto. Inclua a bibliografia utilizada. APÊNDICE A: GERADOR DE BASE DE TEMPO CMOS O diagrama do circuito de um multivibrador astável com portas NOU de CMOS está mostrado na figura 1a. Para que possamos descrever as características essenciais da operação sem atingir uma profusão de pequenos detalhes, suporemos um característica entrada-saída para as portas, como mostrado na figura 2. Além disto, iremos desprezar as impedâncias de saída das portas e supondo também que os diodos de proteção são ideais. Assim, suporemos que a tensão de limiar e a tensão de condução dos diodos são iguais a zero Volts. Figura 1 Figura 2 Com estas hipóteses simplificadoras, é visível que V e V20 são complementares. Quando uma está em Vss, a outra esta em zero, e vice versa. Agora, vamos supor que V1i está acima de VT. Então, V esta em zero e V20 esta na tensão fixa Vss. Assim, V1i está indo assintoticamente para zero. Quando V1i atinge VT, V mudará abruptamente para Vss e V20 mudará abruptamente para zero. Esta mudança abrupta em V20 será transmitida através de C para V1i. A variação para baixo consequentemente em V1i estará limitada à terra devido à ação grampeadora do diodo de proteção na entrada da porta G1 (figura 3). Agora V1i está abaixo de VT e está indo assintoticamente para Vss, que é a tensão em V. Portanto, haverá um chaveamento periódico em V20, V e V1i, como mostrado pelas formas de onda idealizadas da figura 1b, 1c e 1d. Evidentemente, a operação do circuito não depende do fato de VT ser igual a Vss/2. Se, entretanto, VT Vss/2, a forma de onda não será simétrica; isto é, teremos T1 T2. Em geral, teremos: e para T1 = T2 obteremos: T= 1,4RC (segundos) Deveremos notar que as formas de onda na figura 1 são na verdade inconsistentes uma com a outra, pois observamos que do lado do capacitor a tensão muda abruptamente de Vss, enquanto do outro lado a mudança é de Vss/2. Em um circuito físico, a tensão Vss/2 que não aparece em V1i fica na impedância de saída da porta G2 e no diodo de entrada da porta G1. Isto é, em cada transição há um breve intervalo de tempo durante o qual V20 não atinge Vss ou 0 e durante o mesmo intervalo V1i vai acima de Vss e abaixo da terra. Durante este breve intervalo, o capacitor se carrega ou descarrega, mudando sua tensão de Vss/2. Formas de onda mais realistas estão ilustradas na figura 4. Figura 3 Figura 4 PROCEDIMENTOS EXPERIMENTAIS: 1. Utilizando o 4001 (portas NOU de duas entradas) projete o circuito mostrado na figura 1 para oscilar numa freqüência de 1 Hz. 2. Compare o resultado do procedimento experimental 1 com o valor calculado pela expressão T = 1,4RC. Comente as diferenças observadas. 3. Repita os procedimentos 1 e 2 para uma freqüência de 10 Hz. EXERCÍCIOS PROPOSTOS: 1. Qual o tempo de ciclo do relógio para um sistema que usa uma freqüência de 500 KHz ? E um relógio de 1 MHz ? 2. O atraso de propagação total em um flip flop é de 100 nseg. Qual a freqüência máxima do clock que pode ser usado com esse flip flop ? 3. Projete o circuito da figura 1 para oscilar numa freqüência de 100 KHz. 4. Defina: Astável, Monoestável e Biestável Ciclo de atividade Tempo de diminuição Tempo de elevação Tempo do ciclo do relógio 5. Calcule o tempo do ciclo do relógio para um sistema que usa um relógio com freqüência de: 20 KHz 500 KHz 1MHz 6. Quais seriam os pontos de 10 e 90 % na forma de onda mostrada na figura 1b se a amplitude variasse de 0 a +5 Volts ? APÊNDICE B: TIMER 555 O temporizador integrado 555 permite implementar redes de retardo e circuitos osciladores bastantes estáveis. Sua estabilidade é independente da fonte de alimentação, sendo determinada apenas pela tolerância da malha RC externamente conectada ao circuito. ESTRUTURA BÁSICA: O timer 555 consiste basicamente em dois comparadores de tensão e de um biestável, conforme mostra a figura 1. O sistema dos dois comparadores fixa as tensões de limiar a 1/3 e 2/3 de Vcc. O biestável RS controla a saída e a comutação do transistor de descarga, que por sua vez descarrega o capacitor externo de temporização. Figura 1 DADOS OPERACIONAIS: Tensão de Operação: 4,5 a 16 Volts Corrente de repouso: com Vcc = 5V: 3 mA com Vcc = 15V: 10 mA Desvio de freqüência na modalidade MVA: 90 ppm/K; 0,15%/V Corrente máxima de saída: 200 mA. ENCAPSULAMENTO DIP DE 8 PINOS: Figura 2 OPERAÇÃO COMO MONOESTÁVEL (MVM): Quando o 555 for utilizado como MVM, a saída estará normalmente baixa. O transistor interno ligado ao pino 7 acopla o capacitor C1 externo à terra. O MVM é ativado mediante um impulso negativo no pino 2, ocasião em que o capacitor externo C1 passa a ser carregado através do resistor externo de tempo R1 - Figura 3. Assim que sua carga atingir o limiar de 2/3 de Vcc, o MVM comuta ao seu nível estável (baixo) e C1 descarrega-se através do transistor interno. A duração do pulso de saída é determinado através de R1 e C1 por meio da equação mostrada abaixo: T = 1,1xR1xC1 segundos (eq. I) Figura 3 Caso o pino de RESET não seja utilizado, deve-se ligá-lo a Vcc. A duração do pulso de saída pode ainda ser controlada, dentro de certos limites, através do pino 5, o qual normalmente recebe um capacitor de 0,01F ligado à terra. OPERAÇÃO COMO ASTÁVEL (MVA): Interligando-se os pinos 2 e 6 e acrescentando o resistor R3 ao circuito, pode-se converter o MVM em um MVA conforme pode ser visto na figura 4. O MVA possui uma freqüência e um ciclo de trabalho fixo. A ligação dos pinos 2 e 6 permite que o 555 seja ativado sempre que C1 é descarregado abaixo de 1/3 de Vcc e desativado tão logo o capacitor se atinja o limiar de carga em 2/3 de Vcc. Assim, a tensão sobre esse capacitor alterna-se periodicamente entre 1/3 e 2/3 de Vcc. A freqüência de oscilação resultante pode ser determinada pela equação abaixo: f = 1,44/[(R1 + 2xR3) x C1] Hertz (eq. II) Se fizermos o valor de R1 muito maior do que R3 a expressão acima poderá ser dado por: f = 0,72/[R1 x C1] Hertz (eq. III) Para o circuito da figura 4 podemos ainda escrever as seguintes equações referentes ao período de oscilação: TH = 0,693(R1 + R3)C1 segundos (eq. IV) TL = 0,693 R3C1 segundos (eq. V) Figura 4 PROCEDIMENTOS EXPERIMENTAIS: 1. Monte o circuito mostrado na figura 3 com valores diferentes para R1 e C1 conforme mostra a tabela abaixo. 2. Utilizando um relógio de pulso com indicadores de segundos, determine o tempo em que a saída permanece alta após um pulso de disparo e compare com o valor teoricamente calculado. R1 C1 100K 10F 470 K 10F 1M 10F 100K 100F 470 K 100F 1M 100F Tempo Medido Tempo Calculado 3. Compare o resultado do valor medido com o valor calculado pela expressão T = 1,1R1C1. Comente as diferenças observadas. _______________________________________________________________________________________________ _______________________________________________________________________________________________ __ 4. O objetivo desse procedimento é observar o funcionamento do terminal de RESET do 555. Para R1 = 1M e C1 = 100F, dispare o MVM e aplique após alguns segundos um pulso negativo ao terminal de RESET. Observe o comportamento da saída. Desenhe abaixo o diagrama de tempo obtido. 5. Utilizando as equações IV e V projete o circuito da figura 4 para oscilar em 1 Hz. 6. Monte o circuito da figura 4 e verifique se o seu funcionamento está de acordo com o projeto desenvolvido. Anote suas observações. _______________________________________________________________________________________________ _______________________________________________________________________________________________ _ 7. Monte agora o circuito mostrado na figura 5 e observe o funcionamento do 555 quando ligado em cascata. Nota: Para um período de tempo maior do que 2 horas o circuito do MVM deve ser ligado em cascata conforme é mostrado na figura 5, pois o circuito torna-se muito instável devido a corrente de carga no capacitor se aproximar do valor da sua corrente de fuga reversa, impossibilitando dessa forma a sua carga. Figura 5 EXERCÍCIOS PROPOSTOS: 1. Mostre para o MVM que T = 1,1 R1C1 segundos. 2. Mostre para o MVA que: TH = 0,693(R1 + R3)C1 segundos e TL = 0,693(R3)C1 segundos. 3. Demonstre a equação f = 1,44/[(R1 + 2xR3) x C1] Hertz 4. Projete o circuito da figura 3 para oscilar numa freqüência de 10 Hz. 5. Idem para oscilar numa freqüência 60 Hz. 6. Projete o circuito o MVM para um período de 1 hora. 7. Idem 3 horas. 8. Utilizando um MVM desenvolva um circuito capaz de funcionar como um Relé de Tempo. 9. Desenvolva com o 555 um circuito que permita a variação do ciclo de operação sem alterar a freqüência de saída. 10. Desenvolva com o 555 um circuito com dois MVA de forma a produzir o som de duas notas musicais. CIRCUITOS INTEGRADOS TTL UTILIZADOS NOS ENSAIOS ENSAIOS DE ELETRÔNICA DIGITAL TEORIA E PRÁTICA PROF. LUIZ FC COUTINHO 74XX 4 Portas NE de 2 Entradas 00 01 FUNÇÃO LÓGICA: ___ Y = A.B 4 Portas NE de 2 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: ___ Y = A.B 4 Portas NOU de 2 Entradas 02 03 FUNÇÃO LÓGICA: ___ Y = A+B 4 Portas NE de 2 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: ___ Y = A.B 6 Portas INVERSORAS 04 FUNÇÃO LÓGICA: Y = A’ 05 6 Portas INVERSORAS com Saídas em Coletor Aberto FUNÇÃO LÓGICA: Y = A’ 06 6 Portas INVERSORAS Buffers/Drivers com Saídas em Coletor Aberto FUNÇÃO LÓGICA: Y = A’ 07 6 Portas BUFFERS / DRIVERS com Saídas em Coletor Aberto FUNÇÃO LÓGICA: Y=A 4 Portas E de 2 Entradas 08 FUNÇÃO LÓGICA: Y = A.B 09 4 Portas E de 2 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: Y = A.B 3 Portas NE de 3 Entradas 10 FUNÇÃO LÓGICA: ______ Y=A.B.C 3 Portas E de 3 Entradas 11 FUNÇÃO LÓGICA: Y = A.B.C 12 3 Portas NE de 3 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: _____ Y = A.B.C 2 Portas NE de 4 Entradas Schmitt Triggers 13 FUNÇÃO LÓGICA: ______ Y = A.B.C.D 6 Portas INVERSORAS Schmitt Triggers 14 FUNÇÃO LÓGICA: Y = A’ 2 Portas NE de 4 Entradas 20 FUNÇÃO LÓGICA: ______ Y = A.B.C.D 2 Portas E de 4 Entradas 21 FUNÇÃO LÓGICA: Y = A.B.C.D 2 Portas NOU de 4 Entradas com Strobe 25 FUNÇÃO LÓGICA: ___________ Y = G.(A+B+C+D) 3 Portas NOU de 3 Entradas 27 FUNÇÃO LÓGICA: _____ Y = A+B+C 1 Portas NE de 8 Entradas 30 FUNÇÃO LÓGICA: ____ Y = A.B.C 4 Portas OU de 2 Entradas 32 FUNÇÃO LÓGICA: Y = A+B 33 2 Portas NOU de 4 Entradas com Saída em Coletor Aberto FUNÇÃO LÓGICA: ___ Y = A+B 4 Portas NE de 2 Entradas Buffer 37 FUNÇÃO LÓGICA: ___ Y = A.B 38 40 4 Portas NE de 2 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: ___ Y = A.B 2 Portas NE de 4 Entradas com Saídas em Coletor Aberto FUNÇÃO LÓGICA: ______ Y = A.B.C.D 2 Portas E/NOU de 4 Entradas 51 73 74 75 FUNÇÃO LÓGICA: _______ Y = A.B +C.D 2 FLIP FLOPS JK com Entradas de Clear 2 FLIP FLOPS D com Entradas de Preset e Clear 4 LACTCHES BIESTÁVEIS 76 2 FLIP FLOPS JK com Entradas de Preset e Clear 83 SOMADOR PLENO DE 4 BITS 4 Portas OUX de 2 Entradas 86 FUNÇÃO LÓGICA: Y=AB Memória de Apenas Leitura de 256 BITs com Saídas em Coletor Aberto 88 32 palavras de 8 BITs. Memória de Escrita e Leitura 89 90 16 palavras de 4 BITs Contador de Década Shift Register de 8 BITs 91 Serial IN - Serial OUT Shift Register de 4 BITs 95 Paralelo IN - Paralelo OUT Serial IN 4 BUFFER 3 STATE 125 FUNÇÃO LÓGICA: Y = A para G=0 Y = Z para G=1 4 BUFFER 3 STATE 126 138 139 FUNÇÃO LÓGICA: Y = A para G=1 Y = Z para G=0 1 DECODER 3 TO 8 2 DECODER 2 TO 4 153 181 240 241 244 245 DUAL 1OF 4 LINE DATA SELECTOR / MULTIPLEXER UNIDADE DE LÓGICA E ARITMÉTICA - ULA 8 BUFFERS INVERSORES COM SAÍDAS 3-STATE 8 BUFFERS NÃO INVERSORES COM SAÍDAS 3-STATE 8 BUFFERS NÃO INVERSORES COM SAÍDAS 3-STATE 8 BUFFERS NÃO INVERSORES COM SAÍDA 3STATE 283 SOMADOR PLENO DE 4 BITS 373 8 LATCHES TIPO D COM CONTROLE POR NÍVEL 374 8 LATCHES TIPO D COM CONTROLE POR BORDA CIRCUITOS INTEGRADOS CMOS UTILIZADOS NOS ENSAIOS ENSAIOS DE ELETRÔNICA DIGITAL TEORIA E PRÁTICA PROF. LUIZ FC COUTINHO 40XX 00 2 Portas NOU de 3 Entradas mais 1 INVERSOR FUNÇÕES LÓGICAS: _____ _ Y = A+B+C e Y = A 01 4 Portas NOU de 2 Entradas FUNÇÃO LÓGICA: ___ Y = A+B 2 Portas NOU de 4 Entradas 02 06 08 FUNÇÃO LÓGICA: ________ Y = A+B+C+D 18 Stage Static Shift Register SOMADOR PLENO DE 4 BITS 4 Portas NE de 2 Entradas 11 12 13 14 15 16 FUNÇÃO LÓGICA: ___ Y = A.B 2 Portas NE de 4 Entradas FUNÇÃO LÓGICA: ______ Y = A.B.C.D Dual FLIP FLOP tipo D 8 STAGE STATIC SHIFT REGISTERS DUAL 4 STAGE STATIC SHIFT REGISTERS 4 CHAVES BILATERAIS 17 CONTADOR DIVISOR COM 10 SAÍDAS DECODIFICADAS 3 PORTAS NE DE 3 ENTRADAS 23 25 26 27 29 3 PORTAS NOU DE 3 ENTRADAS CONTADOR DE DÉCADA SÍNCRONO COM DECODIFICADOR PARA 7 SEGMENTOS DUAL FLIP FLOP JK MASTERSLAVE CONTADOR UP/DOWN PRESETTABLE 4 Portas OUX de 2 Entradas 30 FUNÇÃO LÓGICA: Y = AB 6 INVERSORES BUFFER 49 FUNÇÃO LÓGICA: Y = A’ 66 4 CHAVES BILATERAIS 6 INVERSORES 69 FUNÇÃO LÓGICA: Y = A’ 4 Portas OUX de 2 Entradas 70 FUNÇÃO LÓGICA: Y = AB 4 Portas OU de 2 Entradas 71 FUNÇÃO LÓGICA: Y = A+B 2 Portas OU de 4 Entradas 72 FUNÇÃO LÓGICA: Y = A+B+C+D 3 PORTAS E de 3 Entradas 73 FUNÇÃO LÓGICA: Y = A.B.C 3 PORTAS OU de 3 Entradas 75 FUNÇÃO LÓGICA: Y = A+B+C 4 Portas E de 2 Entradas 81 FUNÇÃO LÓGICA: Y = A.B 2 Portas E de 4 Entradas 82 FUNÇÃO LÓGICA: Y = A.B.C.D 4 Portas NE de 2 Entradas Schmitt Triggers 93 FUNÇÃO LÓGICA: ___ Y = A.B BIBLIOGRAFIA 1. Capuano, Francisco G. e Idoeta, Ivan, - Elementos de Eletrônica Digital - Livro Érica Editora Ltda, 1997. 2. Malvino, Albert P. e Leach, Donald P., - Eletrônica Digital, Princípios e Aplicações - Vol. 1 e 2 - Editora Mc Graw-Hill Ltda, 1988. 3. Marco, Coppelli. e Bruno, Stortoni, - Esercizi di Elettronica Digitale - La Sovrana Editrice - Fermo, 1984. 4. Millman, Jacob. e Halkias, Christos, - Eletrônica Dispositivos e Circuitos - Vol. 1 e 2 - Editora Mc Graw-Hill Ltda, 1981. 5. Natale, Ferdinando - Tecnologia Digital - Editora Atlas, 1992. 6. Szajnberg, Mordka, - Eletrônica Digital - Livros Técnicos e Científicos Editora Ltda, 1988 7. Tokhein, Roger L.. - Princípios Digitais - Editora Mc Graw-Hill Ltda, 1983. 8. Tocci, Ronald J. E Laskowski, Lester P. - Microprocessadores e Microcomputadores - Hardware e Software - Prentice/Hall do Brasil, 1987.

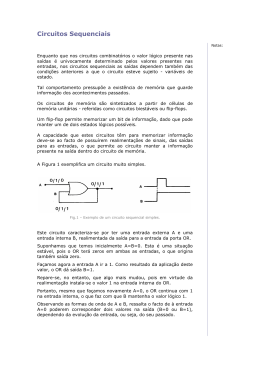

Baixar