Simplificação e Mapa de Karnaugh Sistemas digitais Agenda } Simplificação de circuitos lógicos } } Derivação de expressões } } Agrupamentos e simplificações Implicantes } } Soma de produtos X Produto da soma Mapa de Karnaugh (Mapa K) } } Álgebra booleana X mapa de Karnaugh Implicantes primo e implicante primo essencial Condições de irrelevância 2 Simplificação de circuitos lógicos } Os circuitos mostrados fornecem a mesma saída e, claramente, (b) é menos complexo que (a) } Colocar a expressão na forma SOP através da aplicação de teoremas booleanos e de DeMorgan 1) Achar a ex=ressão para a saída 2) Simplificar Circuitos lógicos podem ser simplificados com álgebra booleana e mapa de Kar7augh 3 Derivação de expressões } Soma de produtos (SOP) } } A expressão soma de produtos aparecerá como dois ou mais termos AND combinados com operações OR Produto de somas (POS) } A expressão produto de somas consiste de dois ou mais termos OR (soma) combinados com operações AND 4 Minitermos X Maxitermos } Minitermo (SOP) } } Variável com valor 0 é negada Maxitermo (POS) } Variável com valor 1 é negada A ex=ressão é fDnção da soma dos miniterFos de valor 1 A ex=ressão é fDnção da multiplicação dos maxiterFos de valor 0 5 Forma canônica X Alternativa } } Encontrar a equação p/ F descrita na tabela } Em soma de produtos (SOP) } Em produto de somas (POS) Representação alternativa } SOP } POS 6 Projetando circuitos lógicos combinacionais } Resolução de qualquer problema de lógica de projeto } } } } } Interprete o problema e defina sua tabela-verdade Escreva o termo AND para cada caso de saída = 1 Combine os termos na forma SOP Simplifique a expressão da saída, se possível Implemente o circuito para a expressão final, simplificada Tabela-‐verdade A saída deve ser alta somente quando a maioria das 3 entKadas for alta Ex=ressão SOP: Circuito Simplificado: 7 Método do mapa de Karnaugh (Mapa K) } Método gráfico para simplificar equações lógicas } } Converter tabelas-verdade no circuito lógico correspondente Pode ser usado para qualquer nº de variáveis de entrada } Porém sua utilidade prática é limitada a cinco ou seis variáveis Representação com duas variáveis m0 m1 m2 m3 Os valores da tabela-‐verdade são colocados no mapa K 8 Mapa K de quatro variáveis } Células adjacentes diferem em apenas uma variável, tanto na horizontal quanto na vertical } Uma expressão SOP pode ser obtida combinando todos os quadrados que contêm 1 m0 m1 m3 m2 m4 m5 m7 m6 m12 m13 m15 m14 m8 m9 m11 m10 9 Agrupamento de 1s (subcubos) } 1s adjacentes em dois, quatro ou oito quadrados podem ser agrupados para uma maior simplificação Só os terFos comuns (variáveis que não mudam o valor lógico) são colocados na ex=ressão final AgKDpamentos também podem ser realizados entKe superior, inferior e laterais 10 Simplificação com mapa K } Passos p/ simplificação da expressão com mapa K } Construir o mapa K com 1s indicado na tabela-verdade } } } } } Agrupar 1s não adjacentes a quaisquer outros 1s (1s isolados) Agrupar 1s que estão em pares Agrupar 1s em octetos, mesmo que já tenha sido agrupados Agrupar quartetos c/ um ou mais 1s e q ainda não estejam em grupos Agrupar qualquer pares necessários p/ incluir 1s ainda não agrupados Eliminar da ex=ressão final a variável que tKoca seu valor lógico dentKo do gKDpo GrDpo de quatKo (QuarXeto) GrDpo de oito (Octeto) 11 Simplificação: Exemplo SOP } Simplifique o mapa K e extraia a função por SOP 12 Simplificação: Exemplo POS } Simplifique o mapa K e extraia a função por POS 13 Implicantes } Implicantes } } Implicantes primos } } } Representa um termo de SOP e deve ser potência de 2 Grupo que contém maior nº possível de células adjacentes Transformar implicantes em primos, obtém maior minimização Implicante primo essencial } Se o implicante é coberto por único implicante primo 14 Implicantes: Exemplo1 } Verificar cada minitermo com 1 } Se for coberto só por único implicante primo, então este é implicante primo essencial 15 Implicantes: Exemplo2 16 Condições de irrelevância (don´t care-DC) } Condições sem efeito } } Existem certas condições de entrada que podem nunca ocorrer e para as quais não haja especificação de saída Projetista fica livre para assumir qualquer valor possível } Procurar produzir expressões com circuitos mais simplificado 𝑠(𝐴,𝐵,𝐶)=∑↑▒(5,6,7)+𝐷𝐶(3,4) 17 Prática! } Determinar a expressão mínima em para 𝑠0(𝐴,𝐵,𝐶,𝐷)=∑↑▒(0,1,2,5,6,7,13,15) 𝑠1(𝑊,𝑋,𝑌,𝑍)=∑↑▒(0,1,2,5,8,9,10) 𝑠2(𝐴,𝐵,𝐶,𝐷)=∏↑▒(1,2,3,6,7,8,9,12,14) 𝑠3(𝐴,𝐵,𝐶,𝐷)=∑↑▒(0,1,2,12,13)+𝐷𝐶(3,7,10,11,14,15) 𝑠4(𝐴,𝐵,𝐶,𝐷)=∑↑▒(0,3,5,6,7)+𝐷𝐶(10,11,12,13,14,15) 18 Resumo 19

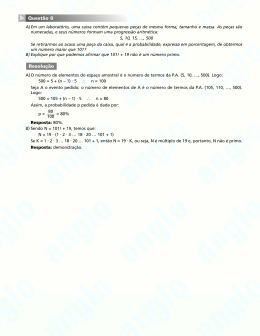

Baixar