Nota: ( ) Prova ( ) Prova Semestral (X) Exercícios ( ) Segunda Chamada ( ) Prova Modular ( ) Prova de Recuperação ( ) Prática de Laboratório ( ) Exame Final/Exame de Certificação ( ) Aproveitamento Extraordinário de Estudos Disciplina: EL-314 / EL-364 – Lista 6 – Proposição de Problemas Lógicos Turma: Professor: Ubiratan Ramos Data: ___ / ___ /20__ Aluno (a): 1) Desenvolver uma lógica que seja capaz de receber 4 entradas (A – MSB e D – LSB) binárias que variam de 0 a F e converta essas entradas para acender um display de 7 segmentos. Desenhar o circuito resultante em Digital Works: 2) Escrever os mintermos, a função canônica disjuntiva, simplificar e projetar o circuito lógico referente à tabela verdade abaixo: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 1 0 1 1 1 0 0 1 3) Projete um circuito lógico cuja saída seja nível ALTO apenas quando a maioria das entradas A, B e C forem nível ALTO. 4) Um chip 7486 contém quatro portas XOR, mostre como implementar uma porta XNOR usando apenas um chip 7486 com o menor número de portas possível. 5) Projete um circuito lógico cuja saída seja nível ALTO sempre que A e B forem ambas nível ALTO enquanto C e D estiverem ambas em nível BAIXO ou ambas em nível ALTO. 6) Uma fábrica precisa de uma sirene para indicar o fim do expediente. A sirene deve ser acionada quando ocorrer uma das seguintes condições: a) Já passou das 17h00 e todas as máquinas estão desligadas; b) É 6ª.-feira, a produção foi atingida e todas as máquinas estão desligadas. Projete um circuito lógico para controle da sirene. Utilize 4 variáveis de entrada: A será nível ALTO apenas quando forem 17h00 ou mais, B quando todas as máquinas estiverem paradas, C quando for 6ª.feira e D quando a produção for atingida. 7) Um número de 4 bits é representado como A0, A1, A2 e A3, onde A0 é o LSB (bit menos significativo) e A3 é o MSB (bit mais significativo). Projete um circuito lógico que gere um nível ALTO na saída sempre que o número binário for maior que 0010 e menor que 1000. RQ 0501 Rev. 14 Página 1 de 2 8) Um edifício possui uma cisterna no subsolo de onde é bombeada a água que vai para a caixa d'água no topo e desta para os apartamentos abaixo por gravidade. Sabendo que a caixa d'água possui um sensor de nível em sua borda superior que fecha quando a água ultrapassa determinado nível, gerando um “1” lógico, que a cisterna possui um outro sensor de nível em sua borda inferior (onde a bomba suga) que gera um “0” lógico quando a água cai abaixo de determinado nível, e que a bomba não pode funcionar a seco, projete um circuito digital que alimente a caixa d'água adequadamente. 9) Crie um circuito inversor controlável, ou seja, quando o sinal enable (habilita) estiver em "1", o circuito deve inverter a entrada. É possível construir este circuito usando apenas uma porta lógica? Se for, qual é esta porta? 10) Uma indústria possui um reservatório de líquido tal que este possa ser esgotado pelo fundo através de uma eletroválvula e enchido por cima através de outra eletroválvula. Existe um sensor de nível instalado na parte superior do reservatório que indica quando este está cheio e uma chave de duas posições usada para encher ou esvaziar o reservatório. Projete um circuito lógico que, baseado na leitura do sensor e da chave possa fazer o controle de enchimento e esgotamento do reservatório. 11) De posse de um contador binário (o funcionamento interno de um contador será explicado mais adiante) de 3 bits, faça um circuito lógico capaz de gerar a sequência de passo para um motor de passo com bobinas B3, B2, B1 e B0, funcionando em meio passo. A sequência de passo está na tabela a seguir: B3 B2 B1 B0 B0 0 0 0 1 0 0 1 1 0 0 1 0 0 1 1 0 0 1 0 0 B0 B3 B3 B2 B0 1 0 0 1 0 0 0 1 0 0 1 B1 B0 B1 B2 B0 B0 B3 B3 B1 B2 B1 B2 B3 B2 B3 B1 B2 B3 B0 B3 B1 1 B0 B1 B1 B2 B2 12) A figura que segue mostra quatro chaves que fazem parte do circuito de controle de uma máquina copiadora. As chaves estão posicionadas em diversos pontos ao longo da trajetória do papel dentro da máquina. Cada chave está no estado normal aberta e, quando o papel passa por uma chave, ela é fechada. É impossível o fechamento simultâneo das chaves SW1 e SW4. Projete um circuito lógico que gere uma saída em nível ALTO sempre que duas ou mais chaves estiverem fechadas ao mesmo tempo. Use o mapa V-K. ATENÇÃO! SW x fechada = “0”. RQ 0501 Rev. 10 Página 2 de 2

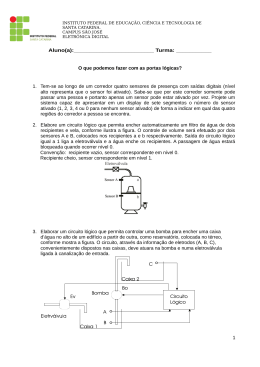

Baixar