UNIVERSIDADE POSITIVO NÚCLEO DE CIÊNCIAS EXATAS E TECNOLÒGICAS CURSO DE ENGENHARIA INDUSTRIAL ELÉTRICA BRUNO BOSTELMANN WILLIAN VERCHAI AVILLA SISTEMA DIDÁTICO PARA A SIMULAÇÃO DE FUNÇÕES DE TRANSFERÊNCIA ATÉ SEGUNDA ORDEM EM FPGA CURITIBA 2008 BRUNO BOSTELMANN WILLIAN VERCHAI AVILLA SISTEMA DIDÁTICO PARA A SIMULAÇÃO DE FUNÇÕES DE TRANSFERÊNCIA ATÉ SEGUNDA ORDEM EM FPGA Monografia apresentada ao Curso de Engenharia Elétrica da Universidade Positivo, a disciplina de Trabalho de Conclusão de Curso (TCC), sob a orientação do Prof. Roberto Selow. CURITIBA 2008 AGRADECIMENTOS Agradecemos primeiramente a Deus que nos permitiu chegar até aqui, aos nossos pais e familiares, que foram nossos maiores professores, e aos bons profissionais que nos apoiaram neste projeto. RESUMO Este trabalho tem como objetivo desenvolver um circuito eletrônico programável capaz de simular funções de transferência de segunda ordem pré-programadas em um FPGA, zelando por manter um baixo custo do projeto. Pretende-se utilizar este sistema na disciplina de Sistemas de Controle facilitando o aprendizado. O sistema apresenta um ambiente baseado em lógica reconfigurável, o que facilita a adaptação nas aplicações de problemas encontrados em automação e controle, também por ser um sistema aberto facilita com que futuras aplicações sejam desenvolvidas. Palavras chave - Sistema de Controle, VHDL, FPGA, Lógica Reconfigurável. ABSTRACT The main subjective of this material is the research of an electronic circuit to be programmed with similar function of transference of second order, pre-programmed in one FPGA, taking care with the low cost of project. The intention of the use of this system is at the Control Systems classes, helping on the learning. The system offers a based ambient in logical re-configuration, and this helps on the adaptation at the problems applications on automation and control. As an open system, can be used in future researched applications. Keywords - System of Control, VHDL, FPGA, Reconfigurable Logic. SUMÁRIO 1 INTRODUÇÃO ........................................................................................................................................ 10 PROBLEMA .......................................................................................................................................... 10 JUSTIFICATIVA............................................................................................................................... 11 OBJETIVO............................................................................................................................................. 11 2 REVISÃO DA LITERATURA ............................................................................................................... 12 3 ESPECIFICAÇÕES TÉCNICAS PRELIMINARES ........................................................................... 14 3.1 VISÃO GERAL DO PROJETO .................................................................................................................. 14 3.2 DESCRIÇÃO FUNCIONAL DOS BLOCOS.................................................................................................. 15 3.2.1 Bloco 1 – Conversor AD ............................................................................................................... 15 3.2.2 Bloco 2 – FPGA ............................................................................................................................ 16 3.2.3 Bloco 3 – Conversor DA ............................................................................................................... 17 3.2.4 Bloco 4 – Gerador de Clock........................................................................................................... 18 3.3 DIMENSIONAMENTO E MEMORIAL DE CÁLCULO .................................................................................. 19 3.3.1 Gráfico – Sobre amortecido, Sub amortecido e Criticamente Amortecido.................................... 19 3.4 PROGRAMAÇÃO................................................................................................................................... 20 3.4.1 Descrição geral .............................................................................................................................. 20 3.4.2 Fluxograma.................................................................................................................................... 21 3.4.3 Diagrama de blocos do FPGA ....................................................................................................... 21 3.4.4 Planejamento – Cronograma de implementação............................................................................ 22 4 METODOLOGIA .................................................................................................................................... 23 5 IMPLEMENTAÇÃO............................................................................................................................... 24 5.1 DESCRIÇÃO DA MONTAGEM ................................................................................................................ 24 5.1.1 Componentes do Protoboard.......................................................................................................... 25 5.1.2 Conexão do circuito com o FPGA................................................................................................. 26 5.2 TESTES, MEDIÇÕES E CONFIGURAÇÕES ................................................................................................ 28 5.2.1 Testes dos circuitos do protoboard................................................................................................ 28 5.2.2 Testes no software do FPGA ......................................................................................................... 29 5.3 CÓDIGO FONTE ................................................................................................................................... 31 5.4 CUSTOS DO PROJETO ........................................................................................................................... 31 6 RESULTADOS......................................................................................................................................... 33 6.1 SIMULAÇÕES DO SISTEMA PROPOSTO .................................................................................................. 33 7 CONCLUSÕES E RECOMENDAÇÕES PARA PROJETOS FUTUROS ........................................ 36 REFERÊNCIAS BIBLIOGRÁFICAS .............................................................................................................. 37 APÊNDICE A – FLUXOGRAMA DO SOFTWARE ....................................................................................... 38 APÊNDICE B – CRONOGRAMA .................................................................................................................... 39 APÊNDICE C – CÁLCULOS ............................................................................................................................ 40 Cálculo 1 – Sobre amortecido...................................................................................................................... 40 Calculo 2 – Sub amortecido......................................................................................................................... 41 Calculo 3 – Criticamente Amortecido ......................................................................................................... 42 APÊNDICE D – CÓDIGO FONTE ................................................................................................................... 44 1.1 1.2 1.3 LISTA DE FIGURAS Figura 1 - Ilustração do Sistema Proposto. .......................................................................... 11 Figura 2 – Diagrama de blocos do sistema. .......................................................................... 15 Figura 3 – Esquemático CI AD574AJN, configuração unipolar........................................ 16 Figura 4 – Cyclone II FPGA Starter Dev Kit Schematic.................................................... 17 Figura 5 – Esquemático CI AD7545. .................................................................................... 18 Figura 6 – Esquemático do sistema gerador de Clock......................................................... 19 Figura 7 – Circuito simulado no Matlab. ............................................................................. 20 Figura 8 – Diagrama em blocos do FPGA............................................................................ 21 Figura 9 – Mesa preparada para os testes............................................................................ 24 Figura 10 - Protoboard contendo diversos módulos............................................................. 25 Figura 11 - Expansion Header. .............................................................................................. 27 Figura 12 – Gráfico com os valores fornecidos pelo aplicativo Quartus II....................... 31 Figura 13 – Sinal de saída da função sobre amortecida...................................................... 33 Figura 14 – Sinal de saída da função sub amortecida......................................................... 34 Figura 15 – Sinal de saída da função criticamente amortecida.......................................... 34 Figura 16 – Fluxograma do software .................................................................................... 38 Figura 17 – Circuito simulado no Matlab. ........................................................................... 41 Figura 18 – Circuito simulado no Matlab. ........................................................................... 42 Figura 19 – Circuito simulado no Matlab. ........................................................................... 43 LISTA DE TABELAS Tabela 1 – Pinos utilizados no sistema.................................................................................. 27 Tabela 2 – Valores obtidos na saída do conversor AD........................................................ 28 Tabela 3 – Valores obtidos na saída do conversor DA........................................................ 29 Tabela 4 – Pinos utilizados no sistema.................................................................................. 29 Tabela 5 – Valores Obtidos na Simulação realizada no Quartus II. ................................. 30 Tabela 6 - Custo preliminar................................................................................................... 32 Tabela 7 – Valores Obtidos e Valores Convertidos. ............................................................ 40 Tabela 8 – Valores Obtidos e Valores Convertidos. ............................................................ 42 Tabela 9 – Valores Obtidos e Valores Convertidos. ............................................................ 43 LISTA DE SÍMBOLOS/ABREVIATURAS/SIGLAS ADC - Analog to Digital Converter ASIC - Circuito de Grande Densidade e Velocidade CPLDs - Dispositivos Lógicos Programáveis Complexos CMOS - Complementary Metal Oxide Semicondutor DAC - Digital to Analog Converter DSP - Digital Signal Processor EPROM - Erasable Programmable Read-Only Memory EEPROM - Electrically Erasable Programmable Read-Only Memory FPGA - Field Programmable Gate Array PMSM - Motor Síncrono à Ímã Permanente ROM - Read Only Memory SRAM - Static Random Access Memory VHDL - VHSIC Hardware Description Language VHSIC - Hardware Description Language IGBT - Insulated Gate Bipolar Transistor PWM - Pulse-width modulation PID – Proporcional – Integral – Derivativo USB - Universal Serial Bus I/O – Input/Output R/C – Read/Convert 10 1 INTRODUÇÃO Em busca de novas tecnologias que permitem a implementação de funções lógicas reprogramáveis por software, encontra-se a tecnologia denominada FPGA (Field Programmable Gate), que surgiu em 1983 após ser desenvolvida pela empresa Xilinx Inc. Nos FPGAs os circuitos programáveis são compostos de grupos de blocos lógicos organizados em forma de matriz, onde cada bloco tem uma capacidade computacional de implementar as funções lógicas e realizar um roteamento para que elas se comuniquem. Para realizar sua programação é utilizada a linguagem VHDL (VHSIC Hardware Description Language). Os dispositivos reconfiguráveis constituem uma ferramenta rápida e versátil para prototipagem de hardware no âmbito da indústria, para o desenvolvimento de novas soluções e o auxílio em tarefas computacionalmente intensivas na investigação e ainda para explorar e testar projetos no processo educativo, conforme ALMEIDA (2006). Este trabalho visa ajudar no processo educacional, fornecendo conhecimentos práticos durante o curso de graduação. Para isto foram utilizadas ferramentas modernas, em um ambiente que integra sistemas de controle com um ambiente de lógica reprogramável, onde será possível incrementar o aprendizado do curso de graduação de Engenharia Elétrica, através da aplicação de funções de transferência pré-definidas, onde o usuário pode variá-las e comparar seus resultados com simulações realizadas no software Matlab. 1.1 PROBLEMA Com a grande diversidade encontrada em sistemas de automação e controle, podem ser encontrados vários problemas, entre eles, é possível citar a grande diversidade dos projetos de automação e os custos elevados para o desenvolvimento dos mesmos. Existem sistemas que possuem hardware e software fechados, dificultando assim as alterações na programação. No ambiente acadêmico verificou-se uma deficiência na realização das simulações práticas na disciplina de Sistemas de Controle, sendo as simulações realizadas em plantas didáticas de elevado custo e através de softwares específicos. 11 1.2 JUSTIFICATIVA Procurando cobrir as necessidades acadêmicas em automação e controle, foi proposto um sistema envolvendo hardware e software que facilite o aprendizado da disciplina. Para isto foram utilizados recursos como os FPGA’s, permitindo assim um baixo custo e flexibilidade na reprogramação do sistema, essa facilidade de reconfiguração permite ao projetista fazer alterações mais rápidas no ambiente, o que reduz o tempo de programação, e diminui a probabilidade de acontecer algum dano no hardware, devido o excesso de contato físico no sistema. 1.3 OBJETIVO O objetivo do presente projeto de pesquisa é desenvolver um ambiente baseado em lógica reconfigurável, facilitando as adaptações nos problemas encontrados em automação e controle. O ambiente a ser desenvolvido possui um sistema aberto1, com isto será de fácil adaptação e de grande aproveitamento no ensino de Sistemas de Controle. O sistema é composto por um módulo de entrada ADC (Analog to Digital Converter), um FPGA e um conversor DAC (Digital to Analog Converter). O principal objetivo deste sistema é comparar o sinal de saída das funções de segunda ordem com resultados simulados no Quartus II e Matlab, verificando a taxa de erro que o sistema esta fornecendo. Figura 1 - Ilustração do Sistema Proposto. FONTE: Própria. 1 Sistema aberto: possibilita alteração parcial ou total do hardware e software assegurando ao usuário acesso irrestrito e sem custos adicionais ao seu código fonte. 12 2 REVISÃO DA LITERATURA Neste capítulo é apresentado uma revisão dos trabalhos relacionados com o projeto proposto. O objetivo é apresentar as abordagens que estendam as tecnologias desenvolvidas para Engenharia Elétrica, de uma forma específica para o desenvolvimento do projeto utilizando um FPGA. Uma ênfase maior é dada às abordagens voltadas para o desenvolvimento de sistemas didáticos baseados em lógica reconfigurável, dada a proximidade à proposta deste projeto. O artigo de MONMASSON (2007) apresenta uma análise do estado da arte do FPGA com uma concepção em aplicações industriais em sistemas de controle. Permite também uma abordagem funcional do ambiente industrial modelando os sistemas eletrônicos. Estas modelagens podem ser aplicadas também em telecomunicações, robótica, equipamentos hospitalares, automotivos e uma infinidade de aplicações que utilizem sistemas de controle. O objetivo principal do artigo é proporcionar uma visão global da utilização do FPGA em sistemas de controle industrial, a fim de conseguir uma elevada eficiência e qualidade em controles industriais permitindo assim uma rápida prototipagem de controladores digitais desenvolvidos em FPGA. Dentre alguns exemplos de aplicação dos FPGA’s em sistema de controle, o artigo de DUFOUR (2006) explica vários aspectos da concepção da modelagem de um motor síncrono (PMSM - Motor Síncrono a Ímã Permanente). De acordo com a técnica de representações de ponto fixo no sistema gerador Xilinx, foram realizadas as simulações no sistema PMSM e os resultados foram comparados com simulações realizadas no Simulink. Com isto foi possível verificar o funcionamento correto do motor PMSM antes de ser aplicado, junto com o controlador a um motor a combustão. O artigo de AW K.C (2007), apresenta um sistema didático desenvolvido para o curso de Engenharia Mecatrônica, o trabalho visa utilizar um FPGA associado a um software possibilitando assim simulações em sistemas de controle. O objetivo é proporcionar ao estudante uma grande variedade de experiências na implantação de sistemas de controle. Foi escolhido o FPGA, pois suporta implementações de circuitos lógicos facilitando assim o desenvolvimento do ambiente utilizado para as simulações contendo diagrama de estados, mapa de Karnaugh e equações booleanas. O FPGA também permite uma rápida prototipagem de sistemas digitais proporcionando ao estudante uma maior facilidade no aprendizado. 13 O artigo de NIU (2005) apresentado na universidade de Sheffiel tem por objetivo desenvolver um controlador PI programável, desenvolvido utilizando um FPGA. O objetivo do sistema é controlar a posição angular de um servomotor DC. Este trabalho foi desenvolvido através de um ciclo de controle atuando na velocidade do servomotor, juntamente com a posição desejada (Set Point). A função do FPGA é realizar o processo do controlador PI e enviar os resultados para o computador. O objetivo do trabalho é verificar se os FPGA’s possuem um desempenho suficiente para realizar aplicações personalizadas em controle digital. O artigo apresentado por LEISSHER (2002) na universidade de Bradley, tem por objetivo implantar um controlador PID (Proporcional – Integral – Derivativo) utilizando um FPGA para controlar a velocidade de um motor DC, assegurando assim a linearidade do sistema. Este controle é realizado através de um codificador instalado no subsistema do rotor do motor. Este codificador é responsável pela produção do sinal, cujo mesmo, emite uma freqüência que é diretamente relacionada à velocidade do rotor, com isto será possível verificar se a velocidade do motor está correta em relação à desejada. O artigo desenvolvido por LIMA (2006) apresenta um ambiente de apoio para o aprendizado de automação e controle utilizando lógica reconfigurável nos FPGA’s. Este ambiente visa atender a demanda encontrada no meio acadêmico, a aplicações industriais, utilizando um sistema aberto de fácil adaptação e com grande capacidade de processamento. O Sistema possui um controle de velocidade de um motor DC utilizando um controlador PID implementado dentro de um FPGA e ligado através de uma conexão USB (Universal Serial Bus) a um computador onde é feita a supervisão do sistema. Os resultados são comparados com resultados obtidos no Matlab. 14 3 3.1 ESPECIFICAÇÕES TÉCNICAS PRELIMINARES VISÃO GERAL DO PROJETO Para o desenvolvimento do sistema proposto, foi utilizado um hardware composto por um módulo de entrada ADC, que realiza a conversão de analógico para digital, o sinal de saída é transmitido para o FPGA. A programação foi realizada em VHDL, onde foram programadas as três funções propostas, sendo elas: uma sub amortecida, uma sobre amortecida e uma criticamente amortecida. Estas funções serão selecionadas através do switch que o próprio kit DE1 desenvolvido pela ALTERA possui. Conforme já descrito, a programação foi realizada em VHDL, que suporta projetos com múltiplos níveis de hierarquia, permitindo que o projeto seja modificado para futuras aplicações. Após a seleção da função através do switch, o sinal de entrada é manipulado e enviado para um conversor DAC que realiza a conversão de digital para analógico. O sinal de saída foi capturado e analisado em um osciloscópio, os resultados obtidos foram comparados com os gráficos simulados no Matlab. É possível verificar na Figura 2 o diagrama de blocos do sistema proposto. De acordo com o projeto proposto foram definidos os componentes e circuitos que melhor atendiam os objetivos deste trabalho, e a partir das definições foram elaborados os circuitos descritos na seqüência em forma de blocos. 15 Figura 2 – Diagrama de blocos do sistema. FONTE: Própria. 3.2 DESCRIÇÃO FUNCIONAL DOS BLOCOS Os blocos funcionam em conjunto interagindo e comunicando-se entre si, de modo que o sistema possa executar todas as funções para qual ele foi projetado. 3.2.1 Bloco 1 – Conversor AD Para realizar a conversão do sinal de entrada de analógico para digital, foi utilizado o CI AD574AJN, este CI foi escolhido porque possui uma resolução de 12 bits, com isto a a- 16 mostragem é mais precisa. Este conversor contém um clock e tensão de referência interna, com isto garante uma alta precisão e a sua comunicação é em paralelo, facilitando assim a integração do sistema. Este CI possui dois tipos de configuração, sendo uma unipolar e outra bipolar. Para o trabalho proposto foi utilizada a configuração unipolar que atende o objetivo do projeto. A figura 3 mostra o esquemático do conversor. Figura 3 – Esquemático CI AD574AJN, configuração unipolar. FONTE: www.alldatasheet.com. 3.2.2 Bloco 2 – FPGA Para realizar o tratamento do sinal digital enviado pelo conversor AD, foi utilizado o kit didático Cyclone II FPGA Starter Dev KIT Schematic DE1, desenvolvido pela ALTERA. As vantagens desse kit com relação ao presente projeto são descritas abaixo: - Possui 10 swicthes, onde três deles foram utilizados para a seleção de cada função e outro deles, para a função reset; - Contém duas expansões de 40 pinos, sendo que desses 80 pinos 64 são de I/O (Input/Output) e 16 de VCC ou GND. Uma das expansões foi utilizada como entrada e a outra como saída; 17 - Possui um FPGA – EP2C20N com 20.000 blocos lógicos, sendo utilizados 10.739 destes, para implementar a programação do ambiente proposto. O kit recebe os valores digitais enviados pelo conversor AD, estes valores serão simulados no FPGA através das funções pré-definidas, e o resultado desta simulação é enviado para o conversor DA, que será explicado no próximo bloco. A Figura 06 representa uma foto demonstrativa do Kit. Figura 4 – Cyclone II FPGA Starter Dev Kit Schematic. FONTE: www.altera.com. 3.2.3 Bloco 3 – Conversor DA Para o conversor DA foi utilizado o circuito integrado AD7545, este CI é responsável pela conversão dos dados simulados no FPGA de digital para analógico. Será utilizado este CI, pois apresenta uma resolução de 12 bits, com isto será possível obter uma taxa de amostragem mais precisa e igual ao conversor AD. Apresenta uma interface paralela, facilitando a 18 comunicação com a saída da placa DE1 da ALTERA. Este CI possui também dois tipos de configuração, sendo uma unipolar e outra bipolar. Utilizou-se a configuração unipolar, pois atende o objetivo do projeto. Após as conversões, os resultados foram analisados em um osciloscópio. Na Figura 05, encontra-se o esquemático do CI. Figura 5 – Esquemático CI AD7545. FONTE: www.alldatasheet.com. 3.2.4 Bloco 4 – Gerador de Clock O circuito gerador de Clock foi desenvolvido utilizando o CI 555, que possui dois modos de operação: monoestável (possui um estado estável) e astável (não possui estado estável). Foi utilizado o modo monoestável que não realiza oscilações no sistema. Após a montagem do sistema ilustrado na figura 6, foi possível selecionar a freqüência desejada, pois o sistema oferece freqüências de 1 Hz, 10 Hz, 100 Hz e 1 kHz. A freqüência que melhor atendeu o funcionamento do sistema foi a de 10 Hz. 19 Figura 6 – Esquemático do sistema gerador de Clock. FONTE: www.ee.pucrs.br/~denis/Sistemas%20Digitais%20I/Placa_Clock.pdf. 3.3 DIMENSIONAMENTO E MEMORIAL DE CÁLCULO De acordo com o projeto proposto foram elaborados os cálculos que melhor atendiam os objetivos do projeto, e a partir das definições, os cálculos foram elaborados e utilizados nas simulações. Estes cálculos foram realizados com o auxilio do livro de Engenharia de Controle escrito por BOLTON (1995). Para realizar a transformada Z das funções de segunda ordem, onde se converte uma FT(s) em FT(z), foi utilizado o software Matlab. Os resultados obtidos e o código utilizado para realizar a transformada Z podem ser verificados no apêndice “C”. 3.3.1 Gráfico – Sobre amortecido, Sub amortecido e Criticamente Amortecido Foi utilizado o software Matlab para gerar os gráficos utilizados como referência para a comparação dos resultados obtidos no ambiente proposto. Conforme a figura 07 é possível verificar os sinais de saída de cada função, onde: • Sub amortecido em azul; • Criticamente amortecido em amarelo; • Sobre amortecido em rosa. 20 Figura 7 – Circuito simulado no Matlab. Sub amortecido Criticamente amortecido Sobre amortecido FONTE: Própria. 3.4 3.4.1 PROGRAMAÇÃO Descrição geral Foi utilizada a linguagem VHDL para realizar a programação no FPGA. Para realização da programação e simulações do sistema, foi utilizado o software Quartus II desenvolvido pela empresa ALTERA. O VHDL que suporta projetos com múltiplos níveis de hierarquia, e sua descrição pode consistir na interligação de outras descrições menores a um código que representa o comportamento esperado do circuito (D’AMORE, 2005). Esses estilos são denominados: estrutural e comportamental, e podem ser mesclados em uma mesma descrição. A estrutura hierárquica e a opção de combinar diversos estilos de descrição facilitam a condução de projetos complexos, que partem de um nível mais elevado para um nível mais baixo de especificação, conhecidos como top down disign (BIZ, 2007). 21 3.4.2 Fluxograma Para um melhor entendimento do sistema proposto foi elaborado um fluxograma onde fosse possível representar o diagrama esquemático do processo. Encontra-se no apêndice “A” o fluxograma necessário para a execução do processo de programação no FPGA. 3.4.3 Diagrama de blocos do FPGA Foi utilizado o software Quartus II para realizar a programação no FPGA. Representado na figura 8, verifica-se o diagrama de blocos desenvolvido para atender o ambiente proposto. Através deste sistema, foi possível realizar as devidas simulações no ambiente antes de unificar o software desenvolvido ao hardware. Figura 8 – Diagrama em blocos do FPGA. FONTE: Própria. 22 3.4.4 Planejamento – Cronograma de implementação Com base no cronograma geral proposto no manual do TCC 2008, e seguindo as necessidades de tempo para execução de determinadas fases do projeto, foi estabelecido o cronograma detalhado, conforme apêndice “B”. 23 4 METODOLOGIA A realização deste trabalho se deu através dos seguintes métodos de pesquisa: 1) Levantamento de natureza exploratória através da internet a respeito das programações em VHDL; 2) Pesquisa bibliográfica em trabalhos científicos (IEC, IEEE) que apresentam informações relacionadas ao tema; 3) Estudo dos manuais do kit ALTERA DE1 utilizado; 4) Aplicação do conhecimento adquirido a fim de propor e montar o sistema no laboratório de pesquisas, utilizando instrumentos e equipamentos disponíveis na Universidade Positivo. Esta estratégia metodológica dá a conotação principal deste trabalho, o qual se trata de uma pesquisa aplicada2. 5) Realização de ensaios e testes em bancada, objetivando coletar dados do sistema e compará-los com resultados obtidos em simulações realizadas no Matlab. 2 Pesquisas aplicadas são as que se destinam a aplicar leis, teorias e modelos, na solução de problemas que exigem ação e/ou diagnóstico de uma realidade. 24 5 5.1 IMPLEMENTAÇÃO DESCRIÇÃO DA MONTAGEM Depois de concluída a fase do detalhamento técnico, onde foram definidos os componentes utilizados no sistema didático e os esquemas elétricos através dos datashheets, iniciouse a implantação do sistema e a realização de simulações para verificação do software desenvolvido no Quartus II. Para começar a implementação do sistema, foram realizados diversos testes em protoboard e no software desenvolvido, utilizando o kit DE1 da ALTERA. Nos testes realizados, verificou-se que os componentes escolhidos atenderam perfeitamente o objetivo do projeto, com resultados precisos e satisfatórios. O kit DE1 com o FPGA EP2C20N contendo 20.000 elementos lógicos supriu perfeitamente as células lógicas utilizadas na programação. Após a montagem do ambiente foram realizadas algumas alterações no software para uma melhor funcionalidade do sistema. No hardware foi ajustado o clock de 10 Hz, com isto foi possível obter-se uma melhor visualização através do osciloscópio. Na Figura 9, encontra-se a mesa com o kit DE1, o protoboard e o osciloscópio, onde foram realizados os testes. Figura 9 – Mesa preparada para os testes. FONTE: Própria. 25 5.1.1 Componentes do Protoboard Para realizar os testes dos componentes utilizados, foram montados em protoboard os circuitos e divididos em três blocos conforme mostra a Figura 10, facilitando os testes individuais de cada circuito: • Bloco A – Conversor AD574AJN, de 12 bits, que realiza a conversão do sinal analógico para digital, onde o sinal de saída é enviado para o FPGA; • Bloco B – Gerador de Clock, através do LM555, foi possível desenvolver um gerador de clock que pode variar a freqüência entre 1Hz a 1kHz, sendo utilizada pelo sistema a de 10 Hz - este sinal é enviado para o kit DE1; • Bloco C – Conversor AD7545, de 12 bits, que realiza a conversão do sinal digital recebido do FPGA para analógico, sendo que o resultado de saída é captado pelo osciloscópio. Figura 10 - Protoboard contendo diversos módulos. FONTE: Própria. O bloco “A” foi o primeiro circuito montado no protoboard, e foi utilizado datasheet do componente AD574AJN para auxiliar nas interligações. Utilizou-se a configuração unipo- 26 lar padrão para 12 bits. A entrada do sinal analógico no sistema foi realizada através do pino 14 do conversor. Esta entrada pode variar de 0 a 20 V. O pino 4 é ligado a um switch, o mesmo tem a funcionalidade de converter o sinal de entrada de analógico para digital. O pino 1 do switch foi utilizado para habilitar o pino R/C (Read/Convert), correspondente ao pino 5 do conversor AD. Quando este pino está em nível lógico baixo, realiza a conversão do sinal, e quando encontra-se em nível lógico alto, envia o valor convertido para a saída. Para o bloco “B”, foi utilizado o esquemático apresentado no capítulo 3.2.4, juntamente com o datasheet do componente LM555. Depois da implantação do circuito foram realizados os testes para verificar qual a melhor freqüência para o sistema. Selecionando o pino 2 do switch utilizado no Gerador de Clock. A freqüência de 10 Hz é selecionada porque é a que melhor atende o sistema desenvolvido. Por último foi montado o bloco “C” no protoboard, utilizando o datasheet do componente AD7545, onde foi possível realizar a configuração unipolar do conversor. Após concluir toda a instalação do circuito e a verificação do funcionamento do sistema, foi possível enviar o sinal digital do FPGA para o conversor, com isto, este sinal foi convertido para analógico podendo assim ser capturado pelo osciloscópio e facilitando nas comparações de resultados. 5.1.2 Conexão do circuito com o FPGA Através do manual do kit DE1, foi possível realizar a ligação do circuito elaborado em protoboard com o kit DE1, foi utilizado nesta ligação os Expansion Header do Kit DE1, para realizar a comunicação entre os sistemas. A Figura 11 detalha os dois conectores de 40 pinos utilizados na entrada e saída do FPGA. A partir dos dados da figura 11 foi possível desenvolver a Tabela 1, onde foi utilizado o conector JP1 para as entradas dos dados no FPGA, e o conector JP2 para as saídas dos dados e a entrada do clock externo no FPGA. 27 Figura 11 - Expansion Header. FONTE: www.altera.com. Tabela 1 – Pinos utilizados no sistema. Pino do conversor AD 16 17 18 19 20 21 22 23 24 25 26 27 Pino do conversor DA 15 14 13 12 11 10 9 8 7 6 5 4 Pino do LM555 3 FONTE: Própria. Descrição do pino DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB10 DB11 Descrição do pino DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB10 DB11 Descrição do pino Q Pino do conector (JP1) IO_A0 IO_A2 IO_A4 IO_A6 IO_A8 IO_A10 IO_A12 IO_A14 IO_A16 IO_A18 IO_A20 IO_A22 Pino do conector (JP2) IO_B22 IO_B20 IO_B18 IO_B16 IO_B14 IO_B12 IO_B10 IO_B8 IO_B6 IO_B4 IO_B2 IO_B0 Pino do conector (JP2) IO_B24 Número do pino na FPGA PIN_A13 PIN_A14 PIN_A15 PIN_A16 PIN_A17 PIN_A18 PIN_A19 PIN_A20 PIN_C21 PIN_D21 PIN_E21 PIN_F21 Número do pino na FPGA PIN_E19 PIN_E20 PIN_D19 PIN_C19 PIN_C17 PIN_D15 PIN_C14 PIN_F12 PIN_F15 PIN_E14 PIN_H14 PIN_H12 Número do pino na FPGA PIN_G20 28 5.2 5.2.1 TESTES, MEDIÇÕES E CONFIGURAÇÕES Testes dos circuitos do protoboard Para iniciar a fase de testes, os três circuitos do protoboard foram divididos em circuitos independentes, o que facilitou os testes individuais e a verificação de erros para possíveis correções. O primeiro teste foi realizado no conversor AD, com 12 leds ligados em seus pinos de saída, com isto, foi possível verificar o funcionamento correto do conversor. Foi desenvolvida a Tabela 2 para comparar os valores obtidos com os esperados. Tabela 2 – Valores obtidos na saída do conversor AD. Valor de entrada (Volts) 20V 10V 5V 0V FONTE: Própria. Valor de saída (Decimal) 4096 2048 1024 0 Valor de saída (Binário) 111111111111 100000000000 010000000000 000000000000 Os testes no conversor AD foram realizados com uma tensão de 5 V aplicada na entrada do conversor, que correspondente a ¼ do valor máximo de entrada. O resultado obtido na saída foi satisfatório, pois somente o 2° led mais significativo ficou aceso. O segundo teste foi realizado no circuito responsável pela geração do clock, que também apresentou um excelente resultado, já que sua freqüência de saída apresentou um valor de 9,8 Hz analisado por um osciloscópio. Esse valor foi muito próximo aos 10 Hz esperados. O último teste de photoboard foi realizado no convesor DA, onde foram alterados os valores de entrada do conversor para o nível lógico alto ou baixo, com isto foi possível verificar a tensão de saída do conversor. Para comparar os valores obtidos com os valores esperados, foi desenvolvida a Tabela 3, tendo como base o valor de referência de 5 V, que é o mesmo valor de entrada do conversor AD. Nestes testes foram encontradas algumas variações de tensão na saída do circuito, que podem ser verificadas na tabela a seguir. 29 Tabela 3 – Valores obtidos na saída do conversor DA. Valor de entrada (Binário) Valor de saída (Decimal) 111111111111 100000000000 010000000000 000000000000 FONTE: Própria. 5.2.2 4096 2048 1024 0 Valor de saída esperado (Volts) -5V -2,5V -1,25V 0V Valor de saída obtido (Volts) -4,95V -2,4V -1,1V 0V Testes no software do FPGA Para testar o software desenvolvido no FPGA, foi utilizado o programa Quartus II da ALTERA. Onde, primeiramente, foram testadas as três funções de transferência em blocos separados, facilitando a programação. Após a unificação dos três blocos referentes às funções de transferência, foram criados dois novos blocos de programação, que funcionam simplesmente para mandar o valor da função selecionada para a saída. Podem-se verificar na Tabela 1 os pinos utilizados para a entrada e saída do sistema desenvolvido com o FPGA. A Tabela 4 refere-se aos switches utilizados do kit DE1 para selecionar as funções e o switch utilizado para o reset do sistema. Tabela 4 – Pinos utilizados no sistema. Switch utilizado no kit SW[9] SW[8] SW[7] SW[6] FONTE: Própria. Função do switch Selecionar a função de transferência sobre amortecida Selecionar a função de transferência sub amortecida Selecionar a função de transferência criticamente amortecida Reset do programa desenvolvido Número do pino na FPGA PIN_L2 PIN_M1 PIN_M2 PIN_U11 Com todos os pinos configurados e a programação concluída, foi possível desenvolver a Tabela 5, através das simulações realizadas no Wafeform do Quartus II. Para isso, foi utili- 30 zado um valor de entrada em binário 001111101000, e um clock de 10 ms, com um tempo máximo de 100 ms, variando os switches para acionar a função desejada. Tabela 5 – Valores Obtidos na Simulação realizada no Quartus II. Sobre amor- Sub amortetecido cido 0 0 33 41 102 151 182 309 262 494 337 686 406 868 468 1027 523 1154 618 1245 659 1299 695 1318 727 1307 755 1272 780 1220 803 1159 823 1096 841 1036 857 983 872 940 885 909 896 890 906 882 915 884 923 894 FONTE: Própria. Criticamente Amortecido 0 36 119 223 331 434 528 610 681 741 791 832 865 891 912 929 942 953 962 968 973 976 979 981 982 Sobre amortecido 930 936 941 946 951 955 959 962 965 967 969 971 973 975 977 978 979 980 981 982 983 984 985 985 985 Sub amortecido 910 930 951 971 989 1004 1015 1023 1027 1024 1019 1013 1006 999 993 988 985 987 989 990 991 992 993 993 993 Criticamente Amortecido 983 984 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 985 Com esses valores foi possível gerar o gráfico da Figura 12, que quando comparado com os resultados simulados no Matlab (Figura 7), apresenta 100% de precisão. 31 Figura 12 – Gráfico com os valores fornecidos pelo aplicativo Quartus II. 1400 1200 1000 Sobre amortecido 800 Sub amortecido 600 Criticamente Amortecido 400 200 0 1 8 15 22 29 36 43 50 57 64 71 78 85 92 99 FONTE: Própria. 5.3 Código Fonte A programação realizada no software Quartus II pode ser vista no apêndice “D”. 5.4 Custos do Projeto Os componentes utilizados no projeto foram escolhidos mediante pesquisa no mercado de componentes (Curitiba e São Paulo) e em sites especializados na venda de componentes eletrônicos. O estudo preliminar de custos apontou para a situação baseada nos componentes pré-determinados, encontrada na tabela 6. 32 Tabela 6 - Custo preliminar. Material Conversor AD Conversor DA Componentes diversos Total FONTE: Própria. Custo total R$ 55,00 R$ 56,00 R$ 200,00 R$ 311,00 33 6 6.1 RESULTADOS SIMULAÇÕES DO SISTEMA PROPOSTO Após a realização de todos os testes no protoboard e no software Quartus II da ALTERA, foi possível realizar a interligação dos sistemas. Foram utilizados dois flats cables, um utilizado para enviar os dados para o FPGA e outro para enviar o resultado para o conversor DA, sendo seu valor de saída capturado por um osciloscópio. Verificou-se que os resultados obtidos estavam de acordo com os propostos. Os resultados obtidos foram impressos da seguinte forma: • Figura 13 - Função sobre amortecida, • Figura 14 - Função sub amortecida, • Figura 15 - Função criticamente amortecida. Figura 13 – Sinal de saída da função sobre amortecida. FONTE: Própria. 34 Figura 14 – Sinal de saída da função sub amortecida. FONTE: Própria. Figura 15 – Sinal de saída da função criticamente amortecida. FONTE: Própria. 35 Através destes três gráficos é possível verificar que a forma de onda obtida é exatamente igual à esperada. Quanto ao valor de tensão obtido, percebe-se um valor um pouco abaixo do esperado nas três funções, o que foi causado pelo conversor DA que apresentou um valor de tensão um pouco abaixo do esperado, refletindo no resultado final do sistema. 36 7 CONCLUSÕES E RECOMENDAÇÕES PARA PROJETOS FUTUROS Com o presente trabalho foram obtidos os resultados gerados pelo FPGA e comparados com os valores simulados no Matlab. Utilizando a programação em VHDL foi possível realizar as alterações nos blocos lógicos com grande facilidade, podendo ser implantadas novas funções no sistema através de novos blocos. Os resultados obtidos nas simulações do ambiente foram satisfatórios devido à alta velocidade de operação do FPGA. Como o intuito principal do projeto é apoiar o ensino de Sistemas de Controle do curso de Engenharia Elétrica da Universidade Positivo, citam-se abaixo as principais ferramentas que este ambiente desenvolvido pode proporcionar: • Simulações de automação de controle – Com este sistema pode-se realizar testes com funções de segunda ordem, e verificar seus resultados de uma forma mais prática do que a utilizada atualmente na disciplina; • Capacidade dos FPGA´s – Como o FPGA utilizado possuiu 20.000 elementos lógicos, e para o desenvolvimento do projeto foram utilizados 10.739, novos blocos podem ser facilmente inseridos, sem haver a necessidade de excluir os atuais; • Lógica reconfigurável – Permite que os alunos do curso de graduação possam acessar o ambiente aberto do projeto, e modificar seus blocos internos, facilitando com que futuras aplicações possam ser implantadas; • Facilidade de expansão – Como o kit DE1 possui 72 pinos de entrada e saída, sendo utilizados 33 deles para o desenvolvimento do ambiente proposto, é possível implementar novos recursos para o sistema. 37 REFERÊNCIAS BIBLIOGRÁFICAS MONMASSON, Eric. FPGA Design Methodology for Industrial Control Systems - A Re- view. 2007. CHRISTIAN DUFOUR, Christian. Real-Time Simulation of Permanent Magnet Motor Drive on FPGA Chip for High-Bandwidth Controller Tests and Validation. Montréal, Québec, Canada, 2006. K. C., Aw. A FPGA-based rapid prototyping approach for teaching of Mechatronics Engineering. University of Auckland, New Zealand, 2007. NIU, Jianyong. Prototyping A DC Motor PI Controller Using Field Programmable Gate Arrays. University of Sheffield, England. 2005. LEISHER, Paul. FPGA Implementation of a PID Controller with DC Motor Application. Bradley University, 2002. LIMA, Carlos. Ambiente para apoio ao aprendizado de automação e controle baseado em lógica reconfigurável. UTFPR, 2006. D’AMORE, Roberto. VHDL – Descrição e síntese de circuitos digitais. 2005. BOLTON, W. Engenharia de Controle. 1995. ALMEIDA, Manuel. Ferramentas práticas de baixo custo para desenvolvimento de sistemas baseados em FPGA’s. Universidade de Aveiro, Santiago, 2006. BIZ, Cristina. Planta de Elevadores com controle por FPGA’s. Universidade Positivo, Curitiba, 2007. Internet: ALTERA. Disponível em http://www.altera.com. Acesso em 28 agosto. 2008 ALLDATASHEET. Disponível em http://www.alldatasheet.com. Acesso em 17 jullho. 2008 PUC-RS. Disponível em www.ee.pucrs.br/~denis/Sistemas/20Digitais/20I/Placa_Clock.pdf. Acesso em 20 agosto. 2008 FSFLA. Disponível em http://www.fsfla.org/pipermail/legales/2006-May/000032.html. Acesso em 24/10/2008. 38 APÊNDICE A – FLUXOGRAMA DO SOFTWARE Figura 16 – Fluxograma do software FONTE: Própria. 39 APÊNDICE B – CRONOGRAMA Observação: Não haverá divisões de tarefas, as mesmas serão executadas sempre em conjunto pelos integrantes da equipe, exceto para o desenvolvimento da monografia. 40 APÊNDICE C – CÁLCULOS Cálculo 1 – Sobre amortecido G ( s) = 9 s + 9s + 9 2 Equação 1 – Sobre amortecido Através dos comandos abaixo foi possível realizar a transformada Z da função sobre amortecido no software Matlab. Num = [9]; den = [1 9 9 ]; Sys = tf(num,den); [sysd] = c2d(sys,0.001) Foi utilizado o tempo de amostragem (0,1) θº = 0,03382z + 0,02508 / z2 V z2 -1,348z + 0,4066 / z2 θº = 0,03382z-1 + 0,02508z-2 V 1 -1,348z-1 + 0,4066z-2 θº [K] = 0,03382 V[K-1] + 0,02508 V[K-2] + 1,348 V[K-1] - 0,4066 V[K-2] (θº [K] = 0,03382 V[K-1] + 0,02508 V[K-2] + 1,348 V[K-1] - 0,4066 V[K-2]) *4464 4464*θº [K] = 151 V[K-1] + 112 V[K-2] + 6018V[K-1] - 1815 V[K-2] θº [K] = 151 V[K-1] + 112 V[K-2] + 6018 V[K-1] - 1815 V[K-2] – 4463 θº [K] Tabela 7 – Valores Obtidos e Valores Convertidos. FONTE: Própria. VALORES OBTIDOS VALORES CONVERTIDOS b = 0,03382 1 b = 0,02508 2 a = 1,348 1 a = 0,4006 2 151 = 0 x 0097h 112 = 0 x 0070h 6018 = 0 x 1782h 1815 = 0 x 0717h 41 Figura 17 – Circuito simulado no Matlab. FONTE: Própria. Calculo 2 – Sub amortecido G (s) = 9 s + 2s + 9 2 Equação 2 – Sub amortecido Através dos comandos abaixo foi possível realizar a transformada Z da função sub amortecido no software Matlab. Num = [9]; den = [1 2 9 ]; Sys = tf(num,den); [sysd] = c2d(sys,0.001) Foi utilizado o tempo de amostragem (0,1) θº = 0,04183z + 0,03913 / z2 V z2 -1,738z + 0,8187 / z2 θº = 0,04183z-1 + 0,03913z-2 V 1 -1,738z-1 + 0,8187z-2 θº [K] = 0,04183 V[K-1] + 0,03913 V[K-2] + 1,738 V[K-1] - 0,8187 V[K-2] (θº [K] = 0,03382 V[K-1] + 0,02508 V[K-2] + 1,348 V[K-1] - 0,4066 V[K-2]) *3610 3610*θº [K] = 151 V[K-1] + 141 V[K-2] + 6274V[K-1] - 2955 V[K-2] θº [K] = 151 V[K-1] + 141 V[K-2] + 6274 V[K-1] - 2955 V[K-2] – 3609 θº [K] 42 Tabela 8 – Valores Obtidos e Valores Convertidos. VALORES OBTIDOS VALORES CONVERTIDOS b = 0,04183 1 b = 0,03913 2 a = 1,738 1 a = 0,8187 2 151 = 0 x 0097h 141 = 0 x 008Dh 6274 = 0 x 1882h 2955 = 0 x 0B8Bh FONTE: Própria. Figura 18 – Circuito simulado no Matlab. FONTE: Própria. Calculo 3 – Criticamente Amortecido G ( s) = 9 s + 6s + 9 2 Equação 3 – Criticamente amortecido Através dos comandos abaixo foi possível realizar a transformada Z da função sub amortecido no software Matlab. Num = [9]; den = [1 6 9 ]; Sys = tf(num,den); [sysd] = c2d(sys,0.001) Foi utilizado o tempo de amostragem (0,1) θº = 0,03694z + 0,03024 / z2 V z2 -1,482z + 0,5488 / z2 θº = 0,03694z-1 + 0,03024z-2 43 V 1 -1,482z-1 + 0,5488z-2 θº [K] = 0,03694 V[K-1] + 0,03924 V[K-2] + 1,482 V[K-1] - 0,5488 V[K-2] (θº [K] = 0,03694 V[K-1] + 0,3924 V[K-2] + 1,482 V[K-1] - 0,5488 V[K-2]) *4087 4087*θº [K] = 151 V[K-1] + 124 V[K-2] + 6059V[K-1] - 2244 V[K-2] θº [K] = 151 V[K-1] + 124 V[K-2] + 6059 V[K-1] - 2244 V[K-2] – 4086 θº [K] Tabela 9 – Valores Obtidos e Valores Convertidos. VALORES OBTIDOS b = 0,03694 1 b = 0,03024 2 a = 1,482 1 a = 0,8187 2 FONTE: Própria. Figura 19 – Circuito simulado no Matlab. FONTE: Própria. VALORES CONVERTIDOS 151 = 0 x 0097h 141 = 0 x 007Ch 6274 = 0 x 17ABh 2955 = 0 x 08C4h 44 APÊNDICE D – CÓDIGO FONTE Programação realizada para o bloco da função sobre amortecido. LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.STD_LOGIC_UNSIGNED.all; ENTITY proj1 IS PORT ( V1 clock reset switch1 S1 ); END proj1; ARCHITECTURE logica of proj1 is SIGNAL C1 : SIGNAL C3 : SIGNAL C5 : SIGNAL C7 : SIGNAL R1 : SIGNAL R2 : SIGNAL R3 : SIGNAL R4 : : IN : IN : IN : IN : BUFFER INTEGER RANGE 0 TO 4095; STD_LOGIC := '0'; STD_LOGIC := '0'; STD_LOGIC := '0'; INTEGER RANGE 0 TO 4095 INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; BEGIN PROCESS (clock, reset, switch1) VARIABLE D1 : INTEGER; BEGIN IF (reset='1') or (switch1='0') THEN D1 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D1 := V1; END IF; C1 <= D1; END PROCESS; PROCESS (clock, reset, switch1) VARIABLE D2 : INTEGER; BEGIN IF (reset='1') or (switch1='0') THEN D2 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D2 := C1; 45 END IF; C3 <= D2; END PROCESS; PROCESS (clock, reset, switch1) VARIABLE D3 : INTEGER; BEGIN IF (reset='1') or (switch1='0') THEN D3 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D3 := S1; END IF; C5 <= D3; END PROCESS; PROCESS (clock, reset, switch1) VARIABLE D4 : INTEGER; BEGIN IF (reset='1') or (switch1='0') THEN D4 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D4 := C5; END IF; C7 <= D4; END PROCESS; R1<=(338*C1/10000); R2<=(251*C3/10000); R3<=(13480*C5/10000); R4<=(-4066*C7/10000); S1<=R1+R2+R3+R4; END logica; Programação realizada para o bloco da função sub amortecido LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.STD_LOGIC_UNSIGNED.all; ENTITY proj2 IS PORT ( V1 clock reset switch2 S2 ); END proj2; ARCHITECTURE logica of proj2 is : IN : IN : IN : IN : BUFFER INTEGER RANGE 0 TO 4095; STD_LOGIC := '0'; STD_LOGIC := '0'; STD_LOGIC := '0'; INTEGER RANGE 0 TO 4095 46 SIGNAL SIGNAL SIGNAL SIGNAL SIGNAL SIGNAL SIGNAL SIGNAL C1 : C3 : C5 : C7 : R1 : R2 : R3 : R4 : INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; BEGIN PROCESS (clock, reset, switch2) VARIABLE D1 : INTEGER; BEGIN IF (reset='1') or (switch2='0') THEN D1 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D1 := V1; END IF; C1 <= D1; END PROCESS; PROCESS (clock, reset, switch2) VARIABLE D2 : INTEGER; BEGIN IF (reset='1') or (switch2='0') THEN D2 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D2 := C1; END IF; C3 <= D2; END PROCESS; PROCESS (clock, reset, switch2) VARIABLE D3 : INTEGER; BEGIN IF (reset='1') or (switch2='0') THEN D3 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D3 := S2; END IF; C5 <= D3; END PROCESS; PROCESS (clock, reset, switch2) VARIABLE D4 : INTEGER; BEGIN IF (reset='1') or (switch2='0') THEN D4 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D4 := C5; 47 END IF; C7 <= D4; END PROCESS; R1<=(418*C1/10000); R2<=(391*C3/10000); R3<=(17380*C5/10000); R4<=(-8187*C7/10000); S2<=R1+R2+R3+R4; END logica; Programação realizada para o bloco da função criticamente amortecido LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.STD_LOGIC_UNSIGNED.all; ENTITY proj3 IS PORT ( V1 clock reset switch3 S3 ); END proj3; : IN : IN : IN : IN : BUFFER ARCHITECTURE logica of proj3 is SIGNAL C1 : SIGNAL C3 : SIGNAL C5 : SIGNAL C7 : SIGNAL R1 : SIGNAL R2 : SIGNAL R3 : SIGNAL R4 : INTEGER RANGE 0 TO 4095; STD_LOGIC := '0'; STD_LOGIC := '0'; STD_LOGIC := '0'; INTEGER RANGE 0 TO 4095 INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; INTEGER; BEGIN PROCESS (clock, reset, switch3) VARIABLE D1 : INTEGER; BEGIN IF (reset='1') or (switch3='0') THEN D1 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D1 := V1; END IF; C1 <= D1; 48 END PROCESS; PROCESS (clock, reset, switch3) VARIABLE D2 : INTEGER; BEGIN IF (reset='1') or (switch3='0') THEN D2 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D2 := C1; END IF; C3 <= D2; END PROCESS; PROCESS (clock, reset, switch3) VARIABLE D3 : INTEGER; BEGIN IF (reset='1') or (switch3='0') THEN D3 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D3 := S3; END IF; C5 <= D3; END PROCESS; PROCESS (clock, reset, switch3) VARIABLE D4 : INTEGER; BEGIN IF (reset='1') or (switch3='0') THEN D4 := 0; ELSIF clock'EVENT AND (clock='1') AND (clock'LAST_VALUE='0') THEN D4 := C5; END IF; C7 <= D4; END PROCESS; R1<=(369*C1/10000); R2<=(302*C3/10000); R3<=(14820*C5/10000); R4<=(-5488*C7/10000); S3<=R1+R2+R3+R4; END logica; Programação realizada para o bloco concentrador dos sinais de saída LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.STD_LOGIC_UNSIGNED.all; ENTITY proj4 IS 49 PORT ( ENT1 ENT2 ENT3 SWITCH SFINAL ); END proj4; : IN INTEGER RANGE 0 TO 4095; : IN INTEGER RANGE 0 TO 4095; : IN INTEGER RANGE 0 TO 4095; : IN INTEGER RANGE 0 TO 3; : OUT INTEGER RANGE 0 TO 4095 ARCHITECTURE logica of proj4 is BEGIN PROCESS(SWITCH, ENT1, ENT2, ENT3) BEGIN CASE SWITCH IS WHEN 1 => SFINAL <= ENT1; WHEN 2 => SFINAL <= ENT2; WHEN 3 => SFINAL <= ENT3; WHEN OTHERS => SFINAL <= 0; END CASE; END PROCESS; END logica; Programação realizada para o bloco dos Switches que define as funções préprogramadas. LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.STD_LOGIC_UNSIGNED.all; entity cod is port ( IN1 IN2 IN3 : in STD_LOGIC; : in STD_LOGIC; : in STD_LOGIC; SAIDA : out INTEGER RANGE 0 TO 3 ); end cod; architecture FUNC of cod is begin SAIDA <= 3 WHEN IN3 = '1' ELSE 2 WHEN IN2 = '1' ELSE 1 WHEN IN1 = '1' ELSE 0; end FUNC;

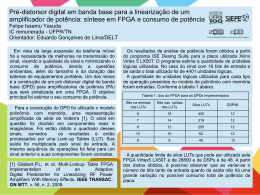

Download