CRONOGRAMA DA DISCIPLINA DE MICROELETRÔNICA EE (4458-G) www.ee.pucrs.br/~vargas/Disciplinas/Microeletronica-EE(4458G-04) Prof. Dr. Fabian Vargas [email protected] G1 = 0,16(P1 + P2 + P3 + P4 + P5) + 0,2(TrabFinal) 1 EE141 Bibliografia (Livros): “Digital Integrated Circuits: a design perspective”, Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic. 2nd edition. “Principles of CMOS VLSI Design: A Systems Perspective”, Neil Weste, Kamran Eshraghian. Addison Wesley Publishing Company. “Microeletrônica – Volume 2”, Adel S. Sedra, Kenneth C. Smith. Makron Books do Brasil Ltda. 1995. (Ver Cap. 1.3: Circuitos Digitais MOS, 563-644; Anexo A: Tecnologia de Fabricação de Circuitos Integrados, 760-742.) 2 EE141 Bibliografia (Sites): http://www-vlsi.stanford.edu:80/group/chips_micropro.html (Microprocessors Through the Ages) http://micro.magnet.fsu.edu/chipshots/index.html (Chip Shots Gallery) http://micro.magnet.fsu.edu/micro/gallery/chips/chipshots.html (Chip Shots Gallery) http://www.intel.com/community/oregon/hightech/history/intel/tech_advances.htm#micron (INTEL in your Community) http://micro.magnet.fsu.edu/electromag/java/transistor/index.html (CMOS Fabrication Process & Design Rules) http://www.cse.nd.edu/courses/cse462/www/lectures/L05_Fabrication.pdf (CMOS Fabrication Process & Design Rules) http://jas.eng.buffalo.edu/education/fab/invFab/index.html (CMOS Inverter Fabrication Process) 3 EE141 The Transistor Revolution First transistor Bell Labs, 1948 4 EE141 The First Integrated Circuits Bipolar logic 1960’s ECL 3-input Gate Motorola 1966 5 EE141 Intel 4004 Micro-Processor 1971 1000 transistors 1 MHz operation 6 EE141 Intel Pentium (IV) microprocessor 7 EE141 Moore’s Law In 1965, Gordon Moore noted that the number transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months 8 EE141 1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975 LOG2 OF THE NUMBER OF COMPONENTS PER INTEGRATED FUNCTION Moore’s Law EE141 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Electronics, April 19, 1965. 9 Evolution in Complexity 10 EE141 Transistor Counts 1 Billion Transistors K 1,000,000 100,000 10,000 1,000 i486 i386 80286 100 10 Pentium® III Pentium® II Pentium® Pro Pentium® 8086 Source: Intel 1 1975 1980 1985 1990 1995 2000 2005 2010 Projected EE141 Courtesy, Intel 11 Moore’s law in Microprocessors Transistors (MT) 1000 2X growth in 1.96 years! 100 10 486 1 P6 Pentium® proc 386 286 0.1 8086 8080 8008 4004 8085 Transistors on Lead Microprocessors double every 2 years 0.01 0.001 1970 EE141 1980 1990 Year Courtesy, Intel 2000 2010 12 Die Size Growth Die size (mm) 100 10 8080 8008 4004 1 1970 8086 8085 1980 286 386 P6 Pentium ® proc 486 ~7% growth per year ~2X growth in 10 years 1990 Year 2000 2010 Die size grows by 14% to satisfy Moore’s Law EE141 Courtesy, Intel 13 Frequency Frequency (Mhz) 10000 Doubles every 2 years 1000 100 486 10 8085 1 0.1 1970 8086 286 P6 Pentium ® proc 386 8080 8008 4004 1980 1990 Year 2000 2010 Lead Microprocessors frequency doubles every 2 years EE141 Courtesy, Intel 14 Power Dissipation Power (Watts) 100 P6 Pentium ® proc 10 8086 286 1 8008 4004 486 386 8085 8080 0.1 1971 1974 1978 1985 1992 2000 Year Lead Microprocessors power continues to increase EE141 Courtesy, Intel 15 Power will be a major problem 100000 18KW 5KW 1.5KW 500W Power (Watts) 10000 1000 100 Pentium® proc 286 486 8086 10 386 8085 8080 8008 1 4004 0.1 1971 1974 1978 1985 1992 2000 2004 2008 Year Power delivery and dissipation will be prohibitive EE141 Courtesy, Intel 16 Power density Power Density (W/cm2) 10000 1000 100 Rocket Nozzle Nuclear Reactor 8086 10 4004 Hot Plate P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year Power density too high to keep junctions at low temp EE141 Courtesy, Intel 17 Not Only Microprocessors Cell Phone Small Signal RF Digital Cellular Market (Phones Shipped) Power RF Power Management 1996 1997 1998 1999 2000 Units 48M 86M 162M 260M 435M Analog Baseband Digital Baseband (DSP + MCU) (data from Texas Instruments) 18 EE141 10,000 10,000,000 100,000 100,000,000 Logic Tr./Chip Tr./Staff Month. 1,000 1,000,000 10,000 10,000,000 100 100,000 Productivity (K) Trans./Staff - Mo. Complexity Logic Transistor per Chip (M) Productivity Trends 1,000 1,000,000 58%/Yr. compounded Complexity growth rate 10 10,000 100 100,000 1,0001 10 10,000 x 0.1 100 xx 0.01 10 xx x 1 1,000 21%/Yr. compound Productivity growth rate x x 0.1 100 0.01 10 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 1981 0.001 1 Source: Sematech Complexity outpaces design productivity EE141 Courtesy, ITRS Roadmap 19 Why Scaling? Technology shrinks by 0.7/generation With scaling, every generation can integrate 2x more functions per chip; chip cost does not increase significantly Cost of a function decreases by 2x But … How to design chips with more and more functions? Design engineering population does not double every two years… Hence, a need for more efficient design methods Exploit different levels of abstraction 20 EE141 Design Abstraction Levels SYSTEM MODULE + GATE CIRCUIT DEVICE G S n+ D n+ 21 EE141 Design Metrics How to evaluate performance of a digital circuit (gate, block, …)? Cost Reliability Scalability Speed (delay, operating frequency) Power dissipation Energy to perform a function 22 EE141 Cost of Integrated Circuits NRE (non-recurrent engineering) costs design time and effort, mask generation one-time cost factor Recurrent costs silicon processing, packaging, test proportional to volume proportional to chip area 23 EE141 NRE Cost is Increasing 24 EE141 Die Cost Single die Wafer Going up to 12” (30cm) From http://www.amd.com EE141 25 Cost per Transistor cost: ¢-per-transistor 1 0.1 Fabrication capital cost per transistor (Moore’s law) 0.01 0.001 0.0001 0.00001 0.000001 0.0000001 1982 1985 1988 1991 1994 1997 2000 2003 2006 2009 26 EE141 2012 Yield No. of good chips per wafer Y 100% T otalnumber of chips per wafer Wafercost Die cost Dies per wafer Die yield wafer diameter/22 wafer diameter Dies per wafer die area 2 die area Simplified Form Complete Form 27 EE141 Defects defectsper unit area die area die yield 1 is approximately 2 28 EE141 Some Examples (1994) Chip Metal Line layers width Wafer cost Def./ Area Dies/ Yield cm2 mm2 wafer Die cost 386DX 2 0.90 $900 1.0 43 360 71% $4 486 DX2 3 0.80 $1200 1.0 81 181 54% $12 Power PC 601 4 0.80 $1700 1.3 121 115 28% $53 HP PA 7100 3 0.80 $1300 1.0 196 66 27% $73 DEC Alpha 3 0.70 $1500 1.2 234 53 19% $149 Super Sparc 3 0.70 $1700 1.6 256 48 13% $272 Pentium 3 0.80 $1500 1.5 296 40 9% $417 29 EE141 Exercícios: 1) A cada nova geração, as pastilhas de circuitos de circuitos integrados DRAM têm significantemente aumentado. No entanto, o rendimento do processo destes circuitos tem permanecido aproximadamente o mesmo (43% a 48%). A tabela a seguir mostra alguns dados estatísticos referentes à produção de memórias DRAMs entre 1980 e 1992. Ano Capacidade (KBytes) Área da Pastilha (cm2) Diâmetro do Wafer (pol) Rendimento do Processo (%) 1980 64 0,16 5 48 1983 256 0,24 5 46 1985 1024 0,42 6 45 1989 4096 0,65 6 43 1992 16384 0,97 8 48 a) Dado o aumento de área da pastilha de memórias DRAM, qual o parâmetro que deve ser melhorado para se manter o mesmo rendimento? b) Qual é o melhoramento calculado para aquele parâmetro entre 1980 e 1992? EE141 30 Respostas para a questão (b): 1980: 1983: 1985: 1989: 1992: 5,61 3,95 2,33 1,61 0,91 2) Qual é o custo aproximado de uma pastilha de R4000 no wafer mostado à esquerda na Fig. 1? Assuma que o wafer de 6 polegadas custa US$750,00 e que a densidade de defeito é 2/cm2. Use o número de pastilhas indicado nesta figura. Resp.: USD 47,64. 3) Mesmo exercício que o anterior, mas utilizando o wafer da direita (R3000). Resp.: USD 8,76. 31 EE141 Fig. 1. Fotografia de um wafer de 6 polegadas contendo microprocessadores MIPS R4000 (esquerda) e um wafer de 6 polegadas contendo microprocessadores MIPS R3000 (direita). O número de pastilhas do R3000 no wafer da direita, para um rendimento de 100%, é 210. Cada pastilha mede 0,8 x 0,9cm2 e contem cerca de 125.000 transistores. O número de pastilhas do R4000 no wafer da esquerda, para um rendimento de 100%, é de 59. O tamanho da pastilha é 1,5 x 1,1cm2 e cada pastilha contem cerca de 1,3 milhão de transistores. Alguns dos chips do R3000 colocados nas bordas do wafer não serão utilizados; eles foram incluídos porque é mais fácil para se criar as máscaras para imprimir o circuito no silício. Os retângulos "vazios" em ambos wafers contém circuitos de teste usados para rapidamente se testar o wafer. O wafer do MIPS R4000 tem quatro circuitos de teste adicionais nas bordas. 32 EE141 3) Se se considerar as demais variáveis como constantes, qual é a relação approximada entre o custo e a área da pastilha? Resp.: die cost f (die area)3 33 EE141 Concepção de Circuitos Integrados Transistor Materiais Semicondutores Elétron Átomo de Silício • Grande estabilidade física e química em temperatura ambiente • 4 elétrons na órbita externa: valência 4 • Permite uma obtenção “natural” do SiO2 - óxido de silício Núcleo Neutron Próton Materiais Semicondutores Cristal de Silício Si Si Si Si Si Si Si Si Monocristal: Silício Monocristalino - estrutura regular e homogênea - ligações covalentes - material quimicamente estável Em estado puro (intrínsico): - mal condutor a temperatura ambiente - isolante a baixas temperaturas Aumento da temperatura: - provoca quebra das ligações - um elétron livre provoca a formação de uma lacuna - ocorre a geração de pares elétrons-buracos Materiais Semicondutores Mobilidade dos elétrons Mobilidade dos buracos µn µp OBS: Cerca de 3 vezes para o silício e 30 vezes para o AsGa Resistividade: capacidade de um material veicular corrente depende: - concentração de portadores (que por sua vez, depende: temperatura, dopagem) - mobilidade dos portadores no material Dopantes: átomos com excesso de elétrons ou de lacunas dopantes do tipo P: falta de elétrons (receptor de é, pFET) dopantes do tipo N: excesso de elétrons (doador de é, nFET) ex.: boro (3A) ex.: fósforo (5A) Materiais Semicondutores Ver Tabelas Periódicas em: http://educar.sc.usp.br/quimica/tabela.html http://profmokeur.ca/quimicap/ Transistor MOS Estruturas MOS Metal Óxido de Silício SiO2 Semicondutor -> (Germânio ou Silício Monocristalino) Silício Policristalino -> CONDUTOR Óxido de Silício SiO2 -> ISOLANTE Silício Monocristalino -> SEMICONDUTOR Transistor MOS Silício Policristalino N Óxido de Silício SiO2 N Corte transversal Silício Monocristalino P “Difusão N” Substrato P Vista de topo N Poli Transistor MOS (nFET) Grade Fonte corte canal N Dreno “Difusão N” N P Substrato P Contato planta baixa N nFET Transistor MOS (nFET) Gate = 0 V Fonte N canal “aberto” (OFF) Dreno N P Fonte Gate = VCC N “Difusão N” canal “fechado” (ON) Dreno N nFET P Transistor MOS (pFET) Gate = VCC Fonte P canal “aberto” (OFF) Dreno P N Well Gate = 0 V Fonte P P “Difusão P” canal “fechado” (ON) Dreno P N Well pFET P

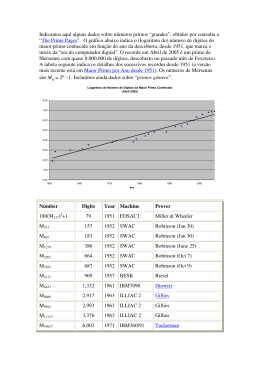

Baixar