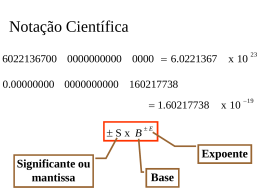

Parte 1: Organização de Computadores 4. Representação dos números e aritmética em computadores Texto base: capítulo 8 Computer Organization and Architecture W. Stallings IC - UFF Unidade Lógica e Aritmética Parte do processador que realiza as operações lógicas e aritméticas Função das outras unidades é trazer dados para serem processados pela ULA e obter resultados em retorno Operações aritméticas: números inteiros e reais (“ponto fixo” e “ponto flutuante”) IC - UFF ULA: entradas e saídas unidade de controle flags ULA registros IC - UFF registros Sistemas numéricos Sistema decimal Sistema binário Conversão entre bases Notação hexadecimal Notação octal IC - UFF Representação dos inteiros Se fossem só os números positivos, a representação seria imediata exemplo: com 8 bits IC - UFF 5110 = 001100112 23710 = 111011012 A = an-1 ... a1a0 = n 1 i 2 ai i0 Sinal e magnitude (1) Bit mais à esquerda: se 0, número positivo se 1, número negativo Exemplo: (com 8 bits) IC - UFF + 27 = 00011011 - 27 = 10011011 Sinal e magnitude (2) Problemas: consideração sobre sinal e magnitude nas operações de adição e subtração duas representações para o 0: IC - UFF +010 = 000000002 -010 = 100000002 Complemento a 2 (1) Resolve os dois problemas anteriores uma única representação para o 0 fácil de implementar a aritmética Regra simples IC - UFF +310 = 0112 complemento booleano: 1002 soma 1 ao BmS (LSB): 1012 = -310 Complemento a 2 (2) Exemplo: IC - UFF +3 = 011 +2 = 010 +1 = 001 +0 = 000 -1 = 111 -2 = 110 -3 = 101 -4 = 100 Faixa dos números inteiros Para 3 bits -4 -3 ... 0 ... +2 +3 Para n bits -2n-1 IC - UFF ... 0 ... 2n-1-1 Soma e subtração com C2 S = a - b = a + (-b) basta somador! IC - UFF OF = bit de overflow SW = chave multiplexadora E o somador? Soma de dois bits bi ai ci+1 IC - UFF realização? si ci E o somador? Soma de dois bits realização si ai bi ci ai bi ci ai bi ci ai bi ci ci 1 bi ci ai bi ai ci IC - UFF E o somador? Soma de dois bits Construção modular: somador de 3 bits b2 a2 c3 IC - UFF b1 a1 b0 a0 s2 s1 s0 c0 E o somador? Soma de dois bits Construção modular Carry lookahead IC - UFF evita propagação do sinal através de todos os estágios e Multiplicação é mais complexa que soma e subtração: Divisão é ainda mais complexa: se um dos números é negativo, multiplicação direta não resolve! números negativos dão trabalho! Mesmo h/w pode ser usado IC - UFF Representando números reais Números fracionários exemplo: 27,7510 = 11011,112 notação em “ponto fixo” problema: números muito grandes e muito pequenos Notação científica: IC - UFF 2.743.000.000.000 = 2,743 1012 0,000000000002743 = 2,743 10-12 Notação ponto flutuante Uso do mesmo método em binário M2 E, com Formato típico: comparação rápida 0 1 sinal sinal: ou mantissa M expoente E expoente IC - UFF 8 9 31 mantissa Expoente e mantissa Expoente: uso da notação “polarizada” (biased): C2 não é adequada 000000002 representa número mais negativo 111111112 representa número mais positivo polarização +127 (IEEE 754) IC - UFF -1 -110 + 12710 = 12610 = 011111102 +1 +110 + 12710 = 12810 = 100000002 Mantissa normalizada: 0,1bbb...b bit mais à esquerda é sempre 1 (implícito) Exemplo de ponto flutuante N = -0,7510 = -0,112 = -1,12 2-1 Representação geral (-1)S (1 + Mantissa) 2(Expoente - 127) (-1)1 (1 + 0,10...02) 2(126 - 127) formato em precisão simples 31 30 29 28 27 26 25 24 23 22 21 ... 0 1 0 1 1 1 1 1 1 0 1 0 ... 0 S IC - UFF Expoente Mantissa Faixa dos números reais Inteiros representáveis -231 231 -1 0 Reais representáveis OVF negativo -(1-2 ) 2 -24 128 IC - UFF Números reais negativos -0,5 2 -127 UDF negativo UDF positivo 0 Números reais positivos 0,5 2 -127 OVF positivo (1-2 ) 2 -24 128 PF: alguns detalhes (1) Número de valores representados neste formato é (praticamente) 232 Números mais espaçados na reta dos reais (mas não igualmente espaçados!) Precisão simples e dupla IC - UFF E: 8 bits 11 bits M: 23 bits 52 bits PF: alguns detalhes (2) Padrão IEEE 754 Precisão simples Expoente Mantissa 0 0 0 diferente de 0 1 a 254 qualquer coisa 255 0 255 diferente de 0 Precisão dupla Expoente Mantissa 0 0 diferente de 0 1 a 2046 qualquer coisa 2047 0 2047 diferente de 0 Associatividade: x + (y + z) = (x + y) + z ? IC - UFF -1,5E38 + (1,5E38 + 1,0) = 0,0 (-1,5E38 + 1,5E38) + 1,0 = 1,0 Objeto representado 0 nº não normalizado nº ponto flutuante NéN Aritmética em ponto flutuante Para a soma e a subtração é necessário que ambos os operandos tenham o mesmo expoente A multiplicação e a divisão são mais diretas Vejamos: y x y IC - UFF x y ( xM B E E yM ) B x y ( xM y M ) B x E y E E Precisão Arredondamento adequado exige bits extras no hardware Padrão IEEE 754 adiciona bits para os cálculos intermediários (e.g., guard e round) Exemplo: 2,56100 + 2,34102 2,3400 + 0,0256 2,3656 IC - UFF 2,37102 + 2,34 0,02 2,36 2,36102 Leitura suplementar Capítulo 4 Arithmetic for Computers Computer Organization & Design D.A. Paterson e J.L. Hennessy Ed. Morgan Kaufmann IC - UFF Trabalho Padrão IEEE 754 Estudar o pb de PF do Pentium IC - UFF

Baixar