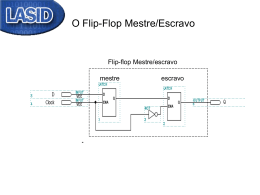

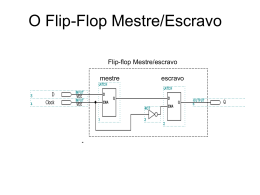

FACULDADE DE ENGENHARIA, ARQUITETURA E URBANISMO CURSO: Engenharia Elétrica e Engenharia de Computação. DISCIPLINA: Circuitos Lógicos 4a Série de Exercícios - Resolução Flip-flops e Dispositivos Correlatos Exercício 1. Considerando que inicialmente Q 0 , aplique as formas de onda x e y, mostradas na figura abaixo às entradas SET e CLEAR de um latch NAND e determine as Exercício 5.1 formas de onda das saídas Q e Q . Exercício 2. Aplique as formas de onda mostradas abaixo em um flip-flop S-C disparado por borda positiva (mostrado na figura abaixo), e determine a forma de onda da saída Q . Repita o procedimento para o flip-flop S-C disparado por borda negativa (visto na página seguinte). Considere inicialmente Q 0 . Exercício 5.9 mod FEAU - FACULDADE DE ENGENHARIA, ARQUITETURA E URBANISMO Avenida Shishima Hifumi, 2911 - Bairro Urbanova -CEP 12244-000 - São José dos Campos-SP Tel: (12) 3947 1006 4ta. Série Resolução 2 Prof. José Ricardo Abalde Guede Exercício 3. (a) Mostre como um flip-flop J-K pode operar como um flip-flop do tipo T (comuta de estado a cada pulso de clock). Em seguida, aplique um sinal de clock de 10 kHz na entrada de clock, CLK, desse flip-flop, e determine a forma de onda da saída Q . (b) Conecte a saída Q desse flip-flop à entrada de clock de um segundo flip-flop J-K que também possui J K 1 . Determine a freqüência do sinal na saída desse flip-flop. Exercício 5.11 (a) Um flip-flop J-K pode operar como um flip-flop do tipo T ao conectar as entradas J e K permanentemente em estado ALTO. A saída Q será uma onda quadrada de freqüência 5 kHz. (b) A saída Q do segundo flip-flop será uma onda quadrada de freqüência 2,5 kHz. Exercício 4. As formas de onda mostradas na figura abaixo são aplicadas em dois flip-flops diferentes: (a) J-K disparado por borda positiva (b) J-K disparado por borda negativa Desenhe a forma de onda da saída Q para cada um desses flip-flops, considerando inicialmente Q 0 . Considere que cada flip-flop tenha tH = 0. Exercício 5.12 4ta. Série Resolução 3 Prof. José Ricardo Abalde Guede Exercício 5. (a) Aplique as formas de onda S e CLK mostradas na figura abaixo às entradas D e CLK respectivamente de um flip-flop D disparado na borda positiva. Em seguida, determine a forma de onda da saída Q . (b) Repita o procedimento usando a forma de onda C , mostrada na figura, na entrada D do Exercício 5.14 flip-flop. Exercício 6. Um flip-flop D disparado por borda pode ser configurado para operar como um flipflop tipo T conforme é mostrado na figura abaixo. Considere inicialmente Q 0 e determine a forma de onda da saída Q . Exercício 5.15 Flip-flop D configurado como um flip-flop tipo T. A saída Q será uma onda quadrada de 500 Hz. 4ta. Série Resolução 4 Prof. José Ricardo Abalde Guede Exercício 7. Aplique as formas de onda CLK , PRE e CLR , mostradas na figura abaixo, em um flip-flop D disparado por borda positiva com entradas assíncronas ativas em nível BAIXO. Considere que a entrada D seja mantida em nível ALTO e que a saída Q esteja inicialmente Exercício 5.21 em nível ALTO. Desenhe a forma de onda resultante na saída Q . Formas de ondas mostrando como um flip-flop J-K com clock responde às entradas assíncronas. Exercício 8. Compare a operação do latch D com o flip-flop D disparado por borda negativa aplicando as formas de onda, mostradas na figura abaixo, em cada um e determinando as Exercício 5.18 formas de onda das saídas Q . 4ta. Série Resolução 5 Prof. José Ricardo Abalde Guede Exercício 9. Aplique as formas de onda mostradas na figura abaixo no flip-flop D disparado na borda negativa do clock e que tem entradas assíncronas ativas em nível BAIXO. Considere que a entrada D seja mantida em nível BAIXO e que a saída Q esteja inicialmente em nível ALTO. Desenhe a forma de onda resultante na saída Q . Exercício 5.22 Exercício 10. Veja o circuito mostrado na figura a seguir e responda às seguintes perguntas: (a) Se o contador começar em 000, qual será o valor da contagem após 13 pulsos de clock? E após 99 pulsos? E após 256 pulsos? (b) Se o contador começar em 100, qual será o valor da contagem após 13 pulsos? E após 99 pulsos E após 256 pulsos? (c) Conecte um quarto flip-flop J-K ( X 3 ) a esse contador e desenhe o diagrama de transição de estados para esse contador de 4 bits. Se a freqüência de clock de entrada for de 80 MHz, como será a forma de onda em X 3 ? Exercício 5.30 4ta. Série Resolução 6 Prof. José Ricardo Abalde Guede Flip-flops J-K conectados para formar um contador binário de três bits (módulo 8). (a) Um contador de 3 flip-flops tem módulo 8. Após 13 pulsos o valor da contagem será 510 = 1012 . Após 99 pulsos será 310 = 1012 e após 256 pulsos será 010 = 0002. 13 | 8 . 99 | 8 . 256 | 8 . 5 1 19 11 16 32 3 0 (b) Começando em 410 = 1002 , o valor final da contagem será 110 = 0012 após 13 pulsos. Após 99 pulsos será 710 = 1112 , e após 256 pulsos 410 = 1002. (c) Diagrama de estados de um contador de 4 flip-flops, módulo 16. Considerando que o módulo do contador de 4 flip-flops é 24 = 16 a freqüência de saída no último flip-flops será 500 kHz. frequencia saída 4ta. Série Resolução frequenciaentrada 80 MHz 500 kHz módulo 16 7 Prof. José Ricardo Abalde Guede Exercício 11. (a) Quantos flip-flops são necessários para construir um contador binário que conte de 0 a 1023? (b) Determine a freqüência na saída do ultimo flip-flop desse contador para uma freqüência de clock de entrada de 2 MHz. (c) Qual é o modulo do contador? (d) Se o contador começar em zero, que valor de contagem ele apresentará após 2060 pulsos? Exercício 5.33 (a) São necessários 10 flip-flops para construir um contador binário que conte de 0 a 1023. 2 N 1 1023, 2 N 1024 N 10 (b) Considerando que o módulo do contador de 10 flip-flops é 210 = 1024 a freqüência de saída no último flip-flops será 1953 Hz. frequencia saída frequenciaentrada 2 MHz 1953 Hz módulo 1024 (c) O módulo do contador de 10 flip-flops é 210 = 1024. (d) A cada 1024 pulsos o contador volta ao estado inicial 0. Logo após 2060 o estado final será 1210 = 00000011002. 2060 | 1024 . 12 2 Exercício 12. Veja as formas de onda mostradas na figura abaixo para monoestáveis com uma duração do pulso de 2,0 ms. Mude a duração do pulso do monoestável para 0,5 ms e determine a saída Q para os dois tipos de monoestaveis. Em seguida, repita o procedimento usando um pulso de duração de 1,5 ms. Exercício 5.39 |--------|--------|------|-------|--------|--------|-------|-------|--------|---0 1 2 3 4 5 6 7 8 9 t [ms] com tp = 0,5 ms 4ta. Série Resolução 8 Prof. José Ricardo Abalde Guede com tp = 1,5 ms Exercício 13. A figura abaixo mostra três monoestáveis não-redisparáveis conectados em cascata produzindo em seqüência três pulsos de saída. Observe o “1” em frente ao pulso dentro do símbolo de cada monoestável indicando a operação não-redisparável. Desenhe o diagrama de tempo mostrando a relação entre o pulso de entrada e as três saídas dos monoestaveis. Considere um pulso de entrada com duração de 10ms. Exercício 5.40 4ta. Série Resolução 9 Prof. José Ricardo Abalde Guede Exercício 14. Veja o símbolo lógico para o monoestável não-redisparável 74121 mostrado na figura abaixo. (a) Que condições de entrada são necessárias para o monoestável ser disparado por um sinal na entrada B ? (b) Que condições de entrada são necessárias para o monoestável ser disparado por um sinal na entrada A1 ? Exercício 5.42 Símbolos lógicos para o monoestável não-redisparável 74121; (a) Tradicional (b) IEEE/ANSI. (a) As entradas A1 ou A2 devem estar em nível BAIXO e o pulso de disparo por borda positiva PGT deve ocorrer em B. (b) As entradas B e A2 devem estar em nível ALTO e o pulso de disparo por borda positiva PGT deve ocorrer em A1. Exercício 15. Considere o circuito mostrado na figura abaixo. Inicialmente, todos os FFs estão no estado 0 (saídas em nível BAIXO). A operação do circuito começa com um pulso momentâneo aplicado na entrada PRESET dos FFs X e Y . Determine as formas de onda em A , B , C , X , Y , Z e W para 20 ciclos de pulsos de clock após o pulso de inicio. Apresente todas as suas suposições. Exercício 5.44 4ta. Série Resolução 10 Prof. José Ricardo Abalde Guede Com o pulso inicial nas entradas assíncronas PRESET dos flip-flops X e Y suas saídas vão para 1 (nível ALTO, flip-flops setados). Com X = Y = 1 a saída Z da porta OR é nível ALTO tal que o flip-flop A trabalho no modo de comutação (J = K = 1). Os 3 flip-flops A , B e C operam como um contador de 3-bits nos 6 primeiros pulsos de entrada. No sexto pulso de entrada B = C = 1 e a saída W da porta NAND vai para nível BAIXO. Isto leva X para nível BAIXO (dispara o flip-flop X que tem sua entrada DX = 0) e Y permanece em nível ALTO (flip-flop Y tem na sua entrada DY = 1). Com Y = 1, Z permanece em nível ALTO e os 3 flip-flops A , B e C continuam a operar como um contador. Após um ciclo completo (módulo 8, ou seja após 8 pulsos) B = C = 1, a saída W = 0 novamente e X = Y = Z 0. 4ta. Série Resolução 11 Prof. José Ricardo Abalde Guede Exercício 16. Projete um oscilador astável com 555 para gerar uma onda aproximadamente quadrada de 40 kHz. O capacitor C deve ser de 500 pF ou maior. Exercício 5.46 CI temporizador 555 usado como um multivibrador astável. 1 25 s t1 t2 12,5 s . f Para termos uma onda quadrada RA RB , por exemplo RA 1 K e RB 10 K . t1 0,693 ( RB ) (C ) 12,5 s 0,693 10 K (C ) C 1800 pF T 0,693 ( RA 2 RB ) (C ) 0,693 (1 K 20 K) (1800 pF ) 26,2 s 1 T 26,2 s f 38 KHz e onda quase quadrada. T f 40 KHz T ***&*** 4ta. Série Resolução 12 Prof. José Ricardo Abalde Guede

Baixar

![Apresentacao 2 - Medidor de Velocidade de Motores[1]](http://s1.livrozilla.com/store/data/000245414_1-380a51a995ea01731d251d44e39198b1-260x520.png)