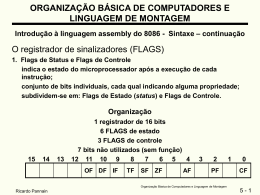

Sistemas Multiprocessados Curso Sistemas Multiprocessados Prof. Helano de Sousa Castro Departamento de Teleinformática/DETI [email protected] Programa da disciplina 1. Evolução das arquiteturas de computadores: aspectos históricos, computador pessoal, bases numéricas 2. Arquitetura de microprocessador: arquitetura interna, modo de endereçamento de memória real e protegido, paginação 3. Modos de endereçamento 4. Programação assembly 5. Arquitetura do processador 8086: especificações técnicas, pinagem, geração de clock (8284), demultiplexação e buferização de barramentos, temporização dos barramentos, estados de espera (WAIT), modo máximo e mínimo 6. Interface de memória: dispositivos de memória, endereçamento, interface de memória do 8086. 7. Interface básica de Entrada/Saída: introdução a interface E/S, decodificação de endereços de portas, Interface Programável de Periféricos (8255), Interface Programável de Teclado/Vídeo (8279), Temporizador Programável (8254), Interface Programável de Comunicação, Conversor analógico-digital e digital-analógico. 8. Interrupções: atendimento de interrupções, interrupção de hardware, expandindo a estrutura de interrupção, Controlador Programável de Interrupção (8259A) 9. Acesso Direto à Memória (DMA): operação do DMA, Controlador de DMA 8237 Avaliação Três avaliações escritas (50%) Projeto de final de disciplina (50%) Projeto Hardware: placa com processador 8086; memória RAM de (no mínimo) 16KB ememória EPROM de mesmo tamanho; interface serial (8251); interface paralela (8255); contador/temporizador programável (8253); controlador de interrupções (8259A); Diferencial: controlador de teclado/video (8275); controlador de DMA (8257); Software: drivers para dispositivos acima; aplicação demonstrado operacionalidade do hardware. Pipelining Organização de memória 1 Organização de memória 2 Organização de memória 3 Registros Registro de flags Registro de Flags Registros de uso geral EAX: Acumulador : Referenciado como EAX, AX, AL ou AH. – Usado em instruções mult, div, etc. – Usado para armazenar um offset. EBX: Base Index : – Usado para armazenar o offset do ponteiro de dados. Registros de uso geral (cont) ECX: Count : – Usado para armazenar contagem em algumas instruções, REP e LOOP. – Usado para armazenar o offset de um ponteiro de dados. EDX: Data : – Usado para armazenar uma parte do resultado de mult, e de operando para div. – Usado para armazenar o offset de um ponteiro de dados. Registros de uso geral EBP: Base Pointer : – EDI: Destination Index : – Armazena o ponteiro base para transferências de dados em memória Armazena o ponteiro base do destino para instruções string. ESI: Source Index : – Armazena o ponteiro destino da origem para instruções string. Registros de propósito especial EIP: Instruction Pointer : – Aponta para a próxima instrução no segmento de código. – 16-bits (IP) no modo real e 32-bits no modo protegido. ESP: Stack Pointer : – Usado em operações na pilha e intruções call and ret. EFlags C (Carry) : P (Parity) : Armazena o “vai 1” após operações de adição ou “empresta 1” após operações de Também indica condições de erro. 0 para números ímpares e 1 para pares. Característica obsoleta do 80x86. A (Auxiliary Carry) : Flag altamente especializado usado em instruções DAA e DAS após instruções de adição e subtração em BCD. Flags (cont) Z (Zero) : S (Sign) : 1 se o resultado de uma instrução lógica ou aritmética for 0. 1se o sinal do resultado de uma instrução aritmética ou lógica for negativo. T (Trap) : Habilita Trap. O microprocessador interrompe o fluxo de instruções de acordo com condições indicada pelos registros de controle e debug. Flags (cont) I (Interrupt) : D (Direction) : Controla a operação do pino de interrupção INTR (Interrupt request). Se1, interrupções são habilitadas. Modificado pelas instruções STI e CLI. Seleciona o modo de incremento ou decremento para o registro DI e/ou SI durante instruções string. Se1, os registros são automaticamente decrementados. Modificado pelas instruções STD e CLD. O (Overflow) : Modificado (set) para instruções de adição e subtração Registros de Segmento CS (Code Segment) : No modo real, especifica o inicio de um segmento de memória de 64KB. No modo protegido, seleciona um descritor de segmento. O segmento de código é limitado a 64KB no 808680286 e 4 GB a partir do 386. DS (Data Segment) : Similar ao CS exceto que esse segmento armazena dados. ES (Extra Segment) : Data segmento de dados usado por algumas instruções string para armazenar dados. Registros de segmento (cont) SS (Stack Segment) : Similar a CS exceto que armazena a pilha. ESP e EBP armazenam os offsets nesse segmento. FS and GS : 80386 e acima. Permitem definir outros segmentos de memória Mapeamento de endereços Segmentação Pinagem do 8086 Característica elétrica do 8086 Sinais do 8086 AD7-AD0 Barramento de sinais multiplexados de dados e endereços (byte menos significativo). O sinal ALE indica presença de endereços no barramento. Os pinos ficam em estado de alta impedância durante um hold acknowledge AD15-AD8 Barramento de sinais multiplexados de dados e endereços (byte mais significativo). O sinal ALE indica presença de endereços no barramento. Os pinos ficam em estado de alta impedância durante um hold acknowledge AD19/S6-A16/S3 Barramento de sinais multiplexados de endereços (4 bits mais significativos) e status. O bit indicativo de status S6 sempre permanece em zero; o bit S5 indica a condição dos bits de flag IF. S3 e S4 podem ser usados para endereçar 4 bancos de memória separados de 1MB, decodificando-os como A20 e A21. Os pinos ficam em estado de alta impedância durante um hold acknowledge S4 S3 Função 0 0 segmento extra 0 1 segmento de pilha 1 0 segmento de código ou nenhum segmento 1 1 segmento de dados RD Sinal de saída. Sempre que for zero, indica que o 8086 está pronto para efetuar uma leitura de memória ou E/S . O pino fica em estado de alta impedância durante um hold acknowledge. READY Sinal de entrada. Usado para introduzir estados de espera (WAIT) na temporização do processador. Se for colocado em nível 0, o 8086 entra em estados de espera e permanece ocioso (idle). Se colocado em nível 1, não tem nenhum efeito na operação do processador. INTR Sinal de entrada que indica um pedido de interrupção (Interrupt request). Quando mantido em 1, se IF=1, o 8086 entra em um ciclo de reconhecimento de interrupção (Interrupt acknowledge, INTA torna-se ativo) após a instrução atual ser concluída. Conhecida por interrupção mascarável por poder ser não reconhecida através da colocação de IF em 0. TEST Sinal de entrada que é testado pela instrução WAIT. Se TEST = 0, a instrução WAIT funciona como um NOP; sefor 1, a instrução WAIT espera que TEST torne-se 0. NMI Sinal de entrada para indicar um pedido de interrupção não mascarável (non-maskable interrupt). Similar a INTR exceto que o status do flag IF não é testado. Se NMI é ativado, a interrupção usa o vetor 2. RESET Sinal de entrada usado para resetar o 8086 por um mínimo de 4 períodos de clock. O processador começa a executar a partir da posição de memória FFFF0H e interrupções mascaráveis são desabilitadas através da colocação de IF em 0. CLK Sinal de entrada, fornece o sinal de temporização básico para o microprocessador. O sinal de clock deve ter um duty cycle de 33% de forma a garantir temporizações internas necessárias. Vcc Sinal de entrada, fornece a tensão de +5V +/-10%, para o processador. GND Conexão de terra para retorno da fonte de potência. O 8086 tem 2 pinos de terra e AMBOS devem ser aterrados. MN/MX Sinal de entrada, seleciona o modo de operação mínimo ou máximo do processador. Se o mínimo é requerido, o pino deve ser conectado a +5V. BHE/S7 Sinal de entrada, fornece a tensão de +5V +/-10%, para o processador. Pinos do 8086 no modo mínimo M/IO Sinal de saída usado para indica que o processador irá efetuar acesso à memoria ou à dispositivos de entrada/saída.Quando 1, indica que o barramento de endereços contém um endereço válido de memória. O pino fica em estado de alta impedância durante um hold acknowledge. WR Sinal de saída, é usado como strobe que indica que o 8086 está enviando dados para memória ou Entrada/Saída. Durante o tempo que WR está em lógica 0, o barramento de dados contém dados válidos para memória ou E/S. O pino fica em estado de alta impedância durante um hold acknowledge. INTA Interrup Acknowledge. Sinal de saída, indica que o 8086 irá responder a um pedido de interrupção feito no pino INTR. ALE Address Latch Enable. Sinal de saída, indica que o barramento multiplexado endereços/dados contém informação de endereços. O endereços pode se referir a memória ou número da porta de E/S. Usado normalmente junto com um Latch para demultiplexar o barramento enderços/dados. Este pino não flutua com HOLDA. DT/R Sinal de saída, indica que o processador está transmitindo ou recebendo no/do barramento de dados. Esse sinal é usado para habilitar buffers externos de dados. DEN Data bus enable. Sinal de saída, usado para ativar buffer externos de dados. HOLD Sinal de entrada, usada para solicitar DMA (Direct Memory Access), Acesso Direto à Memória. Se HOLD=1, o processador para de executar o programa e coloca seus barramentos em alta impedância. Se HOLD=0 o processador executa normalmente. HLDA Hold Acknowledge. Sinal de saída, indica que o 8086 entrou em um estado de HOLD. SS0 Linha de status (saída), é equivalente ao pino S0 no modo operação máximo. Este sinal, combinado com M/IO e DT/R , é usado para decodificar a função do ciclo de barramento atual. Pinos no modo máximo S2, S1, S0 Bits de status (saída) indicam a função corrente do ciclo de barramento. Estes sinais são, normalmente, decodificados usando-se o controlador de barramento 8288. R1/GT1 e RO/GT0 Request/Grant. Usados para pedidos de DMA no modo de operação máximo. Essas linhas são bi-direcionais, e são usadas tanto para pedido como para concessão de operação de DMA. Configuração no modo máximo S2 S1 S2 Função 0 0 0 INT ACK 0 0 1 I/O Read 0 1 0 I/O Write 0 1 1 Halt 1 0 0 Opcode Fetch 1 0 1 Memory Read 1 1 0 MemoryWrite 1 1 1 Passivo Funções do barramento de controle geradas pelo barramento de controle (8288) usando S2, S1 e S0 LOCK Sinal de saída, é usado para “travar” periféricos. Este pino é ativado usando o prefixo LOCK: em qualquer instrução.Hold Acknowledge. QS1 e QS2 Sinais de status (saída), mostram o status da fila interna de instruções. Esses pinos são fornecidos para acesso ao coprocessador numérico QS1 QS2 Função 0 0 Fila está inativa 0 1 Primeiro byte de um opcode 1 0 Fila vazia 1 1 Byte subsequente de um opcode Status da Fila interna de instruções Diagrama de bloco do 8284 Gerador de Clock 8284A AEN1 e AEN2 Pinos Address Enable (entradas) são fornecidos para habilitar os sinais de Ready, RDY1 e RDY2, respectivamente, usados para causar ciclos de WAIT. RDY1 e RDY2 (entradas) Pinos de entrada usados em conjunção com AEN1 e AEN2 para causar ciclos de WAIT no ASYNC A entrada de seleção de sincronização de ready seleciona um ou dois estágios de sincronização para as entradas RDY1 e RDY2. Possui resistor de pull-up interno. READY Sinal de saída para ser conectado no pino READY do 8086. Este sinal está sincronizado com RDY1 e RDY2. X1 e X2 Pinos para conexão do oscilador de cristal externo, usado como fonte de temporização para todos os tempos no 8484. Sua frequência deve ser 3 vezes maior que o valor desejado para CLK. F/C Entrada frequency/crystal select seleciona a fonte de clock do 8284. Se o pino é mantido em 1, um clock externo é fornecido pela entrada EFI; se mantido em 0, o oscilador de cristal interno fornece o sinal de temporização. EFI A entrada External frequency input é usada quando o pino F/C é colocado em 1, caso em que ele fornece a temporização. Sua frequência deve ser 3 vezes maior que o valor desejado para CLK. CLK Pino de saída do clock para o 8086 e outros componentes do sistema. Sua freqüência é 1/3 da freqüência do cristal ou de EFI, e tem um ciclo de trabalho de 33%, requerido pelo processador. PCLK A saída peripheral clock tem 1/6 da freqüência do cristal ou de EFI, e tem ciclo de trabalho de 50%. PCLK fornece sinal de clock para equipamento periférico do sistema. OSC A saída oscilator tem um nível de sinal TTL que é da mesma freqüência que o cristal ou EFI. OSC fornece uma entrada EFI para outros geradores de clock 8284 em sistemas multiprocessadores. Contanto que se tenha um cristal conectado a X1 e X2, sempre esta saída fornecerá um clock, mesmo se, mesmo se F/C estiver em alto. RES Reset é uma entrada ativo baixo para o 8284. Este pino é normalmente conectado a uma rede RC que fornece poweron reset. RESET Saída conectado ao pino de RESET do 8086. CSYNC A entrada clock synchronization é usada sempre que a entrada EFI fornecer a sincronização em sistemas multiprocessadores. Se o oscilador de cristal interno for usado, essa entrada deve ser aterrada. GND Pino de terra. Vcc Deve ser ligado a uma fonte de +5V, +/- 10%. Clock do processador Circuito de reset e clock Latching 8288 Temporização no 8086 8086 usa memória e E/S em períodos chamados de ciclos de barra (ou barramento) Cada ciclo corresponde a 4 períodos de clock (estados T) Se f = 5 MHz, T = 200ns e ciclo = 800ns Velocidade de Leitura ou escrita máxima Ciclo de barra T1 – ALE, DT/R, M/IO, Endereços T2 – RD ou RD, DEN Se ciclo de escrita -> DATA OUT Se ciclo de leitura -> barramento A/D em tri-state Ready – amostrado no final de T2 T3 – Fornecido para dar tempo para memória acessar dado Se o ciclo for de leitura (READ) o dado é amostrado no fim de T3 T4 – Sinais desativados. Preparação para o próximo ciclo Subida de WR Cálculo para tempo de acesso da memória Considerando processador a 5MHz -> T = 200 ns Ciclo de leitura = 3 X T = 3 X 200 ns + 600 ns (Access Time) Deve-se considera o retardo introduzido por: ALE (TCLAV) = 110 ns Access Time = 600 ns – 110 ns = 490 ns Data Setup (TDVCL) = 30 ns Access Time = 490 ns – 30 ns = 460 ns OBS: Incluir retardo de 40 ns (propagação portas) Access Time = 420 ns

Download