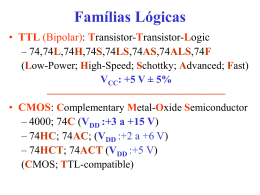

Relação entre Mintermos, Maxtermos e Tabela Verdade Mapas de Karnaugh Mapas de Karnaugh Mapas de Karnaugh e Tabela Verdade Simplificação usando MK: observações importantes • A combinação de células que for selecionada deve incluir deve incluir todos as células pelo menos uma vez (uma célula pode aparecer em mais de uma combinação) • As combinações devem ser selecionadas com a finalidade de incluir o maior número possível de células, de tal modo que todas as células sejam incluídas pelo menor número de combinações • O número de células que deve ser considerado como grupo deve ser uma potência de 2. Implicantes Primos Denominação das combinações (produtos). Pode acontecer que não seja necessário usar todos os primos implicantes p1 = m2 + m3 p2 = m8 + m12 p3 = m2 + m10 p4 = m8 + m10 f = p1 + p2 + p3 ou f = p 1 + p2 + p4 OBS: Uso de p1 é obrigatório, caso contrário m3 não seria incluído Determinando a expressão SOP mínima do MK • Agrupe as células que contenham ‘1s”. Cada grupo de células contendo 1’s cria um termo produto composto de todas as variáveis que ocorram somente em uma forma (complementada ou não). • Determine o termo produto mínimo para cada grupo Algorítmo que leva à expressão mínima para uma função lógica Passo 1 • Assinalar e considerar como implicante primo essencial qualquer célula que não possa ser combinada com nenhuma outra Passo 1 Passo 2 • Identificar as células que podem ser combinadas com uma única outra célula somente de uma maneira. Assinalar estas combinações. Células que podem ser combinadas em grupos de dois, de mais de uma maneira, são deixados temporariamente de lado Passo 2 Passo 3 • Identificar células que podem ser combinadas com três outras células somente de uma maneira. Se as quatro células de tais combinações ainda não estiverem incluídas em grupos de dois, assinalar a combinação de quatro. Novamente, uma célula que pode ser combinada em um grupo de quatro de mais de uma maneira deve ser deixada temporariamente de lado. Passo 3 Passo 4 • Repetir o processo para grupos de oito, etc. Passo 5 • Se, encerrado o processo, ainda restarem algumas células não inclusas em grupamentos, elas podem ser combinadas umas com as outras ou com células já incluídas em outras grupamentos, lembrando que a intenção é de obter o menor número de grupamentos possível. Determinando a expressão SOP mínima do MK • Cada grupo de células contendo 1’s cria um termo produto composto de todas as variáveis que ocorram somente em uma forma (complementada ou não). Passo 5 Para um mapa com 3 variáveis: a) um grupo com 1 célula produz um termo produto com 3 variáveis b) um grupo com 2 células produz um termo produto com 2 variáveis c)Um grupo com 4 células produz um termo com 1 variável d) um grupo de 8 células produz um valor de 1para a expressão Para um mapa com 4 variáveis: a) um grupo com 1 célula produz um termo produto com 4 variáveis b) um grupo com 2 células produz um termo produto com 2 variáveis c) um grupo com 4 células produz um termo com 1 variável d) um grupo de 8 células produz um termo com uma variável e) um grupo de 16 células produz um valor de 1 para a expressão Famílias Lógicas e Magem de Ruído Famílias Lógicas • RTL – Resistor-Transistor Logic • DTL – Diode-Transistor Logic • ECL – Emmiter-Coupled Logic Uso da família lógica e grau de obsolescência Nomeclatura Complementary Metal–Oxide– Semiconductor logic • Consume praticamente nenhuma potência no estado estático (sem mudanças nas entradas) • Porta CMOS consome quase nenhuma corrente quando no estado 0 ou 1 • Quando porta chaveia corrente é consumida da fonte para carregar a capacitância de saída da porta (consumo dessa corrente varia com frequência de operação – tipicamente controlada pelo clock de operação) • Funcionamento em altas frequências • VLSI Ruído Ruído Eletromagnético Os ruídos são sinais eletromagnéticos que podem interferir em outros sinais propagados (sinal principal) no meio onde o ruído trafega, modificando o sinal principal. Margem de ruído Ruídos podem se compor com os sinais aplicados na entrada (ou saída) de uma porta lógica e, dependendo de sua intensidade, podem modificar o nível de tensão na entrada (ou saída) de uma porta, e portando seu nível lógico. Porta lõgica Porta lõgica Low Noise Margin (LNM) = VILmax - VOLmax High Noise Margin (HNM) = VOHmin - VIHmin Níveis de tensão na entrada e saída de uma porta TTL VIH VOH VOL VIL VOL(max) Porta lõgica V IL(max) Porta lõgica VOH(min) V IH(min) Low Noise Margin (LNM) = VILmax - VOLmax High Noise Margin (HNM) = VOHmin - VIHmin Margem de Ruído numa porta TTL Low Noise Margin (LNM) = VILmax - VOLmax High Noise Margin (HNM) = VOHmin - VIHmin Níveis de tensão na entrada e saída de uma porta CMOS operando em 5V CMOS operam em faixas de tensões maiores que TTL CMOS operam em faixas de tensões maiores que TTL Comparação margem de ruído CMOS e TTL Famílias Lógicas Famílias Lógicas Descrição de TTL, ECL, CMOS e Glue Logic Descrição de TTL, ECL, CMOS e Glue Logic Descrição de TTL, ECL, CMOS e Glue Logic Descrição de TTL, ECL, CMOS e Glue Logic Glossário

Baixar