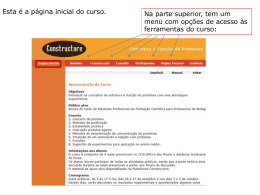

Brazil-IP Program Angelo Brito, Camila Nunes, Marcelo Albuquerque, Maria Cireno, Maryane Brasilino, Rafael Barbosa, Rafael Lima, Raphael Almeida Universidade Federal de Pernambuco Roteiro Introdução/Motivação ipPROCESS Arquitetura do DMA Controller Arquitetura do McBSP Plataforma Unificada Problemas e Soluções Resultados Trabalhos Futuros Introdução Projeto desenvolvido pelo Brazil-IP (UFPE). Brazil IP é um esforço colaborativo de Universidades Brasileiras para formação e treinamento de projetistas de Circuito Integrado. Utliza metodologias próprias ou adapta metodologias com sucesso em software para hardware. BRAZIL-IP Introdução IP – Intellectual Property Implementação de um projeto em hardware em uma linguagem específica para esse objetivo (Verilog, VHDL, …); O ideal é ser reusável e se adaptar a vários dispositivos de hardware. O processo de desenvolvimento do IP Core é dividido em etapas baseado no ipPROCESS Motivação Com o desenvolvimento de tais projetos, o Brasil se torna capaz de desenvolver novas tecnologias de Circuito Integrado, tanto por formar mão de obra qualificada, quanto através de um banco de módulos desenvolvidos em território brasileiro e, consequentemente, mais acessíveis. ipPROCESS Baseaso na metodologia do ipPROCESS – Rigoroso processo de engenharia – Metodologias de Engenharia de Software + Padrões de desenvolvimento de IP-Cores – Define a tarefa de projetar um IP-core como um conjunto de atividades – Já utilizado no desenvimento de outros IP-Cores ipPROCESS Concepção e Arquitetura – Elicitação de requisitos – Especificação de Casos de Uso – Análise – Definição da Arquitetura ipPROCESS Projeto – Implementação do testbench – Módulos de Verificação – Módulos RTL ipPROCESS Verificação – Verificação de RTL – Geração de entradas iguais para o modelo funcional e para o modelo RTL ipPROCESS Prototipação em FPGA Ambiente DMA Controller Processador - DSP Program Acess/ Cache Controlle r Internal Program Memory DMA Dispositivos Data Acess Controller HPI Internal Data Memory Arquitetura do DMA Controller Avalon RPL CL CT GEL BR CI RPE SP GEE CE Arquitetura do DMA Controller Dividido em módulos menores devido a sua complexidade Cada módulo implementado em diferentes níveis de abstração(Funcional e RTL) Arquitetura do McBSP Arquitetura do McBSP McBSP (Multichannel Buffered Serial Port) – – – – Porta Serial de alta velocidade bufferizada; Funciona associada a DSPs da família C6000; Padrão da Texas Intruments; Aplicação em Processamento Digital de Sinais: Áudio, Vídeo, Processamento de voz, etc. Exemplo de áudio: McBSP RTL Plataforma Unificada A comunicação dos módulos da plataforma é feita através de um barramento AVALON: Plataforma Unificada O objtetivo do projeto é ao unificar os módulos, possibilitar a transmissão e recepção de dados seriais em alta velocidade sem a intervenção da CPU. Uma possibilidade de aplicação é fazer um Karaokê, onde a Porta Serial (McBSP) faz as transferências seriais bit a bit, lendo do microfone e escrevendo na interface de som, enquanto o DMA lê e na memória e lê e escreve na Porta Serial para realizar as transferências de dados. Resultados TRANSMISSÃO RECEPÇÃO Resultados Resultados do McBSP Elementos lógicos Portas lógicas (gates) Área da FPGA ocupada Número de linhas do RTL Módulos 4.630 158.902 14% 10181 linhas 8 Resultados Resultados do DMA Módulos de Referência 11 Estruturas de Verificação 11 Módulos RTL 7 Módulos Validados 5 Resultados Implementações em diferentes níveis de abstração: – Nível Funcional – Nível RTL Implementação do Modelo de Referência antes do Modelo RTL: – Domínio das funcionalidades: Problemas e Soluções A inexperiência dos integrantes iniciais do projeto ao fazer o testbench Trabalhos Futuros Objetivo: Atingir o memso nível de excelência dos projetos passados 8051 MP4 Robô Jubinha “Se enxerguei mais longe, foi porque me apoiei sobre os ombros de gigantes.” Isaac Newton Trabalhos Futuros http://www.youtube.com/watch?v=t9j4tASZVWM Dúvidas OBRIGADO!

Download