Microeletrônica Germano Maioli Penello http://www.lee.eng.uerj.br/~germano/Microeletronica%20_%202015-1.html Sala 5145 (sala 17 do laboratorio de engenharia elétrica) Aula 10 1 Revisão Já analisamos as seguintes camadas de fabricação: n-well, metal1, metal2, via1 e overglass. A partir de agora, analisaremos as camadas ativa, n-select, p-select, poly1, silicide e contato. 2 Novas camadas As camadas ativa, n-select, p-select, poly são usadas para criar o canal-n e o canal-p dos MOSFETs e assim a camada de metal pode fazer um contato com o substrato ou o poço. As camadas n-select e p-select definem onde implantar os átomos p e n. As camadas ativa e as camadas select são sempre usadas em conjunto. 3 MOSFET fabricação http://jas.eng.buffalo.edu/education/fab/NMOS/nmos.html Camada ativa A camada ativa define onde abrir o FOX (field oxide) definindo a área ativa. O FOX separa dispositivos uns dos outros. As áreas ativas são isoladas uma das otras pelo FOX (existe conexão entre os dispositivos pelo substrato ou pelo poço, mas o FOX tenta fazer com que essa comunicação seja mínima). 5 p-select e n-select As máscaras p-select e n-select sempre acompanham a camada ativa. Elas são usadas para dopar a região ativa com átomos p ou n (Quais átomos são usados para dopagem p ou n?). 6 p-select e n-select As máscaras p-select e n-select sempre acompanham a camada ativa. Elas são usadas para dopar a região ativa com átomos p ou n (Quais átomos são usados para dopagem p ou n?). Como é a seção de corte dessas máscaras? 7 p-select e n-select As máscaras p-select e n-select sempre acompanham a camada ativa. Elas são usadas para dopar a região ativa com átomos p ou n (Quais átomos são usados para dopagem p ou n?). 8 p-select e n-select As máscaras p-select e n-select sempre acompanham a camada ativa. Elas são usadas para dopar a região ativa com átomos p ou n (Quais átomos são usados para dopagem p ou n?). 9 p-select e n-select As máscaras p-select e n-select sempre acompanham a camada ativa. Elas são usadas para dopar a região ativa com átomos p ou n (Quais átomos são usados para dopagem p ou n?). As máscaras n-select e p-select são sempre maiores que as regiões ativas para evitar problemas de desalinhamento. O FOX protege o substrato da implantação. 10 Camada poly O nome poly vem de polisilício (polysilicon), um material policristalino de silício. Desenhar um poly em cima de uma região ativa forma um MOSFET. O número de MOSFETs em um processamento é facilmente obtido contando-se quantas vezes o poly cruza a região ativa. O poly forma a porta (gate) do MOSFET. O dreno e a fonte são formadas pela implantação n. 11 Camada poly O MOSFET visto desta maneira é um dispositivo de 3 terminais; não estamos abordando a conexão ao corpo (body) do MOSFET. Com a conexão de corpo, o MOSFET passa a ser um dispositivo de 4 terminais. 12 Porta auto alinhada GOX A área abaixo do poly não é dopada. A camada poly protege a região abaixo dela da implantação dos dopantes A fina camada de óxido entre o poly e a região ativa é chamada de óxido de porta - gate oxide (GOX) O dreno e fonte ficam auto alinhados com a deposição do poly da porta. 13 Exemplo de erros Implantação dos dopantes (camadas select) antes da deposição do poly. O que aconteceria caso o poly e as camadas ativas fiquem ligeiramente desalinhadas? Esta é a vantagem da camada poly auto alinhada. 14 Fio de poly As camadas de poly podem ser usadas como fios da mesma forma que a camada de metal. Note que a camada poly fica em cima da camada FOX. A resistência de folha da camada poly é ~200 W/quadrado. Compare com a camada metálica! A capacitância ao substrato também é maior (veja tabela da aula passada). Portanto, o atraso do fio poly é maior do que o do metal. Para reduzir a resistência de folha, uma camada silicide é depositada sobre o MOSFET. O silicide e o poly formam o chamdado polycide. Silicide – mistura de silício com um elemento mais eletropositivo (por ex., tungstênio) 15 Resistências típicas Com silicide as resistências são bem menores! Note que o silicide é sempre colocado acima do poly! Se for colocado abaixo, cria um contato retificador (contato de barreira Schottky). 16 Bloco de silicide Resistências da tabela do slide anterior (com e sem Silicide): 17 Bloco de silicide Resistências da tabela do slide anterior (com e sem Silicide): ns ps 18 Fluxo de processo CMOS Genérico O pad oxide serve apenas como uma camada para o crescimento do silicon nitride que evita o crescimento de óxido. O fotorresiste é depositado e o com fotolitografia protegemos a região de interesse e definimos a região aberta no FOX. 19 Fluxo de processo CMOS Genérico A área não protegida é corroída e forma trincheiras rasas. 20 Fluxo de processo CMOS Genérico As trincheiras são preenchidas com SiO2 formando a região de campo (regiões do FOX). Este tipo de isolamento entre os dispositivos é chamada de isolamento de trincheira rasa (STI – shallow trench isolation) 21 Fluxo de processo CMOS Genérico Duas regiões de implante são feitas para ajustar a tensão de gatilho. As implantações p e n são feitas em etapas distintas. 22 Fluxo de processo CMOS Genérico Polisilício já depositado e o padrão já definido (porta do MOSFET) em cima do óxido de porta. 23 Fluxo de processo CMOS Genérico Implantação rasa para formar o lightly doped drain (LDD) do MOSFET. Serve para prevenir o campo elétrico perto da fonte e dreno ficar muito alto (veremos detalhes mais adiante no curso). O poly serve como uma máscara para as implantações. 24 Fluxo de processo CMOS Genérico Óxido espaçador nas laterais do poly e depois implante n+ e p+ que cria as áreas de dreno e fonte e também dopa o poly para que ele conduza. 25 Fluxo de processo CMOS Genérico A última etapa é o silicide para reduzir a resistência de folha do poly e das regiões n+ e p+. 26 FEOL e BEOL As sequências feitas nos últimos slides são chamadas de FEOL (front-end of the line) As sequências feitas após isso (camadas de metais e vias) são chamadas de BEOL (back-end of the line)) 27 Etapas de processo damasceno As sequências 1) Trincheira 2) Cobrir a trincheira com óxido 3) Polir o substrato para que o topo seja plano É chamado de processo damasceno. Foi este o processo que apresentamos aqui. O processo damasceno é utilizado mais comumente nas camadas metálicas. Trincheiras são formadas nos isolantes, cobre é depositado e o topo do wafer é polido para ficar plano 28 MOSFET fabricação Este processamento do aplicativo é exatamente o mesmo que acabamos de mostrar? http://jas.eng.buffalo.edu/education/fab/NMOS/nmos.html

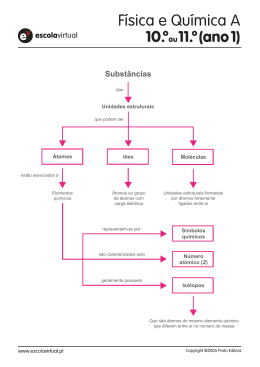

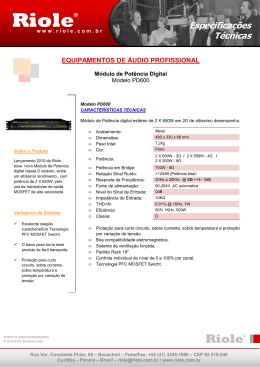

Download